# **REFRESH CONTROLLER FOR 4K DYNAMIC RANDOM ACCESS MEMORIES**

- Ideal for use in 2107A, 2107B Systems

- Simplifies System Design

- Reduces Package Count

- Standard 22-Pin DIP

- Adjustable Refresh Timina Oscillator

- 6-Bit Address Multiplexer

- 6-Bit Refresh Address Counter

- Refresh Cycle Controller

The Intel® 3222 is a refresh controller for dynamic RAMs requiring refresh of up to 6 input addresses (or 4K bits for 64 x 64 organization). The device contains an accurate refresh timer (whose frequency can be set by an external resistor and capacitor), plus all necessary control and I/O circuitry to provide for the refresh requirements of dynamic RAMs. The chip's high performance makes it especially suitable for use with high speed N-channel RAMs like the Intel® 2107B. The 3222 is well suited for asynchronous dynamic memory systems.

The 3222 operates from a single +5 volt power supply and is specified for operation over a 0°C to 75°C ambient temperature range. It is fabricated by means of Intel's highly reliable Schottky bipolar process.

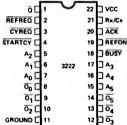

### **PIN CONFIGURATION**

#### **PIN NAMES**

| Ao - A5 | ADDRESS INPUTS | 00.05   | ADDRESS OUTPUTS       |

|---------|----------------|---------|-----------------------|

| ACK     | ACKNOWLEDGE    | ā       | INTERNAL REFRESH      |

|         | OUTPUT         |         | REQUEST LATCH OUTPUT  |

| BUSY    | BUSY INPUT     | REFON   | REFRESH ON OUTPUT     |

| CYREO   | CYCLE REQUEST  | REFREQ  | REFRESH REQUEST INPUT |

|         | INPUT          | RxCx    | RC TIE POINT          |

|         |                | STARTCY | START CYCLE OUTPUT    |

|         |                | Vcc     | +5V SUPPLY            |

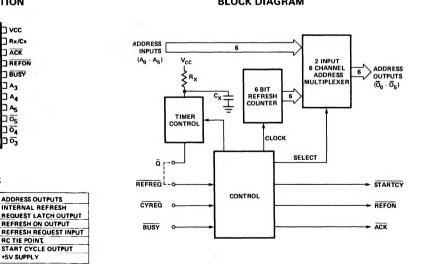

### **BLOCK DIAGRAM**

# **Absolute Maximum Ratings\***

| Temperature Under Bias                          |

|-------------------------------------------------|

| Storage Temperature                             |

| All Input, Output or Supply Voltages0.5V to +7V |

| All Input Voltages1.0V to +5.5V                 |

| Output Currents 100 mA                          |

| Power Dissipation 1 W                           |

### \*COMMENT

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

|                  | Limits                                                      |      |         |      |      |                                                   |  |

|------------------|-------------------------------------------------------------|------|---------|------|------|---------------------------------------------------|--|

| Symbol           | Parameter                                                   | Min. | Typ.[1] | Max. | Unit | Test Conditions                                   |  |

| I <sub>FB</sub>  | Input Load Current BUSY                                     |      | 0.40    | 1    | mA   | V <sub>IN</sub> = 0.45V                           |  |

| IFO              | Input Load Current All Other Inputs                         |      | 0.05    | 0.25 | mA   | V <sub>IN</sub> = 0.45V                           |  |

| I <sub>RB</sub>  | Input Leakage Current BUSY                                  |      | <1      | 50   | μΑ   | V <sub>IN</sub> = V <sub>CC</sub>                 |  |

| IRO              | Input Leakage Current All Other Inputs                      |      | <1      | 20   | μA   | V <sub>IN</sub> = 5.25V                           |  |

| VCLAMP           | Input Clamp Voltage                                         |      | -0.76   | -1   | V    | I <sub>C</sub> = -5.0mA                           |  |

| VIL              | Input "Low" Voltage                                         |      |         | 0.8  | V    |                                                   |  |

| VIH              | Input "High" Voltage                                        | 2.0  |         |      | V    |                                                   |  |

| lcc              | Power Supply Current                                        |      | 91      | 120  | mA   | V <sub>CC</sub> = 5.25V                           |  |

| I <sub>SC</sub>  | Output High Short Circuit Current                           |      | -48     | -70  | mA   | V <sub>OUT</sub> = 0V<br>V <sub>CC</sub> = 5.25V  |  |

| VOL              | Output Low Voltage                                          |      | 0.32    | 0.45 | V    | l <sub>OL</sub> = 5mA                             |  |

| V <sub>OH</sub>  | Output High Voltage $(\overline{O}_0 \cdot \overline{O}_5)$ | 2.6  | 3.1     |      | V    | I <sub>OH</sub> = -1mA<br>V <sub>CC</sub> = 4.75V |  |

| V <sub>OH1</sub> | Output High Voltage (All Other Outputs)                     |      | 3.0     |      | V    | I <sub>OH</sub> = -1mA<br>V <sub>CC</sub> = 4.75V |  |

# **D.C. Characteristics** All Limits Apply for $V_{CC}$ = +5.0V ±5%, T<sub>A</sub> = 0°C to +75°C.

Note 1: Typical values are for  $T_A = 25^{\circ}C$  and nominal power supply voltages.

# Capacitance<sup>[2]</sup>, $T_A = 25^{\circ}C$

|                           |                   | Limit | s (pF) |                          |  |

|---------------------------|-------------------|-------|--------|--------------------------|--|

| Symbol                    | Test              | Typ.  | Max.   | Conditions               |  |

| C <sub>IN</sub> (Address) | Input Capacitance | 5     | 10     | V <sub>bias</sub> = 2.0V |  |

| CIN (CYREQ)               | Input Capacitance | 6     | 10     | V <sub>CC</sub> = 0V     |  |

| CIN (BUSY)                | Input Capacitance | 20    | 30     | f = 1 MHz                |  |

Note 2: This parameter is periodically sampled and is not 100% tested.

| Symbol          | Parameter                            | Min. | Typ. <sup>1</sup> | Max. | Unit | Conditions                                                                                                                                                                                           |

|-----------------|--------------------------------------|------|-------------------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>AA</sub> | Address In to Address Out            |      | 7                 | 12   | ns   | BUSY = VIH                                                                                                                                                                                           |

| tBAM            | BUSY In to Address Out               |      | 21                | 28   | ns   |                                                                                                                                                                                                      |

| tBAR            | BUSY In to Counter Out               |      | 18                | 27   | ns   |                                                                                                                                                                                                      |

| t <sub>BK</sub> | BUSY In to ACK Out                   |      | 14                | 20   | ns   | $\overline{\text{REFREQ}} = V_{\text{IH}}, \overline{\text{CYREQ}} = V_{\text{IL}}$                                                                                                                  |

| t <sub>BR</sub> | BUSY In to REFON Out                 |      | 15                | 24   | ns   |                                                                                                                                                                                                      |

| t <sub>BS</sub> | BUSY In to STARTCY Out               | 4    | 7                 | 14   | ns   | CYREQ = VIL                                                                                                                                                                                          |

| tHOLD           | BUSY Hold Time                       | 50   |                   |      | ns   | External Delay between STARTCY and BUSY                                                                                                                                                              |

| tRH             | CYREQ or REFREQ Hold Time            | 0    |                   |      | ns   | External Delay after BUSY                                                                                                                                                                            |

| t <sub>RR</sub> | REFRED to REFON                      |      | 18                | 26   | ns   | $\label{eq:cyrel} \begin{array}{l} \hline CYREQ \text{ and } \overline{BUSY} = V_{IH}, \text{ No priority} \\ \hline contention between } \overline{REFREQ} \text{ and} \\ \hline CYREQ \end{array}$ |

| tRRC            | REFREQ to REFON                      |      | 33                | 45   | ns   | BUSY = V <sub>IH</sub>                                                                                                                                                                               |

| t <sub>RS</sub> | CYREQ or REFREQ In to<br>STARTCY Out | 9    | 14                | 21   | ns   | BUSY = V <sub>IH</sub>                                                                                                                                                                               |

| tSetup          | BUSY Setup Time                      | 120  |                   |      | ns   | BUSY = VIL During Refresh                                                                                                                                                                            |

**A.C. Characteristics** All Limits Apply for  $V_{CC}$  = +5.0V ±5%,  $T_A$  = 0°C to +75°C. Load = 1 TTL,  $C_L$  = 15pF. Conditions of Test: Input pulse amplitude: 3V, Input rise and fall times: 5ns between 1V and 2V. Measurements are made at 1.5V.

Note 1: Typical values are for  $T_A = 25^{\circ}C$  and nominal power supply voltages.

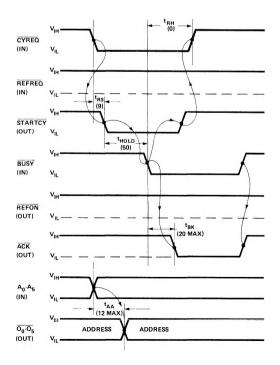

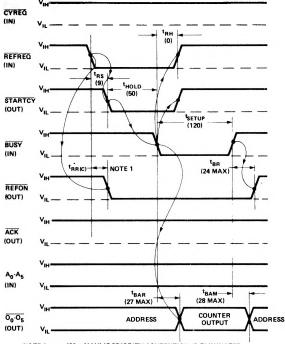

# A. SYSTEM MEMORY CYCLE WITH MEMORY NOT BUSY

## B. SYSTEM MEMORY CYCLE WITH MEMORY BUSY (FOLLOWING REFRESH CYCLE)

(Numbers in parentheses are minimum values in ns unless otherwise specified.)

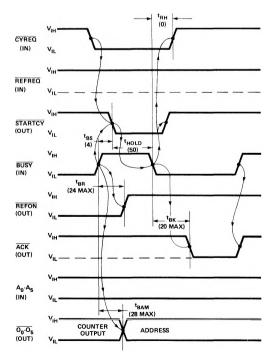

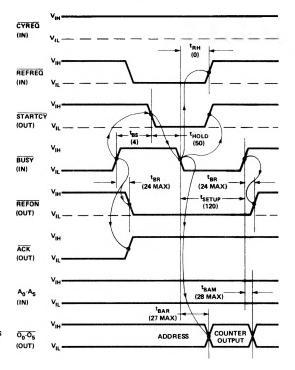

### C. REFRESH MEMORY CYCLE WITH MEMORY NOT BUSY

## D. REFRESH MEMORY CYCLE WITH MEMORY BUSY (FOLLOWING SYSTEM CYCLE)

(Numbers in parentheses are minimum values in ns unless otherwise specified.)

NOTE 1: TRR (26ns MAX) IF PRIORITY CONTENTION IS ELIMINATED; TRRC

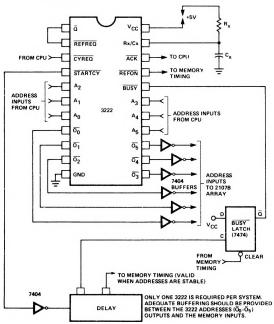

### E. TYPICAL APPLICATION OF 3222 REFRESH CONTROLLER IN A 2107B SYSTEM

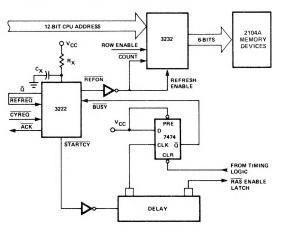

# F. USE OF 3222 FOR REFRESH TIMING AND CONTROL IN A 2104A SYSTEM

# 3222

### PIN NAMES AND FUNCTIONS

| Pin          | Pin                            | <b>–</b>                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| No.          | Name                           | Function                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1            | ā                              | Output of the internal Refresh Re-<br>quest latch. This pin may be con-<br>nected to the Refresh Request input<br>(REFREQ) directly for asynchro-<br>nous sequential mode refresh or<br>indirectly through control logic for<br>burst mode or synchronous mode<br>refresh (see text).                      |  |  |  |

| 2            | REFREQ                         | Refresh Request input (active when<br>low). The request is honored only if<br>the memory is <u>not</u> presently execut-<br>ing a cycle (BUSY high) and if a<br>system cycle request did not occur<br>first.                                                                                               |  |  |  |

| 3            | CYREQ                          | System Memory Cycle Request in-<br>put (active when low). The request<br>is honored only if the memory is not<br>presently executing a cycle (BUSY<br>high) and if a refresh request did not<br>occur first.                                                                                               |  |  |  |

| 4            | STARTCY                        | Output signal indicating to external<br>circuitry that a memory cycle<br>(system or refresh) is to begin. See<br>text for timing considerations for a<br>refresh cycle.                                                                                                                                    |  |  |  |

| 5-7<br>15-17 | A <sub>0</sub> -A <sub>5</sub> | Low order system address inputs. These addresses are multiplexed to the address output pins $(\overline{O}_0 - \overline{O}_5)$ during a system cycle.                                                                                                                                                     |  |  |  |

| 8-10         | ō₀-ō₅                          | Low order memory address outputs.<br>During a system cycle these outputs<br>give the low order $(A_0-A_5)$ address<br>of a memory access. During a<br>refresh cycle these outputs give the<br>refresh address (generated internal<br>to the 3222).                                                         |  |  |  |

| 11           | GROUND                         | Ground.                                                                                                                                                                                                                                                                                                    |  |  |  |

| 18           | BUSY                           | An externally generated signal<br>which the 3222 monitors to determ-<br>ine memory system status. If BUSY<br>is high the memory is not busy and a<br>system or refresh cycle may begin.<br>If BUSY is low the memory is being<br>accessed for a data I/O or refresh<br>cycle and no other cycle may begin. |  |  |  |

| 19           | REFON                          | The 3222 output which when low in-<br>dicates the memory system is either<br>ready to begin or is in a refresh cycle<br>(Refresh On).                                                                                                                                                                      |  |  |  |

| 20           | ACK                            | The 3222 output which when low in-<br>dicates the memory system is<br>either ready to begin or is in a<br>system cycle (system cycle request                                                                                                                                                               |  |  |  |

system cycle (system cycle request accepted and acknowledged).

| Pin<br>No. | Pin<br>Name | Function                                                                                                                                       |

|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 21         | RX/CX       | Connection point for the RC net-<br>work which determines the refresh<br>period for sequential refresh mode.<br>(See Refresh Control section). |

| 22         | Vcc         | +5 volt supply.                                                                                                                                |

## FUNCTIONAL DESCRIPTION

The Intel® 3222 performs the four basic functions of a refresh controller by:

- 1. Providing a refresh timing oscillator.

- 2. Generating six bit refresh addresses.

- 3. Multiplexing refresh and system addresses to the six low order address inputs  $(\overline{O}_0 \overline{O}_5)$ .

- 4. Providing control signals for both refresh and memory cycle accesses.

As shown in the pin configuration figure, the 3222 has as inputs the six low order ( $A_0$ - $A_5$ ) system addresses. These addresses are internally multiplexed with six internally generated refresh addresses. The output of these multiplexers provide the six low order addresses to the memory array.

The block diagram shows the four main circuit categories of the 3222. An explanation of the workings of each of these categories is given in the Device Operation section from a users point of view.

## **DEVICE OPERATION**

Operation of the Intel® 3222 Refresh Controller is most easily explained by considering five conditions presented by the three input control lines Cycle Request (CYREQ), Refresh Request (REFREQ), and System Busy (BUSY). These conditions are:

- 1. System memory cycle request memory not busy (BUSY = High)

- 2. System memory cycle request memory busy (BUSY =Low)

- 3. Refresh cycle request memory not busy (BUSY = High)

- Refresh cycle request memory busy (BUSY =Low)

- 5. Simultaneous system memory cycle and refresh cycle requests.

Condition 5 is actually a subset of the four previous conditions and is included for completeness.

As is implied in the five conditions, the response of the 3222 to both refresh and memory cycles is dependent on the state of the BUSY input. The BUSY signal is generated externally to the 3222 and, when low, defines the time when the memory is performing a cycle (refresh or memory access). It is important to assure that BUSY is low for the *entire* memory cycle time. Interference may occur in asynchronous memory systems if the BUSY input goes high prematurely. (An asynchronous memory cycle requests occur independent of each other.)

### System Memory Cycle Request — Memory Not Busy

This section details operation of the 3222 when the memory is not busy and a request for a system memory cycle is made (See Figure A for timing sequences). The request for a memory cycle is made by the CYREQ input going low. The Start Cycle output STARTCY goes low at  $t_{RS}$  after CYREQ. STARTCY is used for two purposes:

- 1. To set the external BUSY latch. (See Figure E.)

- 2. To initiate memory system timing (after appropriate delay).

The required delay time depends on system configuration and associated delay paths for both Chip Enable (2107B input signal) and system addresses.

The low going  $\overline{BUSY}$  input causes the internally generated Start Cycle output to go high and the Acknowledge output  $\overline{ACK}$  to go low (after  $t_{BK}$  time). The Acknowledge output confirms that the requested system memory cycle has been accepted by the 3222. Note that the cycle request input may be returned to the high state when the  $\overline{BUSY}$  input goes low. However, at the designer's discretion, the cycle request line may remain low until "just prior" to  $\overline{BUSY}$  returning high. (If  $\overline{BUSY}$  goes high before  $\overline{CYREQ}$  goes high, another memory access may inadvertently be started.)

When the memory is not busy and a cycle request has been made, the low order system address delay through the 3222 is  $t_{AA}$  nsec. When the 3222 is not busy, the low order system addresses (A<sub>0</sub>-A<sub>5</sub>) are gated through to the output ( $\overline{O}_0$ - $\overline{O}_5$ ) independent of any other input.

#### System Memory Cycle Request — Memory Busy

The major differences between a system memory cycle request when the system is busy and when it is not busy (as previously described) are:

- The Start Cycle output STARTCY does not go low until t<sub>BS</sub> after the rising edge of the BUSY input. (Even though the CYREQ input is low.)

- 2. Output addresses  $\overline{O}_0$ - $\overline{O}_5$  change at or before  $t_{AA}$  time if the previous cycle was a system cycle request and change at or before  $t_{BAM}$  if the previous cycle was a Refresh Cycle request. (Note that the longer delay is after a refresh cycle.) See Figure B for definition of terms.

Note that for a system memory cycle following a refresh cycle, the refresh on output REFON goes high at or before  $t_{BR}$  relative to BUSY going high. Since the Acknowledge output ACK can not go low until after  $t_{HOLD}$  there is no ambiguity between REFON and ACK. The memory is always defined as being in a refresh cycle, system cycle or no cycle.

### Refresh Cycle — Memory Not Busy

Operation of the 3222 for a refresh request with the memory not busy (see Figure C) is similar to a system cycle request under the same condition. A refresh cycle is initiated by the Refresh Request input (REFREQ) going low. This low going input causes both the Start Cycle output, STARTCY, and Refresh On output, REFON, to go low at t and tRRC (or tRR) time respectively. The low going edge of STARTCY is used to set the external BUSY latch low. As in the previous two cases, the BUSY input must remain low for the entire cycle required by the memory. As in the previous two cases, the low going BUSY drives the STARTCY output high.

### Refresh Cycle — Memory Busy

For this condition, it is assumed that the previous cycle was a system access cycle. Timing conditions for this operation are shown in Figure D. Here, the STARTCY input goes low t<sub>BS</sub> after BUSY returns high from the previous cycle. As before, REFON goes low t<sub>BR</sub> after BUSY goes high. After t<sub>HOLD</sub>, relative to STARTCY, BUSY again goes low and places the low order refresh addresses on the address outputs ( $\overline{O}_0$ - $\overline{O}_5$ ) after t<sub>BAR</sub> time. Internal refresh timing is performed in a manner identical to that described in Refresh Cycle-Memory Not Busy section.

### Simultaneous Refresh and Memory System Cycle Request

The simultaneous request for a refresh and memory system access is almost a certainty in asynchronous systems. It is, therefore, necessary to have circuitry in any refresh controller capable of resolving the attendent ambiguity with minimum additional delay. The Intel® 3222 Refresh Controller has just such a circuit. (All timing parameters specified for asynchronous operation assume that a refresh and memory system request can occur at the same time.) A latch internal to the 3222 decides which signal (CYREQ or REFREQ) it will accept if both occur simultaneously, and conditions the other control circuits appropriately. If a refresh cycle was accepted, REFON will go low at the appropriate time.

### **Refresh Control**

The 3222 controls both burst and distributed refresh modes. The burst refresh mode requires that REFREQ be generated externally to the 3222 since refresh is completed in 64 consecutive cycles every 2ms. A system requiring distributed refresh timing, however can be controlled either by the 3222 or by external circuitry. If refresh timing is to be controlled by the 3222 the output  $\overline{Q}$  is tied to the REFREQ input. Timing is controlled by an oscillator internal to the 3222. The desired refresh timing interval is determined by:

1.  $t_{REF} = .63 R_x C_x$

r Where:

- t<sub>REF</sub> = the total time between refreshes (e.g. 2msec) in msec.

- r = the number of rows to be refreshed on the memory device (for the 2107B r = 64).

- $R_x$  = external timing resistance in K $\Omega$  (3K to 10K)

- $C_x$  = external timing capacitance in  $\mu f$ . (0.005 $\mu f$  to 0.02 $\mu f$ )

The 3222's oscillator stability is guaranteed to be  $\pm 2\%$  for a given part and  $\pm 6\%$  from part to part, both over the ranges  $0^{\circ}C \leq T_A \leq 75^{\circ}C$  and  $V_{CC} = 5.0V \pm 5\%$ .

Figure F shows how the 3222 may be used to control refresh in a 2104A system.