# TRI-STATE QUAD D-TYPE BUS FLIP-FLOP

8T10

B,F,W PACKAGES

# DIGITAL 8000 SERIES TTL/MSI

## DESCRIPTION

The 8T10 is a high speed Quad D flip-flop with tri-state outputs for use in bus-organized systems. The high current sink capability permits up to 20 standard loads to be interconnected on a single bus. The outputs present a high impedance to the bus when disabled (Control Input "1") and active drive when enabled (Control Inputs "0").

All four D-type flip-flops operate from a common clock with data being transferred on the low-to-high transition of the pulse.

A common clear input resets all flip-flops upon application of a logic "1" level.

Data will be stored if either one or both inputs to the Input Disable NOR gate is a logic "1".

#### TRUTH TABLE

| D <sub>n</sub> | INDIS | IN <sub>DIS</sub> OUT <sub>DIS</sub> |                |  |  |  |  |

|----------------|-------|--------------------------------------|----------------|--|--|--|--|

| 0              | 0     | 0                                    | 0              |  |  |  |  |

| 1              | 0     | 0                                    | 1              |  |  |  |  |

| ×              | 1     | 0                                    | o <sub>n</sub> |  |  |  |  |

| ×              | x     | 1                                    | High Z         |  |  |  |  |

On refers to the output state before a clock pulse.

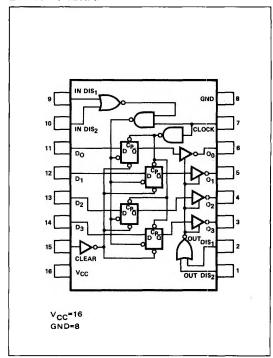

## LOGIC DIAGRAM

# ELECTRICAL CHARACTERISTICS (Over Recommended Operating Temperature And Voltage)

| CHARACTERISTICS        | LIMITS |      |      |       | TEST CONDITIONS |             |             |              |              |       |       |        |       |

|------------------------|--------|------|------|-------|-----------------|-------------|-------------|--------------|--------------|-------|-------|--------|-------|

|                        | MIN.   | TYP. | MAX. | UNITS | D <sub>n</sub>  | IN<br>DIS 1 | IN<br>DIS 2 | OUT<br>DIS 1 | OUT<br>DIS 2 | CLEAR | CLOCK | ООТРОТ | NOTES |

| "1" Output Voltage     | 2.4    | 3.0  |      | v     | 2.0V            | 0.8V        | 0.8V        | 0.8∨         | 0.8∨         | 0.8V  | Pulse | -5.2mA | 6     |

| "0" Output Voltage     |        |      | 0.4  | v     | 0.8V            | 0.8V        | 0.8V        | 0.8∨         | 0.8∨         | 0.8V  | Pulse | 32mA   | 7     |

| Output Leakage Current | -40    |      | +40  | μА    |                 | 0.8         | 0.8V        | +2.0V        | +2.0∨        | 0.8∨  | Pulse | +0.4V/ |       |

| (High Impedance State) |        |      |      |       |                 |             |             |              |              |       |       | +2.4V  |       |

| "1" Input Current      |        |      |      |       |                 |             |             |              |              |       |       |        |       |

| D <sub>n</sub> Inputs  | 1      |      | 40   | μΑ    | 4.5V            | 0.4∨        | 0.4V        | 0.4∨         | 0.4V         | 0.4V  |       |        |       |

| All Other Inputs       |        |      | 50   | μΑ    |                 | 4.5V        | 4.5V        | 4.5V         | 4.5V         | 4.5V  | 4.5V  |        |       |

| "0" Input Current      |        |      |      |       |                 |             |             |              |              |       |       |        |       |

| D <sub>n</sub> Inputs  | 100    |      | -3.2 | mA    | 0.4∨            |             |             |              |              |       |       |        |       |

| All Other Inputs       | 100    |      | -2.0 | mA    |                 | 0.4V        | 0.4∨        | 0.4∨         | 0.4V         | 0.4V  | 0.4V  |        |       |

| Input Voltage Rating   | +5.5V  |      |      |       | 10mA            | 10mA        | 10mA        | 10mA         | 10mA         | 10mA  | 10mA  |        |       |

<sup>0, + 1</sup> refers to the output state after a clock pulse.

$T_A = 25^{\circ} C$  and  $V_{CC} = 5.0 V$

| CHARACTERISTICS                                         | LIMITS |      |            |       | TEST CONDITIONS |             |             |              |      |       |       |        |         |

|---------------------------------------------------------|--------|------|------------|-------|-----------------|-------------|-------------|--------------|------|-------|-------|--------|---------|

|                                                         | MIN.   | TYP. | MAX.       | UNITS | Dn              | IN<br>DIS 1 | IN<br>DIS 2 | OUT<br>DIS 1 |      | CLEAR | CLOCK | ОЏТРОТ | NOTES   |

| Propagation Delay (t <sub>on</sub> , t <sub>off</sub> ) |        |      |            |       |                 |             |             |              |      |       |       |        |         |

| Clock to Output                                         |        | İ    |            |       |                 |             | ŀ           |              |      |       | 1     |        |         |

| C <sub>1</sub> = 30pf                                   |        | 18   | 25         | ns    |                 |             | Ì           | 1            |      |       |       | ļ      | 12      |

| C <mark>լ = 300</mark> pf                               |        | 24   | 35         | ns    |                 |             |             |              |      |       | 1     |        | 12      |

| Disable to Output                                       |        | ĺ    |            |       |                 |             |             | l            |      |       | İ     |        | ļ       |

| High Z to Logic 0, t <sub>pZL</sub>                     |        | ۱    |            |       |                 |             |             |              |      |       | 1     |        |         |

| State (C <sub>1</sub> = 300pf)                          |        | 20   | 30         | ns    |                 |             |             |              |      |       |       |        | 10, 12  |

| Logic 0 to High Z, tpLZ                                 |        | 20   | 30         |       |                 |             |             |              |      |       |       |        | 11, 1   |

| High Z (C, = 300pf)                                     |        | 20   | 30         | ns    |                 |             |             |              |      |       |       |        | , , , , |

| Clear to Output                                         |        |      |            |       |                 |             |             |              |      |       |       |        | ļ       |

| C <sub>L</sub> = 30pf                                   |        | 15   | 22         | ns    |                 |             |             |              |      |       |       |        | 12      |

| $C_1 = 300pf$                                           |        | 21   | 30         | ns    |                 |             |             |              | i    | 1     |       | ľ      | 12      |

| Set Up Time, t <sub>setup</sub>                         |        |      |            |       |                 |             |             |              |      |       |       |        |         |

| Data                                                    | +5     | -1   |            | ns    |                 |             |             |              | 1    | 1     |       |        | 12      |

| Input Disable                                           |        | -6   | 0          | ns    |                 |             |             |              |      |       |       |        | 12      |

| Hold Time, t <sub>hold</sub>                            |        |      |            |       |                 |             |             |              |      |       |       | ł      | 1       |

| Data                                                    |        | -1   | +5         | ns    |                 |             |             |              |      | }     |       |        | 12      |

| Reset Pulse Width                                       | 15     |      |            | ns    |                 |             |             |              |      |       |       |        | 12      |

| Clock Frequency                                         | 35     | 50   |            | MHz   |                 |             |             |              |      | 1     | 1     |        | 12      |

| Clock Pulse Width                                       |        |      |            |       |                 |             |             |              | !    |       |       |        |         |

| Positive                                                |        | 8    | 12         | ns    |                 |             |             |              | 1    |       |       | [      | 12      |

| Negative                                                |        | 8    | 12<br>619/ | ns    |                 |             |             |              |      | l     |       |        | 12      |

| Power/Current Consumption                               | 40     |      | 118        | mW/mA |                 | 0.4V        | 0.4V        | 4.5V         | 0.4  | 0.4   | 4.5V  |        | 8       |

| Output Short Circuit Current                            | -40    |      | -120       | mA    | 4.5V            | 0.4V        | 0.4V        | 0.4∨         | 0.4V | 0.4V  |       | 0.0∨   | 8, 9    |

#### NOTES:

- All voltage and capacitance measurements are referenced to the ground terminal. Terminals not specifically referenced are left electrically open.

- All measurements are taken with ground pin tied to zero volts.

- Positive current flow is defined as into the terminal referenced.

- Positive logic definition: "UP" Level = "1", "DOWN" Level = "0".

- Precautionary measures should be taken to ensure current limiting in accordance with Absolute Maximum Ratings

- should the isolation diodes become forward blased.

- 6. Output source current is supplied through a resistor to ground.

- Output sink current is supplied through a resistor to V<sub>CC</sub>.

- 8.  $V_{CC} = 5.25V$ .

- 9. Not more than one output should be shorted at a time.

- 10. Measured to 1,5V level of output waveform.

- Measured to 10% level of output waveform. 11.

- Refer to AC Test Circuits.

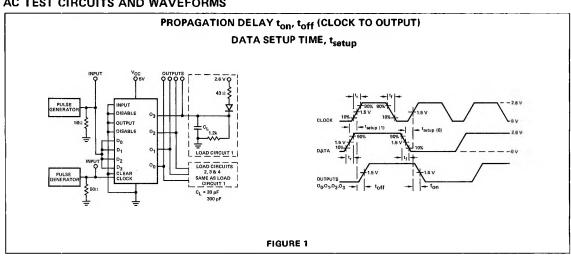

## AC TEST CIRCUITS AND WAVEFORMS

# AC TEST CIRCUITS AND WAVEFORMS (Cont'd) PROPAGATION DELAY (CLEAR TO OUTPUT) FIGURE 2 PROPAGATION DELAY (DATA HOLD TIME) FIGURE 3 PROPAGATION DELAY (DISABLE TO OUTPUT) OUTPUTS... O<sub>0</sub>,O<sub>1</sub>,O<sub>2</sub>,O<sub>3</sub>

FIGURE 4

HIGH 2 TO "0"

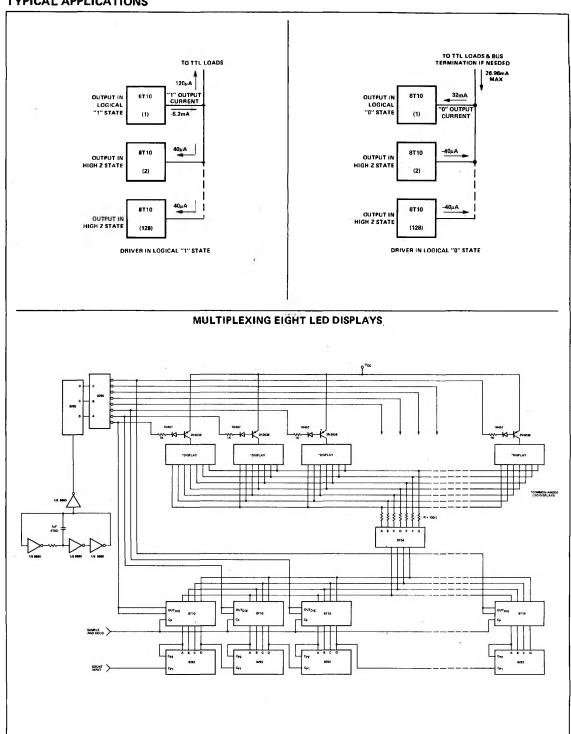

# **TYPICAL APPLICATIONS**