HI2300

8-Bit, 18 MSPS, Video A/D Converter with 3.3V Power Supply Operation

August 1997

#

- Reference Voltage Self-Bias Circuit

Input CMOS Compatible

- Three-State TTL Compatible Output

- Power Supply . . . . . . . . . . . . . . . . . . 3.3V Single

- Low Input Capacitance ......8pF

- Direct Replacement for Sony CXD2300

### **Applications**

- · Portable Equipment

- · Hand-Held Instruments

### Description

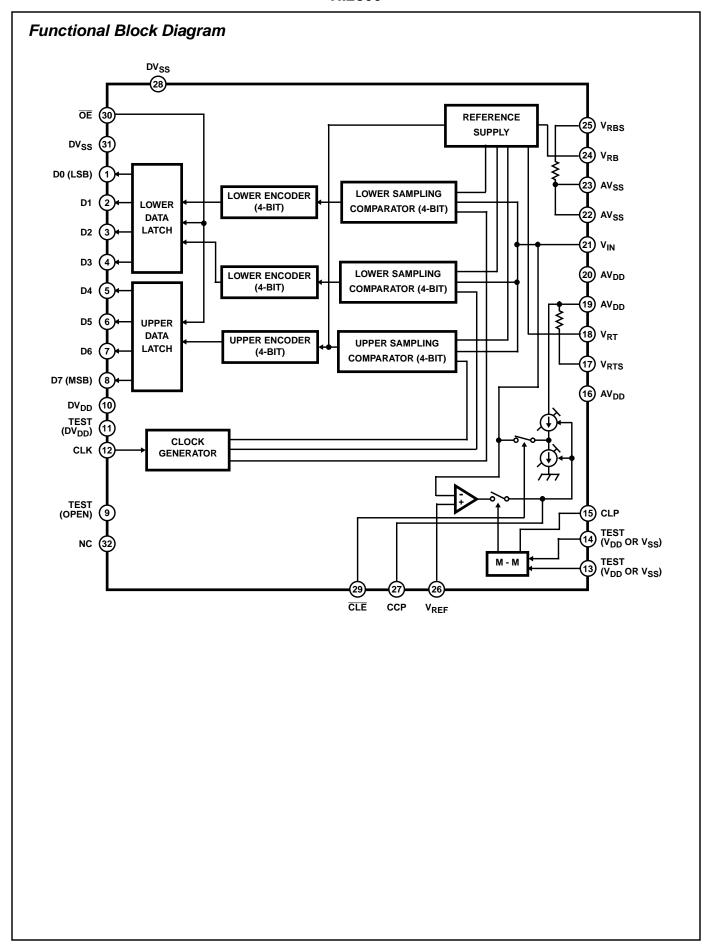

The HI2300 is an 8-bit, CMOS A/D converter for video with synchronizing clamp function and can operate on 3.3V power supply. The adoption of 2 step-parallel method achieves ultra-low power consumption and a maximum conversion speed of 18 MSPS.

### **Ordering Information**

| PART<br>NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG. NO.  |  |

|----------------|---------------------|------------|-----------|--|

| HI2300JCQ      | -40 to 85           | 32 Ld MQFP | Q32.7x7-S |  |

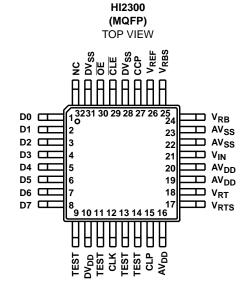

### **Pinout**

## Pin Descriptions

| PIN NUMBER      | SYMBOL           | EQUIVALENT CIRCUIT                  | DESCRIPTION                                                                                                 |  |  |  |  |

|-----------------|------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1 to 8 D0 to D7 |                  |                                     | D0 (LSB) to D7 (MSB) Output.                                                                                |  |  |  |  |

| 9               | TEST             | 9 DV <sub>DD</sub> DV <sub>SS</sub> | Leave open during normal usage.                                                                             |  |  |  |  |

| 10              | DV <sub>DD</sub> |                                     | Digital +3.3V.                                                                                              |  |  |  |  |

| 12              | CLK              | DV <sub>DD</sub> DV <sub>SS</sub>   | Clock Input.                                                                                                |  |  |  |  |

| 11, 13, 14      | TEST             | DV <sub>DD</sub> DV <sub>SS</sub>   | Fix Pin 11 to V <sub>DD</sub> , Pins 13 and 14 to V <sub>DD</sub> over V <sub>SS</sub> during normal usage. |  |  |  |  |

| 15              | CLP              | (15) DV <sub>DD</sub>               | Inputs Clamp Pulse to Pin 15 (CLP). Clamp the signal voltage during Low interval.                           |  |  |  |  |

| 16, 19, 20      | AV <sub>DD</sub> |                                     | Analog +3.3V                                                                                                |  |  |  |  |

| 17              | V <sub>RTS</sub> | AV <sub>DD</sub>                    | Generates approximately +1.8V when shorted with V <sub>RT</sub> .                                           |  |  |  |  |

| 18              | V <sub>RT</sub>  | o AV <sub>DD</sub>                  | Reference Voltage (Top).                                                                                    |  |  |  |  |

| 24              | V <sub>RB</sub>  | 18 AV <sub>SS</sub>                 | Reference Voltage (Bottom).                                                                                 |  |  |  |  |

## Pin Descriptions (Continued)

| PIN NUMBER | SYMBOL           | EQUIVALENT CIRCUIT                | Analog Input.                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------|------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 21         | V <sub>IN</sub>  | 21 AV <sub>DD</sub>               |                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 25         | V <sub>BRS</sub> | AV <sub>SS</sub>                  | Generates approximately +0.4V when shorte with $\ensuremath{V_{RB}}.$                                                                                                                                                                                                                                       |  |  |  |  |

| 26         | V <sub>REF</sub> | AV <sub>DD</sub> AV <sub>SS</sub> | Clamp Reference Voltage Input. Clamps s that the reference voltage and the input signs during clamp interval are equal.                                                                                                                                                                                     |  |  |  |  |

| 27         | CCP              | AV <sub>DD</sub> AV <sub>SS</sub> | Integrates the clamp control voltage. The relationship between the changes in CC voltage and in V <sub>IN</sub> voltage is positive phase.                                                                                                                                                                  |  |  |  |  |

| 28, 31     | DV <sub>SS</sub> |                                   | Digital Ground.                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 29         | CLE              | 29  CLAMP PULSE                   | The clamp function is enabled when \$\overline{CLE}\$ = Low.  The clamp function is set to off and the converter functions as a normal A/D converted when \$\overline{CLE}\$ = High.  The clamp pulse can be measured be connecting \$\overline{CLE}\$ to \$DV_{DD}\$ through several-hundred-ohm resistor. |  |  |  |  |

| 30         | ŌĒ               | 30 DV <sub>DD</sub>               | Data is output when $\overline{OE}$ = Low. Pins D0 to D are at high impedance when $\overline{OE}$ = High.                                                                                                                                                                                                  |  |  |  |  |

|            |                  | 6 DV <sub>SS</sub>                |                                                                                                                                                                                                                                                                                                             |  |  |  |  |

### HI2300

#### **Absolute Maximum Ratings** T<sub>A</sub> = 25°C **Thermal Information** Supply Voltage (V<sub>DD</sub>)......7V Thermal Resistance (Typical, Note 1) $\theta_{JA}$ (°C/W) Reference Voltage (V<sub>RT</sub>, V<sub>RB</sub>).....V<sub>DD</sub> +0.5V to V<sub>SS</sub> - 0.5V Maximum Junction Temperature (Plastic Package) . . . . . . . 150°C Input Voltage, Digital (V $_{IH}$ , V $_{IL}$ ) ........V $_{DD}$ +0.5V to V $_{SS}$ - 0.5V Output Voltage, Digital (V $_{OH}$ , V $_{OL}$ ) .....V $_{DD}$ +0.5V to V $_{SS}$ - 0.5V Maximum Storage Temperature Range .....-65°C to 150°C Maximum Lead Temperature (Soldering 10s).....300°C (MQFP - Lead Tips Only) **Recommended Operating Conditions** Temperature Range ( $t_{OPR}$ ) . . . . . . . . . . -40°C to 85°C Analog Input (ADIN) . . . . . . . . . . . V<sub>RT</sub> to V<sub>RB</sub> Supply Voltage (IDV<sub>SS</sub> - AV<sub>SS</sub>I). . . . . . . . . . 0 to 100mV Clock Pulse width (t<sub>PW1</sub>) . . . . . . . . . . . . . . . . 27ns (Min) Power Supply (DV<sub>DD</sub>, DV<sub>SS</sub>)(AV<sub>DD</sub>, AV<sub>SS</sub>). . . . . . . . . 3.14V to 4.0V (V<sub>RT</sub>).....1.8V

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

**Electrical Specifications** When using a single power supply;  $f_C = 18$  MSPS,  $V_{DD} = 3.3V$ ,  $V_{RB} = 0V$ ,  $V_{RT} = 1.5V$ ,  $T_A = 25^{\circ}C$

| PARAMETER                                                  | SYMBOL                              | TEST CONDITIONS                                                       |                                                | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------|------------------------------------------------|------|------|------|-------|

| Maximum Conversion Rate                                    | f <sub>C</sub> Max                  | V <sub>IN</sub> = 0 to 1.5V                                           |                                                | 18   | 32   | -    | MSPS  |

| Minimum Conversion Rate                                    | f <sub>C</sub> Min                  | f <sub>IN</sub> = 1kHz Ramp                                           | =                                              | 32   | 0.5  | MSPS |       |

| Supply Current                                             | I <sub>DD</sub>                     | $f_C = 18 \text{ MSPS}, N^T$                                          | f <sub>C</sub> = 18 MSPS, NTSC Ramp Wave Input |      |      | 10   | mA    |

| Reference Pin Current                                      | I <sub>REF</sub>                    |                                                                       |                                                | 3.3  | 4.6  | 6.6  | mA    |

| Analog Input Band Width                                    | BW                                  | $V_{IN} = 1.4V_{P-P}, 1$                                              | 7.9MHz                                         | -    | 9    | -    | dB    |

| Analog Input Capacitance                                   | C <sub>IN</sub>                     | $V_{IN} = 0.75V + 0.0$                                                | 07 V <sub>RMS</sub>                            | -    | 8    | -    | pF    |

| Reference Resistance (V <sub>RT</sub> to V <sub>RB</sub> ) | R <sub>REF</sub>                    |                                                                       |                                                | 230  | 330  | 440  | Ω     |

| Self Bias I                                                | V <sub>RB1</sub>                    | Shorts V <sub>RB</sub> and                                            | V <sub>RBS</sub>                               | 0.33 | 0.36 | 0.39 | V     |

|                                                            | V <sub>RT1</sub> - V <sub>RB1</sub> | Shorts V <sub>RT</sub> and V                                          | V <sub>RTS</sub>                               | 1.30 | 1.39 | 1.48 | V     |

| Offset Voltage                                             | E <sub>OT</sub>                     |                                                                       |                                                | -45  | -25  | -5   | mV    |

|                                                            | E <sub>OB</sub>                     |                                                                       |                                                | 40   | 60   | 80   | mV    |

| Digital Input Voltage                                      | V <sub>IH</sub>                     |                                                                       |                                                | 2.5  | -    | -    | V     |

|                                                            | V <sub>IL</sub>                     |                                                                       |                                                | -    | -    | 0.5  | V     |

| Digital Input Current                                      | I <sub>IH</sub>                     | V <sub>DD</sub> = Max                                                 | $V_{IH} = V_{DD}$                              | -    | -    | 5    | μΑ    |

|                                                            | I <sub>IL</sub>                     |                                                                       | $V_{IL} = 0V$                                  | -    | -    | -    | μΑ    |

| Digital Output Current                                     | ГОН                                 | OE = V <sub>SS</sub>                                                  | $V_{OH} = V_{DD} - 0.5V$                       | -1.0 | -    | -    | mA    |

|                                                            | I <sub>OL</sub>                     | $V_{DD} = Min$                                                        | V <sub>OL</sub> = 0.4V                         | 3.3  | -    | -    | mA    |

| Digital Output Current                                     | lozh                                | OE = V <sub>DD</sub>                                                  | $V_{OH} = V_{DD}$                              | -    | -    | 16   | μΑ    |

|                                                            | I <sub>OZL</sub>                    | V <sub>DD</sub> = Max                                                 | V <sub>OL</sub> = 0V                           | -    | -    | 16   | μΑ    |

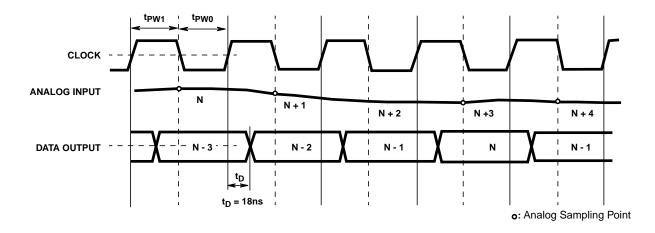

| Output Data Delay                                          | t <sub>DL</sub>                     | With TTL 1 Gate and 10pF Load                                         |                                                | 8    | 18   | 30   | ns    |

| Three-State Output Enable Time                             | t <sub>PZH</sub>                    | $R_L = 1k\Omega$ , $C_L = 20pF$ , $\overline{OE} = 3V \rightarrow 0V$ |                                                |      |      |      |       |

|                                                            | t <sub>PZL</sub>                    |                                                                       |                                                |      |      |      |       |

| Three-State Output Disable Time                            | t <sub>PHZ</sub>                    | $R_L = 1k\Omega$ , $C_L = 2$                                          |                                                |      |      |      |       |

|                                                            | t <sub>PLZ</sub>                    |                                                                       |                                                |      |      |      |       |

| Integral Nonlinearity Error                                | EL                                  | $f_C = 18 \text{ MSPS}$<br>$V_{IN} = 0 \text{ to } 1.5 \text{V}$      | -                                              | +0.5 | ±1.3 | LSB  |       |

| Differential Nonlinearity Error                            | E <sub>D</sub>                      | f <sub>C</sub> = 18 MSPS<br>V <sub>IN</sub> = 0 to 1.5V               |                                                | -    | ±0.3 | ±0.5 | LSB   |

| Aperture Jitter                                            | t <sub>AJ</sub>                     |                                                                       |                                                | -    | 30   | -    | ps    |

| Sampling Delay                                             | t <sub>SD</sub>                     |                                                                       |                                                | -    | 4    | -    | ns    |

| Clamp Offset Voltage                                       | E <sub>OC</sub>                     | V <sub>IN</sub> = DC                                                  | V <sub>REF</sub> = 0.5V                        | -20  | 0    | +20  | mV    |

|                                                            |                                     | PWS = 3μs                                                             | V <sub>REF</sub> = 1.5V                        | -30  | -10  | +10  | mV    |

| Clamp Pulse Delay                                          | tCPD                                |                                                                       |                                                | -    | 25   | -    | ns    |

## **Digital Output**

The following table shows the relationship between analog input voltage and digital output code.

|                         |      | DIGITAL OUTPUT CODE |    |   |   |   |   |    |    |

|-------------------------|------|---------------------|----|---|---|---|---|----|----|

| INPUT SIGNAL<br>VOLTAGE | STEP | M                   | SB |   |   |   |   | LS | SG |

| V <sub>RT</sub>         | 0    | 1                   | 1  | 1 | 1 | 1 | 1 | 1  | 1  |

| •                       | •    |                     |    |   | • | • |   |    |    |

| •                       | •    |                     |    |   | • | • |   |    |    |

| •                       | •    |                     |    |   |   | • |   |    |    |

| •                       | 127  | 1                   | 0  | 0 | 0 | 0 | 0 | 0  | 0  |

|                         | 128  | 0                   | 1  | 1 | 1 | 1 | 1 | 1  | 1  |

|                         | •    |                     |    |   |   | • |   |    |    |

|                         | •    |                     |    |   |   | • |   |    |    |

|                         | •    |                     |    |   |   |   |   |    |    |

| V <sub>RB</sub>         | 255  | 0                   | 0  | 0 | 0 | 0 | 0 | 0  | 0  |

# Timing Chart

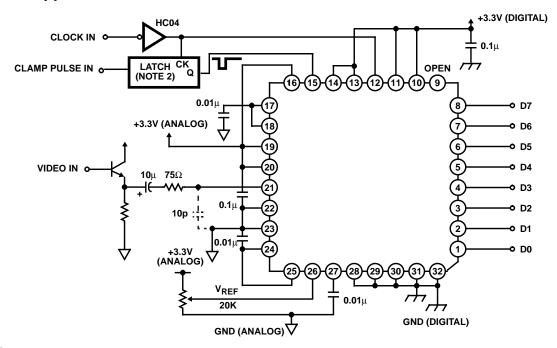

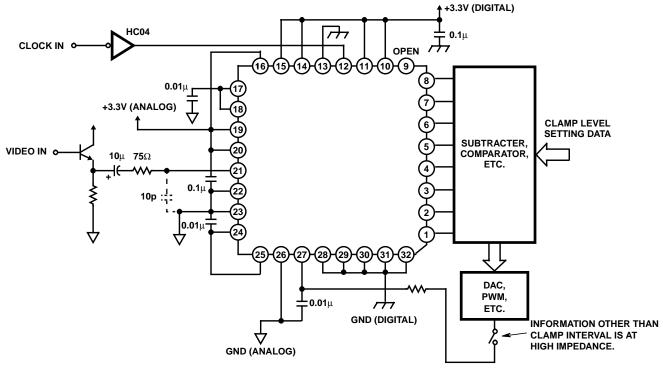

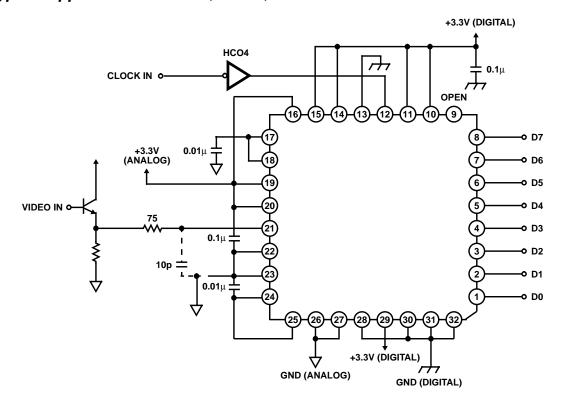

### **Typical Application Circuits**

### NOTE:

1. The clamp pulse is latched by the sampling clock of ADC, but that is not necessary for basic clamp operaiotn. However, slight small beat may be generated as Vertical sag according to the relationship between the sampling frequency and the clamp pulse frequency. At such time, the latch circuit is efective in this case.

FIGURE 1. WHEN CLAMP IS USED (SELF BIAS)

### NOTES:

- 2. The relationship between the changes in CCP voltage (Pin 27) and in V<sub>IN</sub> voltage is positive phase.

- 3.  $\Delta V_{IN}/\Delta V_{CCP} = 3.0$  (f<sub>S</sub> = 20 MSPS).

FIGURE 2. DIGITAL CLAMP (SELF BIAS)

## Typical Application Circuits (Continued)

FIGURE 3. WHEN CLAMP IS NOT USED (SELF BIAS)

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com