# ICM7213

One Second/One Minute Timebase Generator

December 2001

## Features

- Guaranteed 2V Operation

- Very Low Current Consumption (Typ)....100μA at 3V

- All Outputs TTL Compatible

- On Chip Oscillator Feedback Resistor

- Oscillator Requires Only 3 External components: Fixed Capacitor, Trim Capacitor, and A Quartz Crystal

- Output Inhibit Function

- 4 Simultaneous Outputs: One Pulse/s, One Pulse/Min, 16Hz and Composite 1024 + 16 + 2Hz Outputs

- Test Speed-Up Provides Other Frequency Outputs

#### Part Number Information

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |

|-------------|---------------------|------------|-------------|

| ICM7213IPD  | -25 to 85           | 14 Ld PDIP | E14.3       |

## Description

The ICM7213 is a fully integrated micropower oscillator and frequency divider with four buffered outputs suitable for interfacing with most logic families. The power supply may be either a two battery stack (Ni-cad, alkaline, etc.) or a regular power supply greater than 2V. Depending upon the state of the WIDTH, INHIBIT, and TEST inputs, using a 4.194304MHz crystal will produce a variety of output frequencies including 2048Hz, 1024Hz, 34.133Hz, 16Hz, 1Hz, and  $^1\!\!/_{60}$ Hz (plus composites).

The ICM7213 utilizes a very high speed low power metal gate CMOS technology which uses 6.4V zeners between the drains and sources of each transistor and also across the supply terminals. Consequently, the ICM7213 is limited to a 6V maximum  $V_{\mbox{SUPPLY}}$ , although a simple dropping network can be used to extend the  $V_{\mbox{SUPPLY}}$  range well above 6V (See Figure 9).

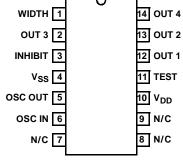

## **Pinout**

ICM7213 (PDIP) TOP VIEW

#### ICM7213

## **Absolute Maximum Ratings**

#

#### **Thermal Information**

| Thermal Resistance (Typical, Not | te 1) $\theta_{JA}$ | (°C/W)             |

|----------------------------------|---------------------|--------------------|

| PDIP Package                     |                     | 100                |

| Maximum Junction Temperature.    |                     | 150 <sup>0</sup> C |

| Maximum Storage Temperature F    | Range65°C to        | 150°C              |

| Maximum Lead Temperature (So     | ldering, 10s)       | 300°C              |

## **Operating Conditions**

Temperature Range . . . . . -25°C to 85°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

$\textbf{Electrical Specifications} \qquad \text{V}_{DD} - \text{V}_{SS} = 3.0 \text{V}, \text{ } \text{f}_{OSC} = 4.194304 \text{MHz}, \text{ Test Circuit, } \text{T}_{A} = 25^{o}\text{C}, \text{ Unless Otherwise Specified } \text{Test Circuit}, \text{ } \text{Test Circuit, } \text{Test Circu$

| PARAMETER                                                                                              | TEST CONDITIONS                                  | MIN | TYP | MAX | UNIT |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|

| Supply Current, I <sub>DD</sub>                                                                        |                                                  | -   | 100 | 140 | μΑ   |

| Guaranteed Operating Supply<br>Voltage Range (V <sub>DD</sub> - V <sub>SS</sub> ), V <sub>SUPPLY</sub> | -20°C to 85°C                                    | 2   | -   | 4   | V    |

| Output Leakage Current, I <sub>OLK</sub>                                                               | Any output, V <sub>OUT</sub> = 6V                | -   | -   | 10  | μΑ   |

| Output Sat. Resistance, R <sub>OUT</sub>                                                               | Any output, I <sub>OLK</sub> = 2.5mA             | -   | 120 | 200 | Ω    |

| Inhibit Input Current, II                                                                              | Inhibit terminal connected to V <sub>DD</sub>    | -   | 10  | 40  | μΑ   |

| Test Point Input Current, I <sub>TP</sub>                                                              | Test point terminal connected to V <sub>DD</sub> | -   | 10  | 40  | μΑ   |

| Width Input Current, I <sub>W</sub>                                                                    | Width terminal connected to V <sub>DD</sub>      | -   | 10  | 40  | μΑ   |

| Oscillator Transconductance, g <sub>M</sub>                                                            | V <sub>DD</sub> = 2V                             | 100 | -   | -   | μS   |

| Oscillator Frequency Range (Note 1), fOSC                                                              |                                                  | 1   | -   | 10  | MHz  |

| Oscillator Stability, f <sub>STAB</sub>                                                                | 2V < V <sub>DD</sub> < 4V                        | -   | 1.0 | -   | ppm  |

| Oscillator Start Time, t <sub>S</sub>                                                                  |                                                  | -   | 0.1 | -   | S    |

|                                                                                                        | $V_{DD} = 2V$                                    | -   | 0.2 | -   | S    |

#### NOTE:

#### **Output Definitions**

| (NOTE 1) INPUT STATES |         | PIN 12 | PIN 13                 | PIN 2                                                                       | PIN 14                            |                                              |  |

|-----------------------|---------|--------|------------------------|-----------------------------------------------------------------------------|-----------------------------------|----------------------------------------------|--|

| TEST                  | INHIBIT | WIDTH  | OUT 1                  | OUT 2                                                                       | OUT 3                             | OUT 4                                        |  |

| L                     | L       | L      | 16Hz ÷ 2 <sup>18</sup> | $\overline{1024 + 16 + 2}$ Hz (÷ $2^{12}$ ÷ $2^{18}$ ÷ $2^{21}$ ) Composite | 1Hz, 7.8ms $\div 2^{22}$          | 1/60Hz, 1s $\div (2^{24} \times 3 \times 5)$ |  |

| L                     | L       | Н      | 16Hz ÷ 2 <sup>18</sup> | $1024 + 16 + 2$ Hz (÷ $2^{12} \div 2^{18} \div 2^{21}$ ) Composite          | 1Hz, 7.8ms $\div$ 2 <sup>22</sup> | <sup>1</sup> / <sub>60</sub> Hz, 125ms       |  |

| L                     | Н       | L      | 16Hz ÷ 2 <sup>18</sup> | $\overline{1024 + 16}$ Hz (÷ 2 <sup>12</sup> ÷ 2 <sup>18</sup> ) Composite  | OFF                               | OFF                                          |  |

| L                     | Н       | Н      | 16Hz ÷ 2 <sup>18</sup> | $1024 + 16$ Hz (÷ $2^{12} \div 2^{18}$ ) Composite                          | OFF                               | See Waveforms                                |  |

| Н                     | L       | L      | ON                     | 4096 + 1024Hz (÷ 2 <sup>10</sup> ÷ 2 <sup>12</sup> ) Composite              | 2048Hz ÷ 2 <sup>11</sup>          | 34.133Hz, 50% DC ÷ (2 <sup>13</sup> x 5 x 3) |  |

| Н                     | L       | Н      | ON                     | 4096 + 1024Hz (÷ 2 <sup>10</sup> ÷ 2 <sup>12</sup> ) Composite              | 2048Hz ÷ 2 <sup>11</sup>          | 34.133Hz, 50% DC ÷ (2 <sup>13</sup> x 5 x 3) |  |

| Н                     | Н       | L      | ON                     | 1024Hz ÷ 2 <sup>12</sup>                                                    | ON                                | OFF                                          |  |

| Н                     | Н       | Н      | ON                     | 1024Hz ÷ 2 <sup>12</sup>                                                    | ON                                | OFF                                          |  |

#### NOTE

<sup>1.</sup> The ICM7213 uses dynamic dividers for high frequency division. As with any dynamic system, information is stored on very small nodal capacitances instead of latches (static system), therefore there is a lower frequency of operation. Dynamic dividers are used to improve the high frequency performance while at the same time significantly decreasing power consumption. At low V<sub>SUPPLY</sub>, operation at less than 1MHz is possible.

<sup>1.</sup> When TEST and RESET are connected to ground, or left open, all outputs except for OUT 3 and OUT 4 have a 50% duty cycle.

## **Timing Waveforms** 1024Hz \_ 16Hz 2Hz FIGURE 1. OUTPUT WAVEFORM INHIBIT OUT 3 <7.8ms CASE 1 0.75s to 1.0s OUT4 **→** 59.75s <125ms to 60s <7.8ms OUT 3 CASE 2 (PULSE 3 <7.8ms COINCIDENT WITH INHIBIT) OUT 4 OUT 3 CASE 3 (EFFECT OF OUT 4 WIDTH ON OUT 4) **WIDTH** OUT 3 CASE 4 OUT 4 (EFFECT OF WIDTH ON OUT 4) **WIDTH**

FIGURE 2. EFFECT OF THE INHIBIT (TEST CONNECTED TO  $V_{\mbox{\footnotesize SS}}$  OR LEFT OPEN)

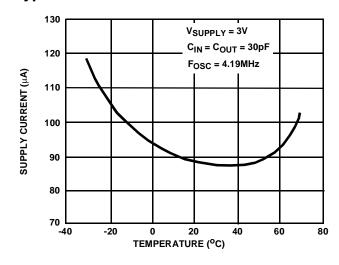

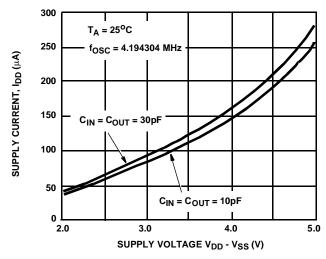

# **Typical Performance Curves**

FIGURE 4. SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

# Typical Performance Curves (Continued)

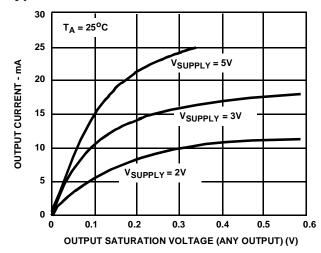

FIGURE 5. OUTPUT CURRENT AS A FUNCTION OF OUTPUT

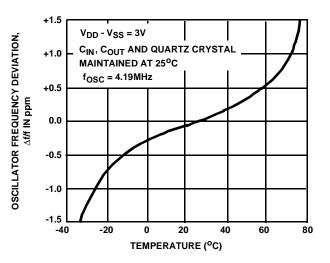

FIGURE 6. OSCILLATOR STABILITY AS A FUNCTION OF DEVICE TEMPERATURE

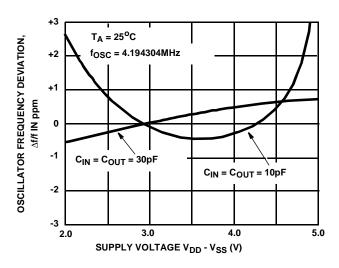

FIGURE 7. OSCILLATOR STABILITY AS A FUNCTION OF SUPPLY VOLTAGE

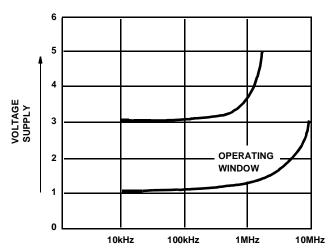

FIGURE 8. WINDOW OF CORRECT OPERATION

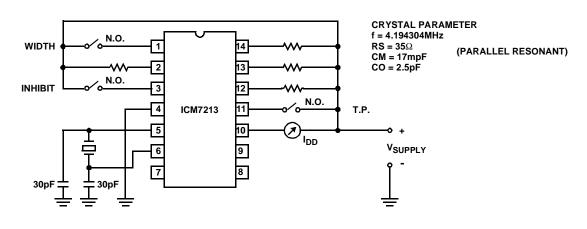

## **Test Circuit**

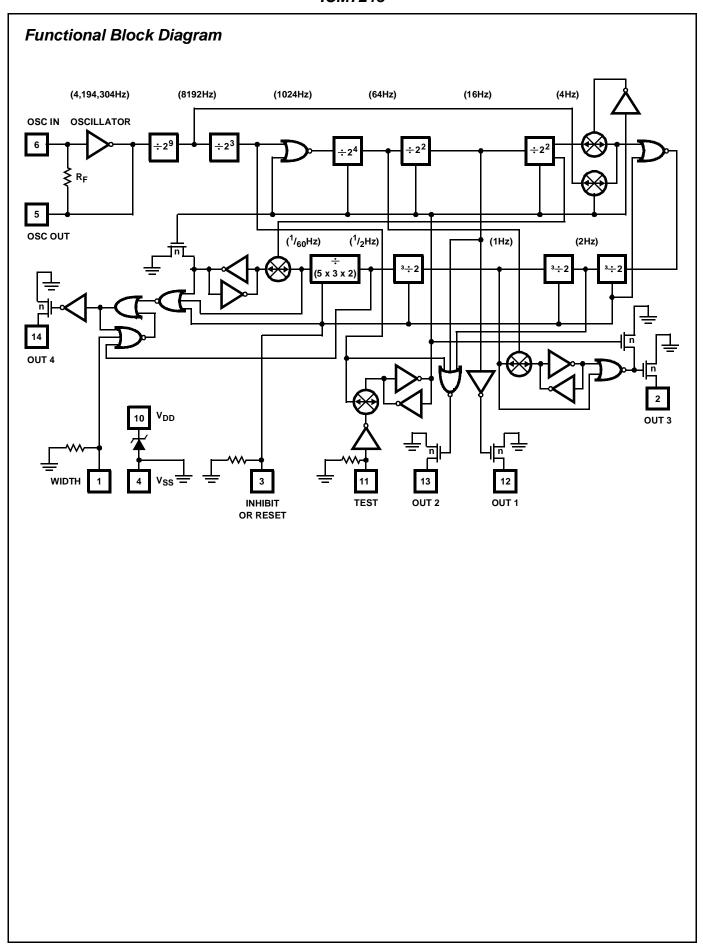

## **Detailed Description**

## **Supply Voltage Considerations**

The ICM7213 may be used to provide various precision outputs with frequencies from 2048Hz to  $^{1}/_{60}$ Hz using a 4.194304MHz quartz oscillator, and other output frequencies may be obtained using other quartz crystal frequencies. Since the ICM7213 uses dynamic high frequency dividers for the initial frequency division there are limitations on the  $V_{\mbox{SUPPLY}}$  range depending on the oscillator frequency. If, for example, a low frequency quartz crystal is selected, the  $V_{\mbox{SUPPLY}}$  should be selected in the center of the operating window, or approximately 1.7V.

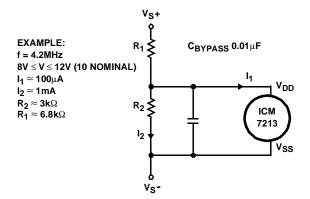

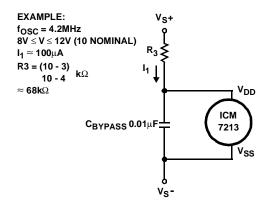

The V<sub>SUPPLY</sub> to the ICM7213 may be derived from a high voltage supply by using a simple resistor divider (if power is of no concern), by using a series resistor for minimum current consumption, or by means of a regulator.

#### Outputs

Pull up resistors will generally be required to interface with other logic families. These resistors must be connected between the various outputs and the positive power supply.

#### **Oscillator Considerations**

The oscillator consists of a CMOS inverter and a feedback resistor whose value is dependent on the voltage at the oscillator input and output terminals and the V<sub>SUPPLY</sub>. Oscillator stabilities of approximately 0.1ppm per 0.1V variation are achievable with a nominal V<sub>SUPPLY</sub> of 5V and a single voltage dropping resistor. The crystal specifications are shown in the Test Circuit.

It is recommended that the crystal load capacitance (CL) be no greater than 22pF for a crystal having a series resistance equal to or less than 75 $\Omega$ , otherwise the output amplitude of the oscillator may be too low to drive the divider reliably.

It a very high quality oscillator is desired, it is recommended that a quartz crystal be used having a tight tuning tolerance  $\pm 10 \text{ppm}$ , a low series resistance (less than  $25\Omega)$ , a low motional capacitance of 5mpF and a load capacitance of 20pF. The fixed capacitor  $C_{IN}$  should be 30pF and the oscillator tuning capacitor should range between approximately 16pF and 60pF.

Use of a high quality crystal will result in typical stabilities of 0.05ppm per 0.1V change of  $V_{\mbox{SUPPLY}}$ .

## **Control Inputs**

The TEST input inhibits the  $2^{18}$  output and applies the  $2^9$  output to the  $2^{21}$  divider, thereby permitting a speedup of the testing of the  $\div$  60 section by a factor of 2048 times. This also results in alternative output frequencies (see table).

The WIDTH input may be used to change the pulse width of OUT 4 from 125ms to 1s, or to change the state of OUT 4 from ON to OFF during INHIBIT.

See Figures 1 and 2 for output waveforms and effect of control inputs.

FIGURE 9A.

FIGURE 9B.

FIGURE 9. BIASING SCHEMES WITH HIGH VOLTAGE SUPPLIES

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

# Sales Office Headquarters

**NORTH AMERICA EUROPE ASIA** Intersil Corporation Intersil Corporation Intersil Corporation Intersil Europe Sarl 7585 Irvine Center Drive 2401 Palm Bay Rd. Ave. C - F Ramuz 43 Unit 1804 18/F Guangdong Water Building Suite 100 Palm Bay, FL 32905 CH-1009 Pully 83 Austin Road Irvine, CA 92618 TEL: (321) 724-7000 Switzerland TST, Kowloon Hong Kong TEL: (949) 341-7000 FAX: (321) 724-7946 TEL: +41 21 7293637 TEL: +852 2723 6339 FAX: +41 21 7293684 FAX: +852 2730 1433 FAX: (949) 341-7123