## CMOS SyncBiFIFO™ 256 x 18 x 2 512 x 18 x 2

IDT72605 IDT72615

#### **FEATURES:**

- Two independent FIFO memories for fully bidirectional data transfers

- 256 x 18 x 2 organization (IDT72605)

- 512 x 18 x 2 organization (IDT72615)

- · Synchronous interface for fast (20ns) read and write cycle times

- Each data port has an independent clock and read/write control

- Output enable is provided on each port as a three-state control of the data bus

- Built-in bypass path for direct data transfer between two ports

- Two fixed flags, Empty and Full, for both the A-to-B and the Bto-A FIFO

- . Programmable flag offset can be set to any depth in the FIFO

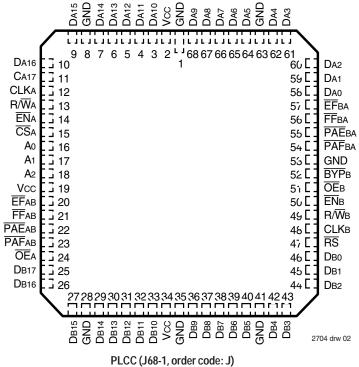

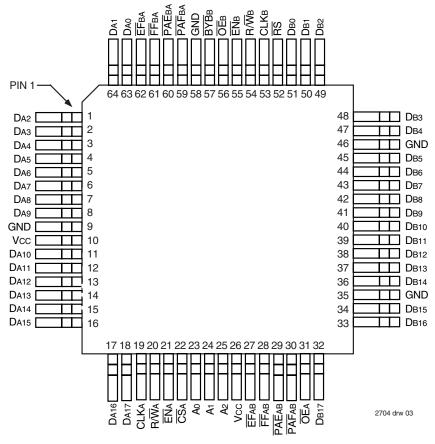

- The synchronous BiFIFO is packaged in a 64-pin TQFP (Thin Quad Flatpack) and 68-pin PLCC

- Industrial temperature range (-40°C to +85°C)

#### **DESCRIPTION:**

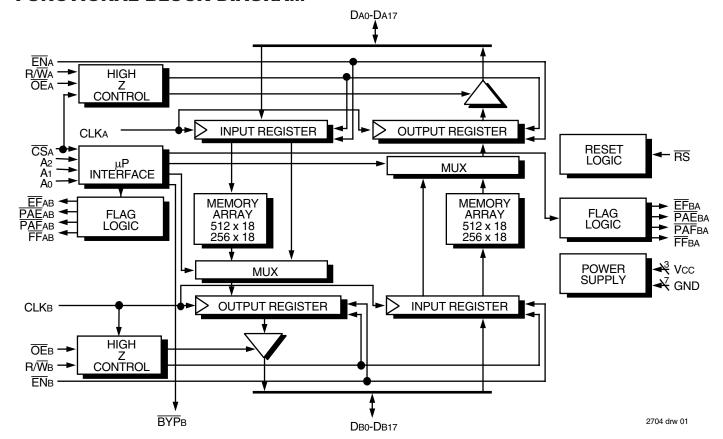

The IDT72605 and IDT72615 are very high-speed, low-power bidirectional First-In, First-Out (FIFO) memories, with synchronous interface for fast

read and write cycle times. The SyncBiFIFO $^{TM}$  is a data buffer that can store or retrieve information from two sources simultaneously. Two Dual-Port FIFO memory arrays are contained in the SyncBiFIFO; one data buffer for each direction.

The SyncBiFIFO has registers on all inputs and outputs. Data is only transferred into the I/O registers on clock edges, hence the interfaces are synchronous. Each Port has its own independent clock. Data transfers to the I/O registers are gated by the enable signals. The transfer direction for each port is controlled independently by a read/write signal. Individual output enable signals control whether the SyncBiFIFO is driving the data lines of a port or whether those data lines are in a high-impedance state.

Bypass control allows data to be directly transferred from input to output register in either direction.

The SyncBiFIFO has eight flags. The flag pins are Full, Empty, Almost-Full, and Almost-Empty for both FIFO memories. The offset depths of the Almost-Full and Almost-Empty flags can be programmed to any location.

The SyncBiFIFO is fabricated using IDT's high-speed, submicron CMOS technology.

## **FUNCTIONAL BLOCK DIAGRAM**

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The SyncBiFIFO is a trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

**APRIL 2003**

#### **PIN CONFIGURATIONS**

**TOP VIEW**

TQFP (PN64-1, order code: PF) TOP VIEW

## **PIN DESCRIPTION**

| . If R/WA is HIGH, utput register. If  A is HIGH, Port A is mpedance) state. |

|------------------------------------------------------------------------------|

| utput register. If  A is HIGH, Port A is                                     |

| utput register. If  A is HIGH, Port A is                                     |

| utput register. If  A is HIGH, Port A is                                     |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

| If R/W  B is HIGH,  utput register. If                                       |

|                                                                              |

|                                                                              |

| в is HIGH, Port В is                                                         |

| s HIGH, the FIFO is<br>vailable for passing                                  |

| the offset<br>в Register. The                                                |

| minus the offset<br>epth minus the                                           |

| GH, the FIFO is not<br>output register. If<br>ner message can be             |

| s HIGH, the FIFO<br>s available for                                          |

| the offset<br>A Register. The                                                |

| h minus the offset<br>depth minus the                                        |

| GH, the FIFO is<br>A's output register. It<br>er message can be              |

| aced the FIFO into to CLKB.                                                  |

|                                                                              |

|                                                                              |

|                                                                              |

|                                                                              |

## **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol | Rating                                     | Industrial   | Unit |

|--------|--------------------------------------------|--------------|------|

| VTERM  | Terminal Voltage with<br>Respect to Ground | -0.5 to +7.0 | V    |

| Tstg   | Storage Temperature                        | -55 to +125  | °C   |

| lout   | DC Output Current                          | -50 to +50   | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

# RECOMMENDED DC OPERATING CONDITIONS

| SYM | IBOL | PARAMETER             | MIN. | TYP. | MAX. | UNIT |

|-----|------|-----------------------|------|------|------|------|

| Vc  | C    | Supply Voltage        | 4.5  | 5.0  | 5.5  | V    |

| GI  | ND   | Supply Voltage        | 0    | 0    | 0    | V    |

| VII | 1    | Input High Voltage    | 2.0  | _    | _    | V    |

| VIL | (1)  | Input Low Voltage     | _    | _    | 0.8  | V    |

| TA  |      | Operating Temperature | -40  | _    | 85   | °C   |

#### NOTE:

1. 1.5V undershoots are allowed for 10ns once per cycle.

## **DC ELECTRICAL CHARACTERISTICS**

(Industrial:  $VCC = 5V \pm 10\%$ .  $TA = -40^{\circ}C$  to  $+85^{\circ}C$ )

| (inuustriai.       | VCC = 3V ± 10%, 1A = -40 C 10 +03 C)              |     | IDT72615L<br>IDT72605L<br>Industrial |     |                    |  |  |  |

|--------------------|---------------------------------------------------|-----|--------------------------------------|-----|--------------------|--|--|--|

| Symbol             | tclk = 20, 25, 35, 50ns  Parameter Min. Typ. Max. |     |                                      |     |                    |  |  |  |

| ILI <sup>(1)</sup> | Input Leakage Current (Any Input)                 |     | —                                    | 1   | <b>Unit</b><br>μ Α |  |  |  |

| ILO <sup>(2)</sup> | Output Leakage Current                            | -10 | _                                    | 10  | μA                 |  |  |  |

| Vон                | Output Logic "1" Voltage Iout = -2mA              | 2.4 | _                                    | _   | V                  |  |  |  |

| Vol                | Output Logic "0" Voltage IouT = 8mA               | _   | _                                    | 0.4 | V                  |  |  |  |

| Icc <sup>(3)</sup> | Active Power Supply Current                       | _   | _                                    | 230 | mA                 |  |  |  |

#### NOTES:

- 1. Measurements with  $0.4V \le VIN \le Vcc$ .

- 2.  $\overline{\text{OEA}}$ ,  $\overline{\text{OEB}} \ge \text{ViH}$ ;  $0.4 \le \text{Vout} \le \text{Vcc}$ .

- 3. Tested with outputs open (lout = 0). Testing frequency f=20MHz.

## **CAPACITANCE** (TA = +25°C, F = 1.0MHz)

| Symbol                | Parameter          | Conditions | Max. | Unit |

|-----------------------|--------------------|------------|------|------|

| CIN <sup>(2)</sup>    | Input Capacitance  | VIN = 0V   | 10   | pF   |

| COUT <sup>(1,2)</sup> | Output Capacitance | VOUT = 0V  | 10   | pF   |

- 1. With output deselected.

- 2. Characterized values, not currently tested.

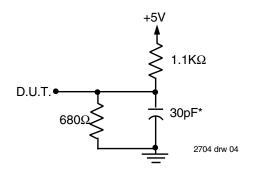

## **ACTEST CONDITIONS**

| In Pulse Levels               | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 3ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 2 |

or equivalent circuit Figure 2. Output Load

## **AC ELECTRICAL CHARACTERISTICS**

(Industrial: VCC =  $5V \pm 10\%$ , TA = -40°C to +85°C)

|             |                                                                | Industrial  |      |                  |      |                  |      |      |      |      |                                   |

|-------------|----------------------------------------------------------------|-------------|------|------------------|------|------------------|------|------|------|------|-----------------------------------|

|             |                                                                | IDT72615L20 |      |                  |      |                  |      |      |      |      |                                   |

| Symbol      | Parameter                                                      | Min.        | Max. | 101720<br>  Min. | Max. | 101720<br>  Min. | Max. | Min. | Max. | Unit | Timing Figures                    |

| fclk        | Clockfrequency                                                 | _           | 50   | _                | 40   | _                | 28   | _    | 20   | MHz  |                                   |

| tclk        | Clock cycle time                                               | 20          | _    | 25               | _    | 35               | _    | 50   |      | ns   | 4,5,6,7                           |

| tclkh       | Clock HIGH time                                                | 8           | _    | 10               | _    | 14               | _    | 20   |      | ns   | 4,5,6,7,12,13,14,15               |

| tclkl       | Clock LOW time                                                 | 8           | _    | 10               | _    | 14               | _    | 20   | _    | ns   | 4,5,6,7,12,13,14,15               |

| trs         | Reset pulse width                                              | 20          | _    | 25               | _    | 35               | _    | 50   | _    | ns   | 3                                 |

| trss        | Reset setup time                                               | 12          | _    | 15               | _    | 21               | _    | 30   | _    | ns   | 3                                 |

| trsr        | Reset recovery time                                            | 12          | _    | 15               | _    | 21               | _    | 30   | _    | ns   | 3                                 |

| trsf        | Reset to flags in initial state                                | _           | 27   | _                | 28   | _                | 35   | _    | 50   | ns   | 3                                 |

| tA          | Data access time                                               | 3           | 10   | 3                | 15   | 3                | 21   | 3    | 25   | ns   | 5,7,8,9,10,11                     |

| tcs         | Control signal setup time <sup>(1)</sup>                       | 6           | _    | 6                | _    | 8                | _    | 10   | _    | ns   | 4,5,6,7,8,9,10,11,<br>12,13,14,15 |

| tсн         | Control signal hold time <sup>(1)</sup>                        | 1           | _    | 1                | _    | 1                | _    | 1    | _    | ns   | 4,5,6,7,10,11,12,<br>13,14,15     |

| tos         | Data setup time                                                | 6           | _    | 6                | _    | 8                | _    | 10   |      | ns   | 4,6,8,9,10,11                     |

| <b>t</b> DH | Data hold time                                                 | 1           | _    | 1                | _    | 1                | _    | 1    | _    | ns   | 4,6                               |

| toe         | Output Enable LOW to output data valid <sup>(2)</sup>          | 3           | 10   | 3                | 13   | 3                | 20   | 3    | 28   | ns   | 5,7,8,9,10,11                     |

| tolz        | Output Enable LOW to data bus at Low-Z <sup>(2)</sup>          | 0           | _    | 0                | _    | 0                | _    | 0    | _    | ns   | 5,7,8,9,10,11                     |

| tohz        | Output Enable HIGH to data bus at High-Z <sup>(2)</sup>        | 3           | 10   | 3                | 13   | 3                | 20   | 3    | 28   | ns   | 5,7,10,11                         |

| tff         | Clock to Full Flag time                                        | _           | 10   | _                | 15   | _                | 21   | _    | 30   | ns   | 4,6,10,11                         |

| ter         | Clock to Empty Flag time                                       | _           | 10   | _                | 15   | _                | 21   | _    | 30   | ns   | 5,7,8,9,10,11                     |

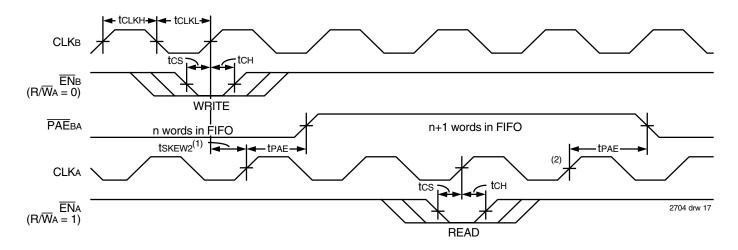

| tpae        | Clock to Programmable<br>Almost-Empty Flag time                | _           | 12   | _                | 15   | _                | 21   | _    | 30   | ns   | 12,14                             |

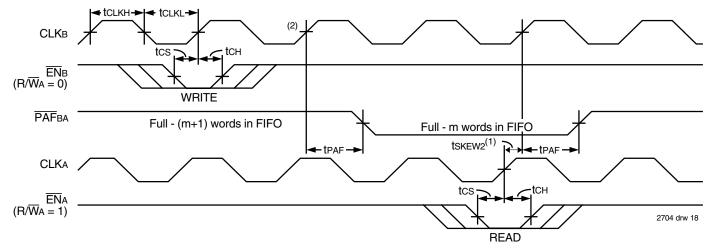

| tpaf        | Clock to Programmable<br>Almost-Full Flag time                 | _           | 12   | _                | 15   | _                | 21   | _    | 30   | ns   | 13,15                             |

| tskew1      | Skew between CLKA & CLKB for Empty/Full Flags <sup>(2)</sup>   | 10          | _    | 12               | _    | 17               | _    | 20   | _    | ns   | 4,5,6,7,8,9,10,11                 |

| tskew2      | Skew between CLKA & CLKB for Programmable Flags <sup>(2)</sup> | 17          | _    | 19               | _    | 25               | _    | 34   | _    | ns   | 4,7,12,13,14,15                   |

- Control signals refer to CSA, R/WA, ENA, A2, A1, A0, R/WB, ENB.

Minimum values are guaranteed by design.

<sup>\*</sup> Includes jig and scope capacitances.

#### **FUNCTIONAL DESCRIPTION**

IDTs SyncBiFIFO is versatile for both multiprocessor and peripheral applications. Data can be stored or retrieved from two sources simultaneously.

The SyncBiFIFO has registers on all inputs and outputs. Data is only transferred into the I/O registers on clock edges, hence the interfaces are synchronous. Two Dual-Port FIFO memory arrays are contained in the SyncBiFIFO; one data buffer for each direction. Each port has its own independent clock. Data transfers to the I/O registers are gated by the enable signals. The transfer direction for each port is controlled independently by a read/write signal. Individual output enable signals control whether the SyncBiFIFO is driving the data lines of a port or whether those data lines are in a high-impedance state. The processor connected to Port A of the BiFIFO can send or receive messages directly to the Port B device using the 18-bit bypass path.

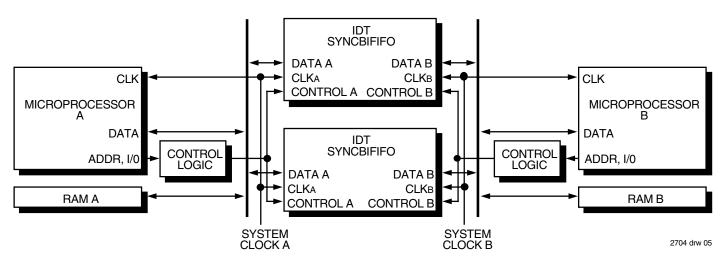

The SyncBiFIFO can be used in multiples of 18-bits. In a 36- to 36-bit configuration, two SyncBiFIFOs operate in parallel. Both devices are programmed simultaneously, 18 data bits to each device. This configuration can be extended to wider bus widths (54- to 54-bits, 72- to 72-bits, etc.) by adding more SyncBiFIFOs to the configuration. Figure 1 shows multiple SyncBiFIFOs configured for multiprocessor communication.

The microprocessor or microcontroller connected to Port A controls all operations of the SyncBiFIFO. Thus, all Port A interface pins are inputs driven by the controlling processor. Port B interfaces with a second processor. The Port B control pins are inputs driven by the second processor.

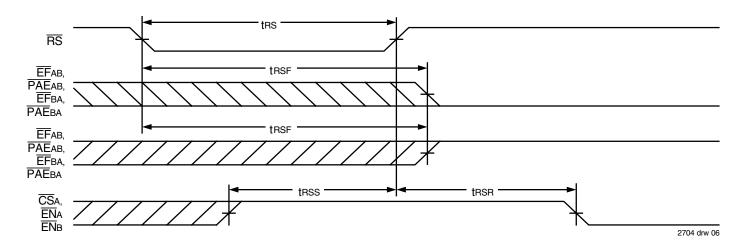

#### **RESET**

Reset is accomplished whenever the Reset ( $\overline{RS}$ ) input is taken to a LOW state with  $\overline{CS}A$ ,  $\overline{EN}A$  and  $\overline{EN}B$  HIGH. During reset, both internal read and write pointers are set to the first location. A reset is required after power up before a write operation can take place. The A $\rightarrow$ B and B $\rightarrow$ A FIFO Empty Flags ( $\overline{EF}AB$ ,  $\overline{EF}BA$ ) and Programmable Almost-Empty flags ( $\overline{PAE}AB$ ,  $\overline{PAE}BA$ ) will be set to LOW after tRSF. The A $\rightarrow$ B and B $\rightarrow$ A FIFO Full Flags ( $\overline{FF}AB$ ,  $\overline{FF}BA$ ) and Programmable Almost-Full flags ( $\overline{PAF}AB$ ,  $\overline{PAF}BA$ ) will be set to HIGH after tRSF. After the reset, the offsets of the Almost-Empty flags and Almost-Full flags for the A $\rightarrow$ B and B $\rightarrow$ A FIFO offset default to 8.

#### **PORT A INTERFACE**

The SyncBiFIFO is straightforward to use in micro-processor-based systems because each port has a standard microprocessor control set. Port A interfaces with microprocessor through the three address pins (A2-A0) and a Chip Select  $\overline{CSA}$  pins. When  $\overline{CSA}$  is asserted, A2,A1,A0 and R/ $\overline{WA}$  are used to select one of six internal resources (Table 1).

With A2=0 and A1=0, A0 determines whether data can be read out of output register or be written into the FIFO (A0=0), or the data can pass through the FIFO through the bypass path (A0=1).

With A2=1, four programmable flags (two A $\rightarrow$ B FIFO programmable flags and two B $\rightarrow$ A FIFO programmable flags) can be selected: the A $\rightarrow$ B FIFO Almost-Empty flag Offset (A1=0, A0=0), A $\rightarrow$ B FIFO Almost-Full flag Offset (A1=0, A0=1), B $\rightarrow$ A FIFO Almost-Empty flag Offset (A1=1, A0=0), B $\rightarrow$ A FIFO Almost-Full flag Offset (A1=1, A0=1).

Port A is disabled when CSA is deasserted and data A is in high-impedance state.

#### **BYPASS PATH**

The bypass paths provide direct communication between Port A and Port B. There are two full 18-bit bypass paths, one in each direction. During a bypass operation, data is passed directly between the input and output registers, and the FIFO memory is undisturbed.

Port A initiates and terminates all bypass operations. The bypass flag,  $\overline{BYP}B$ , is asserted to inform Port B that a bypass operation is beginning. The bypass flag state is controlled by the Port A controls, although the  $\overline{BYP}B$  signal is synchronized to CLKB. So,  $\overline{BYP}B$  is asserted on the next rising edge of CLKB when A2A1A0=001 and CSa is LOW. When Port A returns to normal FIFO mode (A2A1A0=000 or CSa is HIGH),  $\overline{BYP}B$  is deasserted on the next CLKB rising edge.

Once the SyncBiFIFO is in bypass mode, all data transfers are controlled by the standard Port A (R/ $\overline{W}$ A, CLKA,  $\overline{E}$ NA,  $\overline{O}\overline{E}$ A) and Port B (R/ $\overline{W}$ B, CLKB,  $\overline{E}$ NB,  $\overline{O}\overline{E}$ B) interface pins. Each bypass path can be considered as a one word deep FIFO. Data is held in each input register until it is read. Since the controls

- 1. Upper SyncBiFIFO only is used in 18- to 18-bit configuration.

- 2. Control A consists of R/WA, ENA, OEA, CSA, A2, A1, A0. Control B consists of R/WB, ENB, OEB.

Figure 1. 36- to 36-bit Processor Interface Configuration

#### TABLE 1 — PORT A OPERATION CONTROL SIGNALS

|     |      |     |     | Data A |                                                                                                                                                                                                                                                                                             |

|-----|------|-----|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSA | R/WA | ΕNA | ŌĒA | I/O    | Port A Operation                                                                                                                                                                                                                                                                            |

| 0   | 0    | 0   | 0   | I      | Data A is written on CLKa $\neq$ . This write cycle immediately following low-impedance cycle is prohibited. Note that even though $\overline{OE}_A = 0$ , a LOW logic level on R/ $\overline{W}_A$ , once qualified by a rising edge on CLKa, will put Data A into a high-impedance state. |

| 0   | 0    | 0   | 1   | I      | Data A is written on CLKA ≠                                                                                                                                                                                                                                                                 |

| 0   | 0    | 1   | Χ   |        | Data A is ignored                                                                                                                                                                                                                                                                           |

| 0   | 1    | 0   | 0   | 0      | Data is read <sup>(1)</sup> from RAM array to output register on CLKa ≠, Data A is low-impedance                                                                                                                                                                                            |

| 0   | 1    | 0   | 1   | 0      | Data is read <sup>(1)</sup> from RAM array to output register on CLKa ≠, Data A is high-impedance                                                                                                                                                                                           |

| 0   | 1    | 1   | 0   | 0      | Output register does not change (2), Data A is low-impedance                                                                                                                                                                                                                                |

| 0   | 1    | 1   | 1   | 0      | Output register does not change <sup>(2)</sup> , Data A is high-impedance                                                                                                                                                                                                                   |

| 1   | 0    | Х   | Х   | I      | Data A is ignored <sup>(3)</sup>                                                                                                                                                                                                                                                            |

| 1   | 1    | Χ   | Х   | 0      | Data A is high-impedance <sup>(3)</sup>                                                                                                                                                                                                                                                     |

#### NOTES:

- 1. When A2A1A0 = 000, the next B→A FIFO value is read out of the output register and the read pointer advances. If A2A1A0 = 001, the bypass path is selected and bypass data from the Port B input register is read from the Port A output register. If A2A1A00 = 1XX, a flag offset register is selected and its offset is read out through Port A output register.

- 2. Regardless of the condition of A2A1A0, the data in the Port A output register does not change and the B-A read pointer does not advance.

- 3. If CSA# is HIGH, then BYPB is HIGH. No bypass occur under this condition.

of each port operate independently, Port A can be reading bypass data at the same time Port B is reading bypass data.

When  $R/\overline{W}A$  and  $\overline{EN}A$  is LOW, data on pins DA0-DA17 is written into Port A input register. Following the rising edge of CLKA for this write, the  $A \rightarrow B$  Full Flag ( $\overline{F}FAB$ ) goes LOW. Subsequent writes into Port A are blocked by internal logic until  $\overline{F}FAB$  goes HIGH again. On the next CLKB rising edge, the  $A \rightarrow B$  Empty Flag ( $\overline{E}FAB$ ) goes HIGH indicating to Port B that data is available. Once  $R/\overline{W}B$  is HIGH and  $\overline{E}NB$  is LOW, data is read into the Port B output register.  $\overline{OE}B$  still controls whether Port B is in a high-impedance state. When  $\overline{OE}B$  is LOW, the output register data appears at DB0-DB17.  $\overline{E}FAB$  goes LOW following the CLKB rising edge for this read. FFAB goes HIGH on the next CLKA rising edge, letting Port A know that another word can be written through the bypass path.

By pass data transfers from Port B to Port A work in a similar manner with  $\overline{\text{EFB}}$ A and  $\overline{\text{FFB}}$ A indicating the Port A output register state.

When the Port A address changes from bypass mode (A2A1A0=001) to FIFO mode (A2A1A0=000) on the rising edge of CLKa, the data held in the Port B output register may be overwritten. Unless Port A monitors the  $\overline{BYP}B$  pin and waits for Port B to clock out the last bypass word, data from the A $\rightarrow$ B FIFO will overwrite data in the Port B output register.  $\overline{BYP}B$  will go HIGH on the rising edge of CLKB signifying that Port B has finished its last bypass operation. Port B must read any bypass data in the output register on this last CLKB clock or it is lost and the SyncBiFIFO returns to FIFO operations. It is especially important to monitor  $\overline{BYP}B$  when CLKB is much slower than CLKA to avoid this condition.  $\overline{BYP}B$  will also go HIGH after  $\overline{CS}A$  is brought HIGH; in this manner the Port B bypass data may also be lost.

Since the Port A processor controls  $\overline{CS}$ A and the bypass mode, this scenario can be handled for B $\to$ A bypass data. The Port A processor must be set up to read the last bypass word before leaving bypass mode.

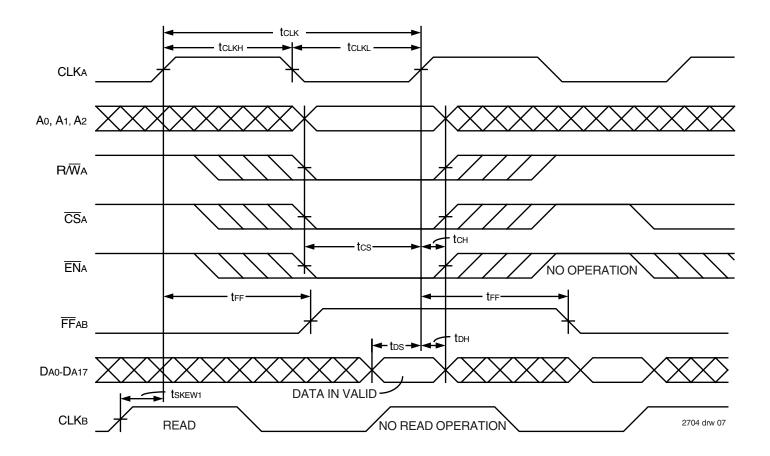

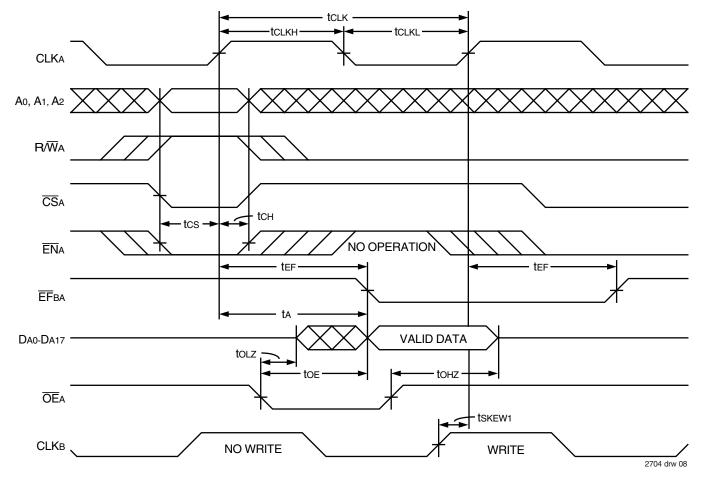

#### PORT A CONTROL SIGNALS

The Port A control signals pins dictate the various operations shown in Table 2. Port A is accessed when  $\overline{CS}$ A is LOW, and is inactive if  $\overline{CS}$ A is HIGH. R/ $\overline{W}$ A and  $\overline{EN}$ A lines determine when Data A can be written or read. If R/ $\overline{W}$ A and  $\overline{EN}$ A are LOW, data is written into input register on the LOW-to-HIGH transition of CLKA. If R/ $\overline{W}$ A is HIGH and  $\overline{OE}$ A is LOW, data comes out of bus and is read from output register into three-state buffer. Refer to pin descriptions for more information.

## TABLE 2—ACCESSING PORT A RE-SOURCES USING CSA, A2, A1, AND A0

| CSA | <b>A</b> 2 | <b>A</b> 1 | A <sub>0</sub> | Read                                | Write     |  |  |  |  |

|-----|------------|------------|----------------|-------------------------------------|-----------|--|--|--|--|

| 0   | 0          | 0          | 0              | B→A FIFO                            | A→B FIFO  |  |  |  |  |

| 0   | 0          | 0          | 1              | 18-bit Byr                          | oass Path |  |  |  |  |

| 0   | 1          | 0          | 0              | 3:                                  |           |  |  |  |  |

| 0   | 1          | 0          | 1              | A→B FIFO Almost-Full<br>Flag Offset |           |  |  |  |  |

| 0   | 1          | 1          | 0              | B→A FIFO <i>F</i><br>Flag(          |           |  |  |  |  |

| 0   | 1          | 1          | 1              | B→A FIFO Almost-Full<br>Flag Offset |           |  |  |  |  |

| 1   | Х          | Х          | Х              |                                     |           |  |  |  |  |

#### **PROGRAMMABLE FLAGS**

The IDT SyncBiFIFO has eight flags: four flags for A→B FIFO (ĒFAB, PĀĒAB, PĀFAB, FFAB), and four flags for B→A FIFO (ĒFBA, PĀĒBA, PĀFBA, FFBA). The Empty and Full flags are fixed, while the Almost-Empty and Almost-Full offsets can be set to any depth through the Flag Offset Registers (see Table 3). The flags are asserted at the depths shown in the Flag Truth Table (Table 4). After reset, the programmable flag offsets are set to 8. This means the Almost-Empty flags are asserted at Empty +8 words deep, and the Almost-Full flags are asserted at Full -8 words deep.

The  $\overline{PAE}$ AB is synchronized to CLKB, while  $\overline{PAE}$ AB is synchronized to CLKA; and  $\overline{PAE}$ BA is synchronized to CLKA, while  $\overline{PAE}$ BA is synchronized to CLKB. If the minimum time (tskew2) between a rising CLKB and a rising CLKA is met, the flag will change state on the current clock; otherwise, the flag may not change state until the next clock rising edge. For the specific flag timings, refer to Figures 12-15.

#### PORT B CONTROL SIGNALS

The Port B control signal pins dictate the various operations shown in Table 5. Port B is independent of  $\overline{CSA}$ . R/ $\overline{WB}$  and  $\overline{ENB}$  lines determine when Data

can be written or read in Port B. If  $R/\overline{W}B$  and  $\overline{EN}B$  are LOW, data is written into input register, and on LOW-to-HIGH transition of CLKB data is written into input register and the FIFO memory. If  $R/\overline{W}B$  is HIGH and  $\overline{OE}B$  is LOW, data comes out of bus and is read from output register into three-state buffer. In bypass mode,

if R/ $\overline{W}$ B is LOW, bypass messages are transferred into B $\rightarrow$ A output register. If R/ $\overline{W}$ A is HIGH, bypass messages are transferred into A $\rightarrow$ B output register. Refer to pin descriptions for more information.

#### TABLE 3—FLAG OFFSET REGISTER FORMAT

|                            | 17 | 16 | 15       | 14  | 13 | 12 | 11 | 10 | 9      | 8   | 7 | 6         | 5       | 4        | 3         | 2        | 1 | 0 |

|----------------------------|----|----|----------|-----|----|----|----|----|--------|-----|---|-----------|---------|----------|-----------|----------|---|---|

| PAEAB Register             | Χ  | Х  | Х        | Х   | Χ  | Χ  | Χ  | Χ  | Χ      |     |   | A→B F     | IFO Alm | nost-Em  | npty Flag | g Offset |   |   |

|                            | 17 | 16 | 15       | 14  | 13 | 12 | 11 | 10 | Q      | Q   | 7 | 6         | 5       | 1        | 2         | 2        | 1 | 0 |

| PAFAB Register             |    | Ιχ | <u>ы</u> | l v | X  | X  | V  | Y  | 7<br>Y | 0   |   | 0<br>Δ_∠R | FIFO AI | most-Fi  | ull Flan  | Offsat   |   |   |

| TALAB REGISIEL             |    |    | _ ^      | _ ^ | ^  | ^  | ٨  | ٨  | ٨      |     |   | А→В       | IIIOAI  | 111031-1 | uli i iay | Oliset   |   |   |

|                            | 17 | 16 | 15       | 14  | 13 | 12 | 11 | 10 | 9      | 8   | 7 | 6         | 5       | 4        | 3         | 2        | 1 | 0 |

| PAE <sub>BA</sub> Register | Χ  | Х  | Х        | Х   | Χ  | Χ  | Χ  | Χ  | Χ      |     |   | B→A F     | IFO Alm | nost-Em  | npty Flag | g Offset |   |   |

|                            |    |    |          |     |    |    |    |    |        |     |   |           |         |          |           |          |   |   |

|                            | 17 | 16 | 15       | 14  | 13 | 12 | 11 | 10 | 9      | - 8 | 7 | 6         | 5       | 4        | 3         | 2        | 1 | 0 |

| PAFBA Register             | Χ  | Х  | Х        | Х   | Χ  | Χ  | Χ  | Χ  | Χ      |     |   | В→А       | FIFO AI | most-F   | ull Flag  | Offset   |   |   |

#### NOTE:

### **TABLE 4 — INTERNAL FLAG TRUTH TABLE**

| 1    | of Words<br>IFO |      |      |      |      |

|------|-----------------|------|------|------|------|

| From | To              | ĒĒ   | PAE  | PAF  | FF   |

| 0    | 0               | LOW  | LOW  | HIGH | HIGH |

| 1    | n               | HIGH | LOW  | HIGH | HIGH |

| n+1  | D-(m+1)         | HIGH | HIGH | HIGH | HIGH |

| D-m  | D-1             | HIGH | HIGH | LOW  | HIGH |

| D    | D               | HIGH | HIGH | LOW  | LOW  |

#### NOTE:

### TABLE 5—PORT B OPERATION CONTROL SIGNALS

| R/W̄B | <b>EN</b> B | <b>ŌĒ</b> B | Data B<br>I/O | Port B Operation                                                                                                                                                                                                                                                                                                                       |

|-------|-------------|-------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0           | 0           | I             | Data B is written on CLKB $\uparrow$ . This write cycle immediately following output low-impedance cycle is prohibited. Note that even though $\overline{\text{OE}}_{\text{B}} = 0$ , a LOW logic level on R/ $\overline{\text{W}}_{\text{B}}$ , once qualified by a rising edge on CLKB, will put Data B into a high-impedance state. |

| 0     | 0           | 1           | I             | Data B is written on CLKB ↑.                                                                                                                                                                                                                                                                                                           |

| 0     | 1           | Χ           | I             | Data B is ignored                                                                                                                                                                                                                                                                                                                      |

| 1     | 0           | 0           | 0             | Data is read <sup>(1)</sup> from RAM array to output register on CLKB ≠ Data B is low-impedance                                                                                                                                                                                                                                        |

| 1     | 0           | 1           | 0             | Data is read <sup>(1)</sup> from RAM array to output register on CLKB ≠, Data B is high- impedance                                                                                                                                                                                                                                     |

| 1     | 1           | 0           | 0             | Output register does not change <sup>(2)</sup> , Data B is low-impedance                                                                                                                                                                                                                                                               |

| 1     | 1           | 1           | 0             | Output register does not change <sup>(2)</sup> , Data B is high-impedance                                                                                                                                                                                                                                                              |

<sup>1.</sup> Bit 8 must be set to 0 for the IDT72605 (256 x 18) Synchronous BiFIFO.

<sup>1.</sup> n = Programmable Empty Offset (PAEAB Register or PAEBA Register)

m = Programmable Full Offset (PAFAB Register or PAFBA Register)

D = FIFO Depth (IDT72605 = 256 words, IDT72615= 512 words)

<sup>1.</sup> When A<sub>2</sub>A<sub>1</sub>A<sub>0</sub> = 000 or 1XX, the next A $\rightarrow$ B FIFO value is read out of the output register and the read pointer advances. If A<sub>2</sub>A<sub>1</sub>A<sub>0</sub> = 001, the bypass path is selected and bypass data is read from the Port B output register.

<sup>2.</sup> Regardless of the condition of A₂A₁A₀, the data in the Port B output register does not change and the A→B read pointer does not advance.

Figure 3. Reset Timing

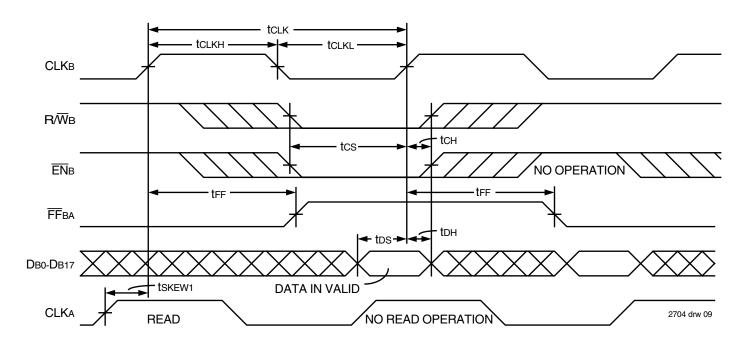

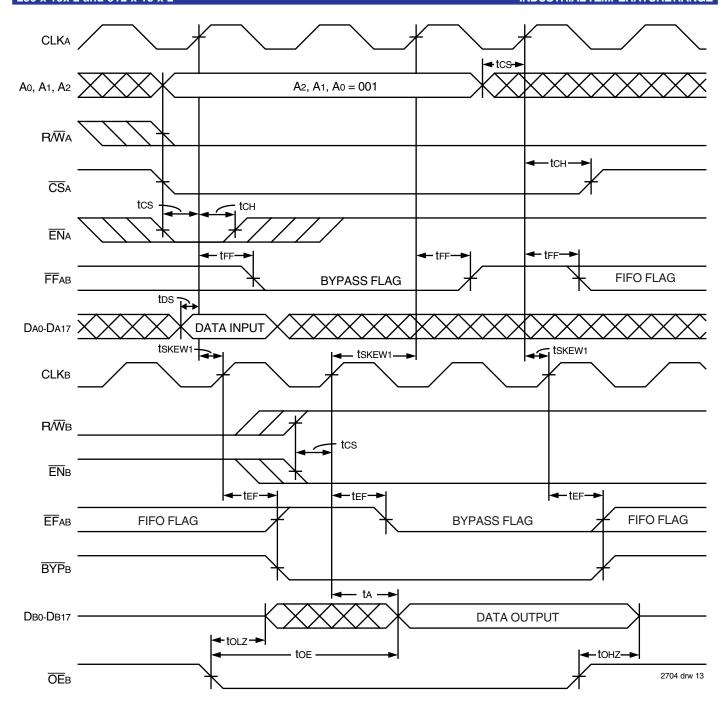

Figure 4. Port A (A→B) Write Timing

Figure 5. Port A (B→A) Read Timing

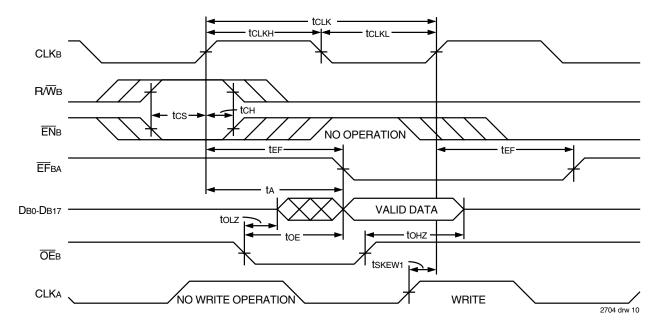

Figure 6. Port B (B→A) Write Timing

Figure 7. Port B (A→B) Read Timing

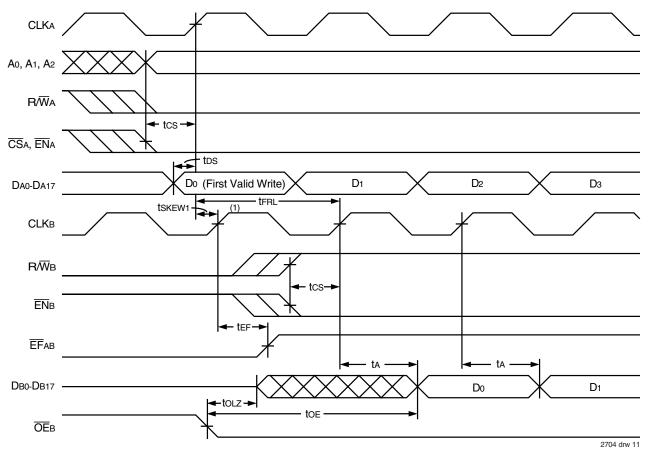

1. When tskew1 ≥ minimum specification, tfrL(Max.) = tclk + tskew1 tskew1 < minimum specification, tfrL(Max.) = 2tclk + tskew1 or tclk + tskew1

The Latency Timing applies only at the Empty Boundary (EF = LOW).

Figure 8. A→B First Data Word Latency after Reset for Simultaneous Read and Write

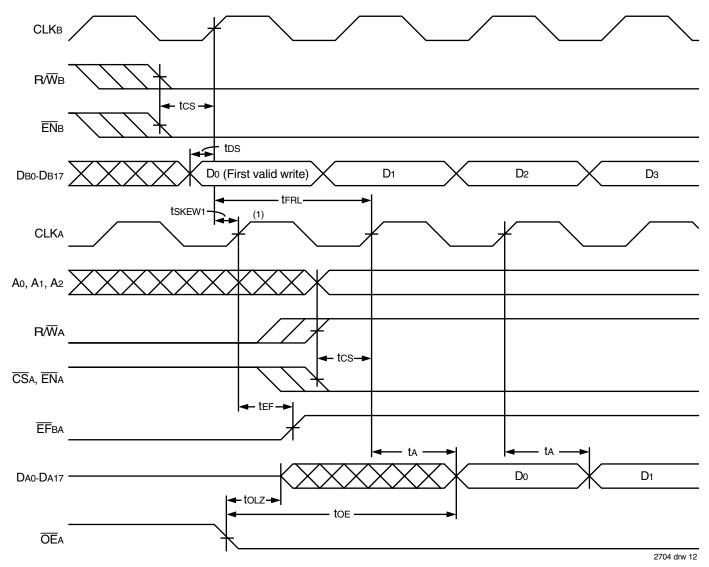

When tskew1 ≥ minimum specification, tFRL(Max.) = tclk + tskew1 tskew1 < minimum specification, tFRL(Max.) = 2tclk + tskew1 The Latency Timing apply only at the Empty Boundary (EF = LOW).

Figure 9. B→A First Data Word Latency after Reset for Simultaneous Read and Write

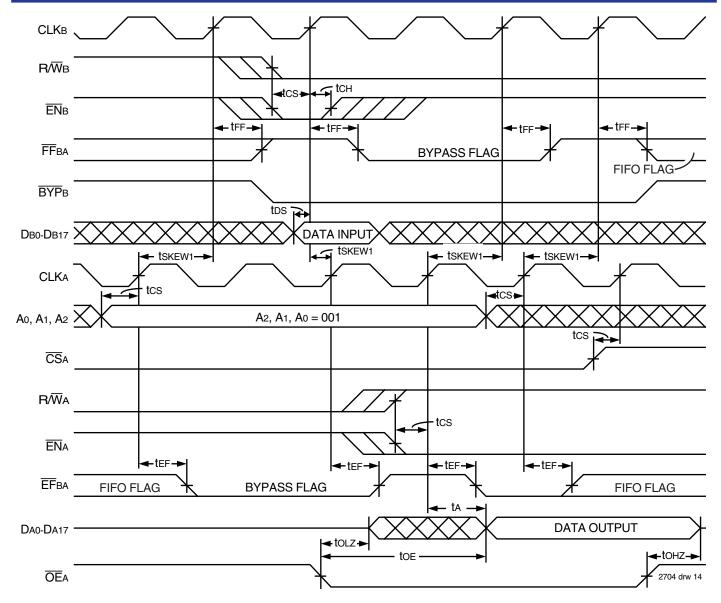

- 1. When <del>CS</del>A is brought HIGH, A→B Bypass mode will switch to FIFO mode on the following CLKA LOW-to-HIGH transition.

- 2. After the bypass operation is completed, the BYPB goes from LOW-to-HIGH; this will reset all bypass flags. The bypass path becomes available for the next bypass operation.

- 3. When A-side changed from bypass mode into FIFO mode, B-side only has one cycle to read the bypass data. On the next cycle, B-side will be forced back to FIFO mode.

Figure 10. A→B Bypass Timing

- 1. When CSA is brought HIGH, A→B Bypass mode will switch to FIFO mode on the following CLKA going LOW-to-HIGH.

- 2. After the bypass operation is completed, the BYPB goes from LOW-to-HIGH; this will reset all bypass flags.

- 3. When A-side changed from bypass mode into FIFO mode, B-side only has one cycle to read the bypass data. On the next cycle, B-side will be forced back to FIFO mode.

Figure 11. B→A Bypass Timing

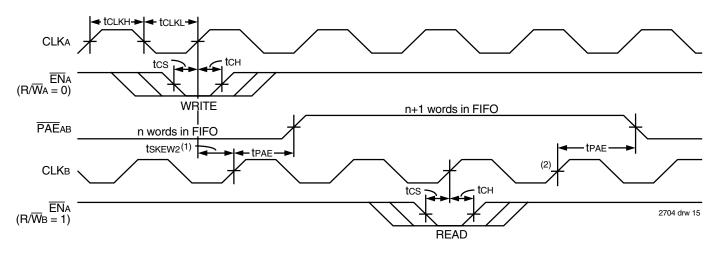

- 1. tskewz the minimum time between a rising CLKa edge and a rising CLKa edge for PAEaB to change during that clock cycle. If the time between the rising edge of CLKa and the rising edge of CLKB is less than tskew, then PAEAB may not go HIGH until the next CLKB rising edge.

2. If a read is performed on this rising edge of the read clock, there will be Empty + (n + 1) words in the FIFO when PAE goes LOW.

Figure 12. A→B Programmable Almost-Empty Flag Timing

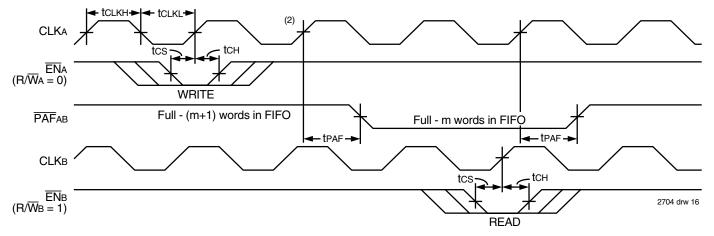

- 1. tskewz is the minimum time between a rising CLKB edge and a rising CLKA edge for PAFAB to change during that clock cycle. If the time between the rising edge of CLKB and the rising edge of CLKA is less than tskew2, then PAFAB may not go HIGH until the next CLKA rising edge.

- 2. If a write is performed on this rising edge of the write clock, there will be Full (m + 1) words in the FIFO when PAF goes LOW.

Figure 13. A→B Programmable Almost-Full Flag Timing

- 1. tskewz is the minimum time between a rising CLKa edge and a rising CLKa edge for PAEba to change during that clock cycle. If the time between the rising edge of CLKa and the rising edge of CLKa is less than tskewz, then PAEba may not go HIGH until the next CLKa rising edge.

- 2. If a read is performed on this rising edge of the read clock, there will be Empty + (n 1) words in the FIFO when PAE goes LOW.

Figure 14. B→A Programmable Almost-Empty Flag Timing

- 1. tskew2 is the minimum time between a rising CLKa edge and a rising CLKa edge for PAFBA to change during that clock cycle. If the time between the rising edge of CLKa and the rising edge of CLKa is less than tskew2, then PAFBA may not go HIGH until the next CLKa rising edge.

- 2. If a write is performed on this rising edge of the write clock, there will be Full (m + 1) words in the FIFO when PAF goes LOW.

Figure 15. B→A Programmable Almost-Full Flag Timing

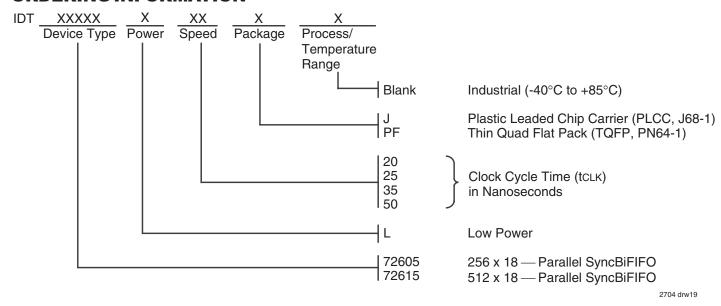

#### **ORDERING INFORMATION**

## **DATASHEET DOCUMENT HISTORY**

pgs. 1, 2, 3, 4, 16 11/02/2000 04/08/2003 pg. 17.

**CORPORATE HEADQUARTERS**

2975 Stender Way Santa Clara, CA 95054 for SALES:

800-345-7015 or 408-727-6116 fax: 408-492-8674

www.idt.com

for Tech Support: 408-330-1753 email: FIFOhelp@idt.com