# Mobile Pentium<sup>®</sup> Processor with MMX<sup>TM</sup> Technology on 0.25 Micron System Design Considerations

#### **MHPG Technical Marketing**

1/98

243571-002

## Legal Disclaimers

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The mobile Pentium(R) processor with MMX(TM) Technology may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

MPEG is an international standard for video compression/decompression promoted by ISO. Implementations of MPEG CODECs, or MPEG enabled platforms may require licenses from various entities, including Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com

Copyright © Intel Corporation1997. Third-party brands and names are the property of their respective owners.

## **Topics**

- Overview and Differences Between Mobile Pentium(R) Processor with MMX<sup>TM</sup> Technology on 0.25 Micron<sup>(1)</sup> (166/200/233/266 MHz) and P55CLM<sup>(2)</sup> (133/150/166 MHz)

- Voltage Supply Solution

- Thermal Design Considerations

- I/O Signals

- o Packaging

- Key Validation Areas

- **o** Platform Readiness Summary

- o Collateral

Notes:

1. Mobile PPMT on 0.25 Micron is Mobile Pentium(R) Processor with MMX(TM) Technology on 0.25 Micron 2. P55CLM is Mobile Pentium(R) Processor with MMX  $^{TM}$  Technology.

### **Overview**

• This presentation covers hardware design considerations for the Mobile Pentium(R) Processor with MMX<sup>TM</sup> Technology on 0.25 Micron at (166/200/233/266 MHz).

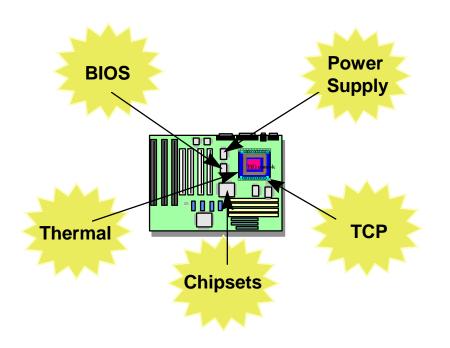

## Mobile Pentium(R) Processor with MMX<sup>TM</sup> Technology on 0.25 Micron Platform Block Diagram

#### Summary of Differences Between the Mobile Pentium(R) Processor with MMX<sup>TM</sup> Technology on 0.25 Micron and P55CLM

|   |                          | <u>P55CLM</u>               | Mobile PPMT on 0.25 Micron                                                             | OEM Impact                               |

|---|--------------------------|-----------------------------|----------------------------------------------------------------------------------------|------------------------------------------|

| 0 | Vcc2 (core)              | 2.45V + 0.215V<br>/- 0.165V | $\begin{array}{l} 1.8V \pm 0.135V(166\text{-}233) \\ 2.0V \pm 0.150V(266) \end{array}$ | Power Supply Design Re-qualification     |

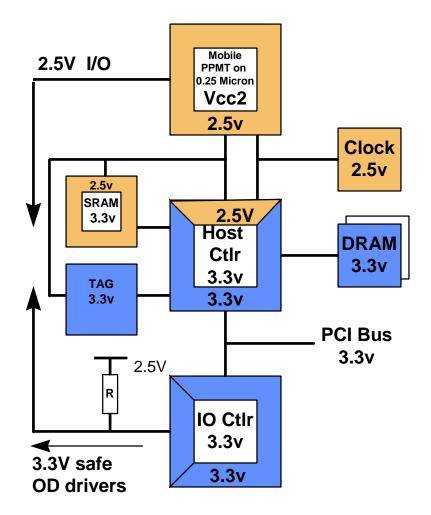

| 0 | Vcc3 (I/O)               | $3.3V \pm 5\%$              | $2.5V \pm 5\%$                                                                         | Power Supply Design Re-qualification     |

| 0 | <b>Power Dissipation</b> |                             |                                                                                        |                                          |

|   | - TDP (max)              | 9.0W @ 166 MHz              | 7.6W @ 266 MHz                                                                         | Possible Thermal Impact                  |

|   | - Auto-halt (max)        | 1.0W @ 166 MHz              | 0.71W @ 266 MHz                                                                        |                                          |

|   | - Stopclk (max)          | 50mW                        | 62mW @ 266 MHz                                                                         |                                          |

| 0 | Signal Levels            | 3.3V                        | 2.5V                                                                                   | "New" Clock Design                       |

|   | (inc'l clocks)           |                             |                                                                                        | L2 Cache [PBSRAM]                        |

| 0 | <b>Bus:Core Ratio</b>    |                             | 2/7 & 1/4 ratio added                                                                  | Extended product offering                |

| 0 | Pinout                   |                             | BF2, PICD0-1, PICCLK                                                                   | Layout Change                            |

|   |                          |                             | pins added                                                                             |                                          |

| 0 | CPUID                    | <b>04H</b>                  | 08H                                                                                    | BIOS Change                              |

| 0 | Packaging                | TCP/PPGA                    | TCP/Mobile Module                                                                      | Package Migration                        |

|   |                          |                             |                                                                                        |                                          |

| 0 | Die Size                 | DL=12.855 mm                | DL=10.450 mm                                                                           | <b>Re-qual Thermals &amp; Die Attach</b> |

|   |                          | DW=11.105 mm                | DW=9.088 mm                                                                            |                                          |

| 0 | Process Technology       | 0.35 um                     | 0.25 um                                                                                | Lower Vcc/Power Dissipation              |

|   |                          |                             |                                                                                        |                                          |

# Vcc2/Vcc3 Voltage Supply

#### • Vcc Specs

|      | Min<br>Voltage   | Max<br>Voltage   | Tolerance                                                  |

|------|------------------|------------------|------------------------------------------------------------|

| Vcc3 | 2.375V           | 2.625V           | 2.5V +/- 0.125V                                            |

| Vcc2 | 1.665V<br>1.850V | 1.935V<br>2.150V | 1.8V +/- 0.135V (166-233 MHz)<br>2.0V +/- 0.150V (266 MHz) |

#### o Sequencing

- u No specific sequence required for the Mobile PPMT on 0.25 Micron CPU

- u It is recommended that Vcc2 and Vcc3 power supplies be either both ON or both OFF within 1 second of each other.

- u Other platform elements (such as chipset, SRAM,...) may require a specific dual supply voltage sequence; consult vendor specifications

- u 430TX has a specific sequence; consult specification

- Keep power supply design flexible to accommodate processor requirements

- u Vcc2 should be able to adjust between 1.8 and 2.0V

- u Vcc2 should be adjustable independent of Vcc3

## Capacitive Decoupling

#### • Bulk Cap Recommendations (assumes 0.1 Ohm ESR caps)

- u 166/66 MHz: (Vcc\_core = 1.8V + 0.135V)

- ã Vcc2: 2x 100uF, 2x 220uF Tantalums with 300KHz switching regulator

- ã Vcc3: 1x 33uF

- u 200/66 MHz: (Vcc\_core = 1.8V + 0.135V)

- ã Vcc2: 2x 100uF, 2x 220uF Tantalums with 300KHz switching regulator

- ã Vcc3: 1x 33uF

- u 233/66 MHz: (Vcc\_core = 1.8V + -0.135V)

- ã Vcc2: 3x 100uF, 2x 220uF Tantalums with 300KHz switching regulator

- ã Vcc3: 1x 47uF

- u 266/66 MHz: (Vcc\_core = 2.0V + 0.150V)

- ã Vcc2: 7x 220uF (or 5x 220uF/ESR=0.07 Ohms) Tantalums with 300KHz switching regulator

- ã Vcc3: 1x 100uF

#### • High Frequency Decoupling

- u Use multiple 0.1uF and 0.01uF bypass caps

- Capacitive decoupling must be verified for each design to guarantee Vcc spec compliance

- u Designing in margin today will avoid redesigns for future processors

- u Excel\* Worksheet available to help assess your CPU decoupling cap values

- Consult with your power supply vendor for the exact values of decoupling needed for specific designs

## Thermal Design Power Definitions

#### • Thermal Design Power (Max)

- u Usage This value should be used for system thermal design. Systems must be designed to thermally dissipate this level of power as a steady state condition while keeping the CPU temperature in spec.

- u Definition Maximum power dissipation under normal operating conditions (no pins shorted together, etc.) at nominal Vcc, worst case temperature, while executing the worst case power instruction mix.

#### • Thermal Design Power (Typical)

- u Usage This value can be used for system thermal design. System thermal design may either meet the thermal design maximum spec or provide a thermal feedback fail safe mechanism in case CPU power consumption exceeds the thermal design typical spec for prolonged periods.

- u Definition Power dissipation based on the average and peak power of real applications under normal operating conditions (no pins shorted together, etc.) at nominal Vcc and room temperature.

## **Thermal Design Power**

• Thermal design also needs to be flexible to handle Vcc2 requirements

| Frequency | 166MHz       | 200MHz | 233MHz       | 266MHz |

|-----------|--------------|--------|--------------|--------|

| Vcc2      | 1.8V         | 1.8V   | 1.8V         | 2.0V   |

| Vcc3      | 2.5V         | 2.5V   | 2.5V         | 2.5V   |

| TDP max   | <b>4.1W</b>  | 5.0W   | 5.5W         | 7.6W   |

| TDP typ   | <b>2.9</b> W | 3.4W   | <b>3.9</b> W | 5.3W   |

• All TDP numbers are validated with silicon

# **Thermal Design Considerations**

#### • Specification Summary

- u Thermal resistance

- $\tilde{a}$  TCP Theta JC without enhancements = 0.8 deg. C/W

- u Max Tcase

- ã 95C for TCP

#### • Measure processor power when measuring thermals

- u Will help calibrate Mobile PPMT on 0.25 Micron power vs. OEM's existing CPU designs (P55CLM, P54CSLM, or P54LM)

- u NB CPU Power Measurement Method and Thermal Implications white paper available to assist in determing thermal performance

#### • Thermal design for TDP (typ)

- u Disable Power Management while running thermal tests

- u Run application

- ã Prime95

- ã DEP

- u Conduct the test for at least 3 hours

- u Ensure that rest of the system component temperatures are within component specs

- ã HDD, FDD, CD-ROM, SRAM, chipset etc.

#### • Maximize Tcase margin for possible future processors

u Will save future rework

# I/O Signals

• All I/O signals are 2.5V tolerant only (not 3.3V)

#### • Clock Levels

- u CLK, PICCLK, TCK require 2.5V signals

- u Clock buffers are not 3.3V tolerant

- u Refer to CKDM-66M Specifications (Version 1.1, doc#: SC 2063)

#### **o** Clock Undershoot/Overshoot specifications

- u Refer to Mobile PPMT on 0.25 Micron datasheets (Order number: 243468-001) page 53-54 (Table 21-22) for Overshoot/Undershoot specifications

- u Reduce as much as possible while still meeting rise/fall time

#### **o** Timing Margins

- u 66MHz AC bus timings slightly different between P55CLM and Mobile PPMT on 0.25 Micron

- a Min and Max Valid Delays affected

- ã Vil max also affected

- u Design for maximum system timing margins

- u System timing margins are a function of CPU valid delays, clock skews, flight times, and chipset setup/hold times (see next slide)

- u Flight times minimization can be accomplished with:

- a Optimized layout design (minimizing trace lengths/routing, etc.)

- ã I/O simulations using appropriate buffer models for CPU/chipset/SRAMs

- ã I/O buffer modeling (available in EDS Rev. 2.0)

- ã Linear IBIS modeling (available on request)

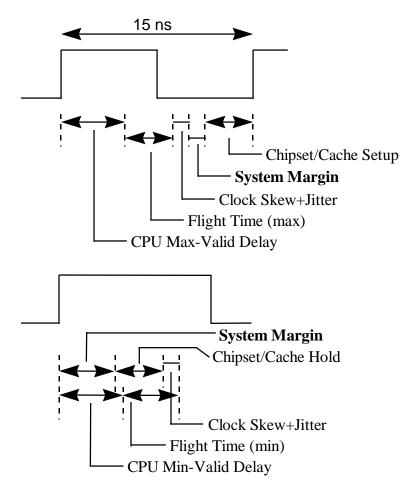

# I/O Signals (Cont'd)

• Timing Margins (66MHz example)

#### • CPU Max-Valid Delay

- u CPU Max-VD increases

- u Flight time and Clock skew are approximately constant

- u Chipset/cache setup times and system margin stressed

System Margin = 15 - (CPU Max-VD + Flt time + Clk skew + Chipset setup)

#### v CPU Min-Valid Delay

- u CPU Min-VD decreases

- u Flight time and Clock skew are approximately constant

- u Chipset/cache hold times and system margin stressed

System Margin = (CPU Min-VD + Flt time) -(Clk skew + Chipset hold)

# I/O Signals (Cont'd)

#### • Vil (max) Change

- u Due to reduced Vcc,  $V_{IL max} = 0.5V$

- u SRAMs spec'd to handle lower Vil (max); (V  $_{OL, max}$  spec = 0.2V)

- u OEMs need to validate SRAMs meet CPU signal level requirements

- u Signals requiring external pullups may be affected

- a Use of large pullups is recommended to maintain sufficient noise margin

- ã Signals affected are for configuration only (e.g., BRDY#, BUSCHK#)

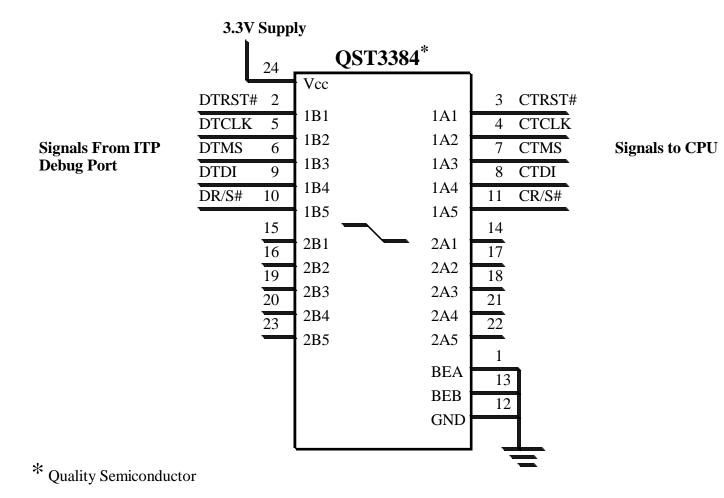

## I/O Signals (Cont'd)

#### • ITP/JTAG Interface requires existing 3.3V debug equipment

- u Q-switch can be used to interface 3.3V signals to Mobile PPMT on 0.25 Micron JTAG interface (TRST#, TCLK, TMS, TDI, R/S#)

- u National, Quality Semiconductor, and TI have suitable Q-switches

- u CPU 'piggy back' board may be inserted between ITP debug port cable and board connector

- a 3.3V needs to be supplied to 'piggy back' board

- a OEM may choose to implement Q-switch circuit in his board design to eliminate 'piggy back' board

ITP/JTAG Interfacing Example

#### **o** 3.3V must be supplied to Q - switch

Mobile/Handheld Products Group Technical Marketing 1/98

Page 16

## **Bus-to-Core Ratio Changes**

#### • BF2 pin added for possible future upgrades

**u** Default = 0

u Layout option to allow possible future external pull-up to 2.5V

| <b>BF2</b> <sup>**</sup> (pin 184) | <b>BF1</b><br>(pin 185) | <b>BF0</b><br>(pin 186) | Mobile<br>PPMT on<br>0.25<br>Micron | P55C     | Mobile PPMT on 0.25<br>Micron Freq |

|------------------------------------|-------------------------|-------------------------|-------------------------------------|----------|------------------------------------|

| 0                                  | 0                       | 0                       | 2/5                                 | 2/5      | 166/66MHz                          |

| 0                                  | 0                       | 1                       | 1/3                                 | 1/3      | 200/66MHz                          |

| 0                                  | 1                       | 0                       | 1/2*                                | 1/2*     |                                    |

| 0                                  | 1                       | 1                       | 2/7                                 | Reserved | 233/66MHz                          |

| 1                                  | 0                       | 0                       | 1/4                                 | N/A      | 266/66MHz                          |

\* Note that the Mobile PPMT on 0.25 Micron defaults to the 1/2 bus-to-core ratio \*\* BF2 is not defined for P55CLM

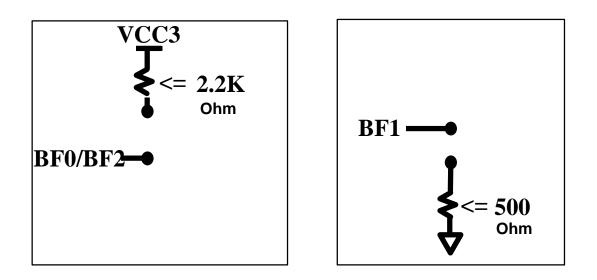

• External pull-up/pull-down resistor values for BF0, BF1, and BF2

| Pin Name | External Resistor<br>Type | Recommended<br>Value (ohm) |

|----------|---------------------------|----------------------------|

| BF0/BF2  | pull-up                   | < 2.2K                     |

| BF1      | pull-down                 | < 500                      |

## Bus-to-Core Ratio Changes (cont'd)

• For maximum flexibility, jumpers should be used to configure BF0-2

## I/O Signals (cont'd)

#### • Input pins must be connected to Vss if not used by the system

- u AHOLD, KEN#, WB/WT#, NA#, INV, BRDY#, or EWBE#

- u If not driven by system logic must be tied to ground via a weak pulldown resistor (i.e. >2 Kohms)

# **Processor CPU ID**

#### • Mobile Pentium(R) Processor with MMX<sup>TM</sup> Technology on 0.25 Micron CPUID is new (Different from P55CLM)

u Mobile PPMT on 0.25 Micron uses a model number of 08H; P55C used 04H

- u BIOS/application code that uses model number may need to change

- u Feature register may be accessed to determine specific features such as support for MMX<sup>TM</sup> technology

| CPUID                      | Reserved<br>[31:14] | Type<br>[13:12] | Family<br>[11:8] | Model<br>[7:4] | Stepping<br>[3:0] |

|----------------------------|---------------------|-----------------|------------------|----------------|-------------------|

| Mobile PPMT on 0.25 Micron | 0                   | 0h              | 5h               | 8h             | х                 |

| P55CLM                     | 0                   | 0h              | 5h               | 4h             | Х                 |

| P54CSLM                    | 0                   | 0h              | 5h               | 2h             | Х                 |

# Packaging

# • Mobile PPMT on 0.25 Micron -166, 200, 233, & 266 available in TCP and Mobile Module packaging

#### • Die Size

- u Production die-size (0.25 micron) smaller than P55CLM (0.35 micron)

- ã May require adjustment in the die-attach process

| Product                          | Die Length (DL) | Die Width (DW) |

|----------------------------------|-----------------|----------------|

| P55CLM                           | 12.855 mm       | 11.105 mm      |

| Mobile PPMT<br>on 0.25<br>Micron | 10.450 mm       | 9.088 mm       |

## Pin#11(BRDYC# ) and Pin#190 (FRCMC#) Connection Issue

- Design Consideration for Mobile Pentium(R) Processor with MMX(TM) Technology on .25 Micron only:

- Pin#11 (Vcc2) and pin#190 (Vcc2) on the Mobile Pentium Processor with MMX Technology on .25 Micron can be connected to either Vcc2 or Vcc3.

- When connected to Vcc2, there is a minor increase in leakage current (up to 300uA) on pin#11 and pin#190. To avoid the incremental leakage current, those pins are recommended to connect to Vcc3.

- pin#11 and pin#190 should be tied to Vcc3 to design for maximum margin in Vih spec. For future low power offerings of Mobile Pentium Processor with MMX Technology on .25 Micron, it is recommended to connect to Vcc3.

## Key Platform Validatation Areas

• Validation of O/S legacy applications and MMX(TM) applications

#### • 2.5V I/O interface signal integrity

- u Clock signals meet 2.5V spec

- u SRAMs/chipset signals meet interface spec (especially CPU Vil = 0.5V)

- System tuning flight time measurements and AC timing margin analyses

- Voltage supply solution

- System thermal solution

#### • CPU stress testing

Due to Mobile PPMT on 0.25 Micron operating characteristics, several validation areas need to be emphasized

# Platform Readiness/Checklist Summary

#### • Clock chip compatibility verified

- u Clock levels measured and within 2.5V spec

- u Undershoot/Overshoot/Rise/Fall within specification

#### • SRAM/chipset compatibility verified

u Voh/Vol measured and within Vil/Vih CPU spec

#### • Chipset AC timing compatibility verified

u Flight time measurements made and sufficient AC timing margin verified

### • Power supply compatibility verified

- u Tolerance measurements made and within spec

- ã Transient noise within budget

- ã Hi-frequency noise within budget

# • Thermal design capable of handling CPU/system requirements

u Tcase, Tamb, and power measured using worse case applications

## Mobile Pentium(R) Processor With MMX(TM) Technology On 0.25 Micron Collaterals

| <u>Document</u>                                                | <u>Date</u> |

|----------------------------------------------------------------|-------------|

| Mobile PPMT on 0.25 Micron Platform Architecture               | Now         |

| Analysis Rev. 1.0                                              |             |

| <b>CPU Power Measurement Method and Thermal</b>                | Now         |

| Implications                                                   |             |

| EDS Rev 2.0                                                    | Now         |

| Mobile Design Considerations Rev. 2.0                          | Now         |

| IBIS Model                                                     | Now         |

| BSDL File                                                      | Now         |

| Mobile PPMT on 0.25 Micron 200/233 MHz data sheets             | Now         |

| Mobile PPMT on 0.25 Micron 166/266 MHz final specs             | Now         |

| Mobile PPMT on 0.25 Micron 166/266 MHz data sheets             | Now         |

| Mobile PPMT on 0.25 Micron performance brief (166-<br>266 MHz) | Now         |