#### **INTRODUCTION**

The KS58015 is a DTMF dialer for 4 bit binary data input from microprocessor. When the tone enable input low, the oscillator is inhibited and the device is in a low power consumption at standby mode. On the low to high transition of tone enable, data is latched into the device and selected the standard DTMF signals.

The N-channel open drain output provides a MUTE output during tone generation.

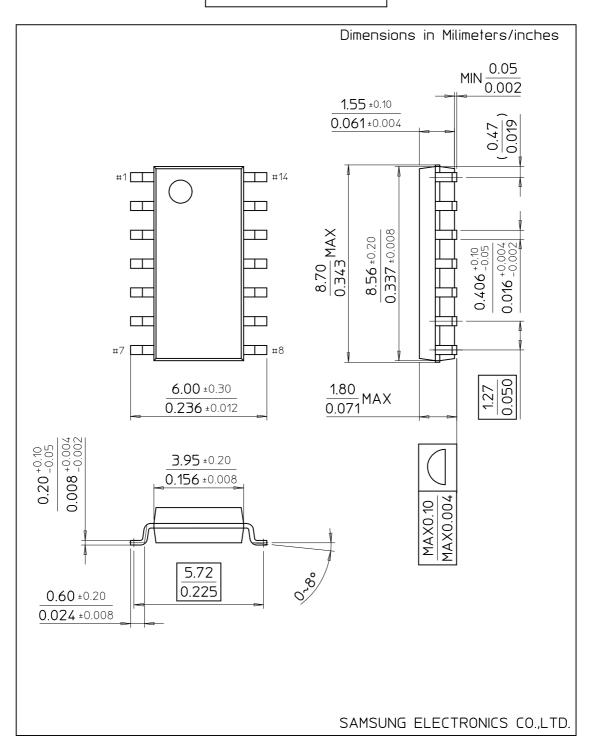

# 14-SOP-225B

#### **FEATURES**

- · Direct interface with microprocessor

- Generates 16 standard tones

- Uses inexpensive TV crystal or ceramic resonator (3.579545MHz)

- Very low total harmonic distortion

- Low power standby mode

- Binary data inputs with latches

- Wide Operating Voltage: 2.5 ~ 8.0V

## **ORDERING INFORMATION**

| Device   | Package     | Operating Temperature |

|----------|-------------|-----------------------|

| KS58015N | 14-DIP-300  | - 30°C ~ + 70°C       |

| KS58015D | 14-SOP-225B | - 30 0 4 + 70 0       |

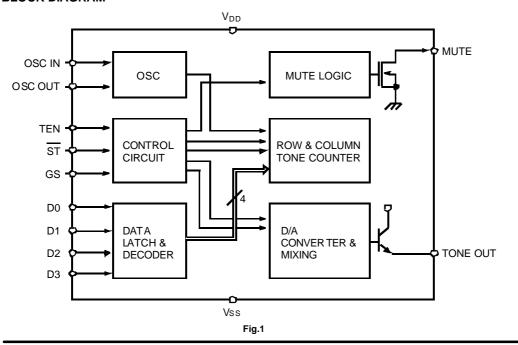

## **BLOCK DIAGRAM**

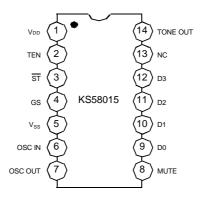

# **PIN CONFIGURATION**

Fig. 2

# **PIN DESCRIPTION**

| Pin No | Symbol          | Descriptions                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | $V_{DD}$        | Positive supply input                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 2      | TEN             | Tone enable input. An internal pull-up resistor is in a chip. When this pin connects to logic 'low', the oscillator is inhibited and the tone generators and output transistor are turned off. A low to high transition on this pin latches in data from D0 ~ D3, and tone generation continues until this pin is connected 'low' again. |  |  |  |  |

| 3      | ST              | Single tone enable. An internal pull-up resistor is in a chip. When this pin connects to logic 'low', the device is in a single tone mode. For normal operation, connects this pin to V <sub>DD</sub> or open-circuit.                                                                                                                   |  |  |  |  |

| 4      | GS              | Group selection input. This pin is used to select the high group or low group frequency, when the device is in single tone mode. An internal pull-up resistor is in a chip. When this pin connects to $V_{DD}$ or open, the high group will be generated, and whe connects to $V_{SS}$ , the low group will be generated.                |  |  |  |  |

| 5      | V <sub>SS</sub> | Negative supply input                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 6      | OSC IN          | Oscillator input                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 7      | OSC OUT         | Oscillator output                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 8      | MUTE            | N-channel open drain output.  This pin is a logic high state, when the tone enable pin is a high state.  This pin goes a logic low state, when the tone enable pin is a low state.                                                                                                                                                       |  |  |  |  |

| 9, 10, | D0, D1,         | DATA-INPUTS. These are the inputs for binary-coded data, which is latched in on                                                                                                                                                                                                                                                          |  |  |  |  |

| 11, 12 | D2, D3          | the rising edge of the tone enable signal.                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 13     | N.C             | No connection.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 14     | Tone out        | This output is the open emitter of a NPN transistor. When an external load resistor is connected from this pin to $V_{SS}$ , the tone generates on the tone enable pin = 'High'.                                                                                                                                                         |  |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic        | Symbol                | Value                            | Unit |

|-----------------------|-----------------------|----------------------------------|------|

| Supply Voltage        | $V_{DD}$              | 9                                | V    |

| MUTE Voltage          | V <sub>I (MUTE)</sub> | 9                                | V    |

| Input Voltage         | $V_1$                 | $V_{DD} + 0.3 \sim V_{SS} - 0.3$ | V    |

| Power Dissipation     | $P_D$                 | 500                              | mW   |

| Operating Temperature | T <sub>OPR</sub>      | - 30 ~ + 70                      | °C   |

| Storage Temperature   | T <sub>STG</sub>      | - 55 ~ <b>+</b> 125              | °C   |

## **ELECTRICAL CHARACTERISTICS**

(V<sub>SS</sub> = 0V, 2V<V<sub>DD</sub><8V,  $f_{OSC}$  = 3.579545MHz, Ta = 25°C, unless otherwise noted)

| Characteristic           | Symbol                 | Test Conditions                                  | Min                | Тур | Max                | Unit |

|--------------------------|------------------------|--------------------------------------------------|--------------------|-----|--------------------|------|

| Operating Voltage Range  | $V_{DD}$               |                                                  | 2.0                |     | 8.0                | V    |

| Operating Current        | I <sub>DD</sub>        | V <sub>DD</sub> = 3.0V, MUTE Open                |                    |     | 1.5                | mA   |

| Standby Current          | I <sub>SB</sub>        | $R_L = 10K, D0~D3 \text{ open}, V_{DD} = 3.0V$   |                    | 50  | 100                | μΑ   |

| Input Pull-up Resistance | R <sub>I (PULL)</sub>  | DI0 ~ DI3, TEN                                   |                    | 100 |                    | ΚΩ   |

| Input Voltage            | V <sub>IL</sub>        | DIO DIO TENI                                     |                    |     | 0.2V <sub>DD</sub> | V    |

|                          | V <sub>IH</sub>        | DI0 ~ DI3, TEN                                   | 0.8V <sub>DD</sub> |     | $V_{DD}$           | V    |

| 0 1 10 1 (MUTE)          | I <sub>OL (MUTE)</sub> | $V_{DD} = 3V$ , $V_O = 0.5$ , TEN = LOW          | 0.5                | 1.5 |                    | mA   |

| Output Current (MUTE)    | I <sub>OH (MUTE)</sub> | $V_{DD} = 3V$ , $V_{O} = V_{DD}$ , TEN = HIGH    |                    | 1   | 2                  | μΑ   |

| Tone Output Level        | V <sub>O (TONE)</sub>  | $V_{DD} = 3V$ , $R_L = 5K\Omega$ , Row Tone      | -14                |     | -11                | dBV  |

| Ratio of Column to Row   | dB <sub>CR</sub>       | $V_{DD} = 3V, R_L = 5 \text{ K}\Omega$           | 1                  | 2   | 3                  | dB   |

| THD (Dual Tone)          | THD                    | 1MHz Bandwidth, $V_{DD} = 5V$ , $R_L = 5K\Omega$ | -20                |     |                    | dB   |

| Oscillator Start-up Time | t <sub>ST (OSC)</sub>  | 90% Amplitudes, V <sub>DD</sub> = 3.0V           |                    | 4   |                    | mS   |

| Data Set-up Time         | t <sub>SU (DATA)</sub> | V <sub>DD</sub> = 3.0V                           | 200                |     |                    | nS   |

| Data Hold Time           | t <sub>H (DATA)</sub>  | V <sub>DD</sub> = 3.0V                           | 200                |     |                    | nS   |

| Data Duration            | t <sub>W (DATA)</sub>  | V <sub>DD</sub> = 3.0V                           | 600                |     |                    | nS   |

# **APPLICATION INFORMATION**

#### **FUNCTION DESCRIPTION**

When tone enable input is low, oscillator is inhibited, being allowed to low power standby mode since transistor goes to turn off state, so  $D0 \sim D3$  input data is ignored.

However if tone enable input goes from low to high, input data is latched and tone output is enabled, and it is correspond to data input.

This device is designed with 14 levels, 28 segments in each single-tone. The column tone is pre-emphasized 2dB than the row tone.

**TABLE1. SINGLE TONE FREQUENCY**

| Tone Group | Standard DTMF (Hz) | Tone Output Actual Frequency | % Deviation from Standard |

|------------|--------------------|------------------------------|---------------------------|

| ROW 1      | 697                | 699.13                       | + 0.31                    |

| ROW 2      | 770                | 766.17                       | - 0.50                    |

| ROW 3      | 852                | 845.43                       | - 0.54                    |

| ROW 4      | 941                | 947.97                       | + 0.74                    |

| COLUMN 1   | 1209               | 1215.89                      | + 0.57                    |

| COLUMN 2   | 1336               | 1331.67                      | - 0.33                    |

| COLUMN 3   | 1477               | 1471.85                      | - 0.35                    |

| COLUMN 4   | 1633               | 1645.01                      | + 0.75                    |

**TABLE 2. FUNCTION TABLE**

| Key Board  | Data Input |    |    | Tone Output |         |                     |

|------------|------------|----|----|-------------|---------|---------------------|

| Equivalent | D3         | D2 | D1 | D0          | f∟ (Hz) | f <sub>H</sub> (Hz) |

| 1          | 0          | 0  | 0  | 1           | 697     | 1209                |

| 2          | 0          | 0  | 1  | 0           | 697     | 1336                |

| 3          | 0          | 0  | 1  | 1           | 697     | 1477                |

| 4          | 0          | 1  | 0  | 0           | 770     | 1209                |

| 5          | 0          | 1  | 0  | 1           | 770     | 1336                |

| 6          | 0          | 1  | 1  | 0           | 770     | 1477                |

| 7          | 0          | 1  | 1  | 1           | 852     | 1209                |

| 8          | 1          | 0  | 0  | 0           | 852     | 1336                |

| 9          | 1          | 0  | 0  | 1           | 852     | 1477                |

| 0          | 1          | 0  | 1  | 0           | 941     | 1336                |

| *          | 1          | 0  | 1  | 1           | 941     | 1209                |

| #          | 1          | 1  | 0  | 0           | 941     | 1477                |

| А          | 1          | 1  | 0  | 1           | 697     | 1633                |

| В          | 1          | 1  | 1  | 0           | 770     | 1633                |

| С          | 1          | 1  | 1  | 1           | 852     | 1633                |

| D          | 0          | 0  | 0  | 0           | 941     | 1633                |

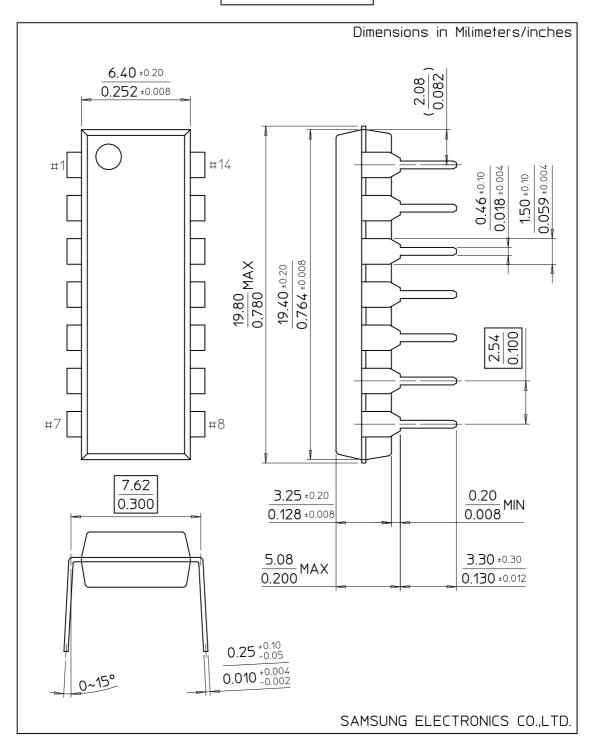

# 14-DIP-300

# 14-SOP-225B