# PRODUCT OVERVIEW

#### SAM87RI PRODUCT FAMILY

Samsung's SAM87RI family of 8-bit single-chip CMOS microcontrollers offer fast and efficient CPU, a wide range of integrated peripherals, and supports OTP device.

A dual address/data bus architecture and bit- or nibble-configurable I/O ports provide a flexible programming environment for applications with varied memory and I/O requirements. Timer/counters with selectable operating modes are included to support real-time operations.

#### KS86C6104/P6104 MICROCONTROLLER

The KS86C6104/P6104 microcontroller with USB function can be used in a wide range of general purpose applications. It is especially suitable for mouse or joystick controller and is available in 20-pin DIP and 20-pin SOP package.

The KS86C6104/P6104 single-chip 8-bit microcontroller is fabricated using an advanced CMOS process. It is built around the powerful SAM87RI CPU core.

Stop and Idle power-down modes were implemented to reduce power consumption. To increase on-chip register space, the size of the internal register file was logically expanded. The KS86C6104/P6104 has 4 Kbytes of program memory on-chip and 144 bytes of RAM including 16 bytes of working register.

Using the SAM87Ri design approach, the following peripherals were integrated with the SAM87Ri core:

- Two configurable I/O ports (11 pins)

- 7 bit-programmable pins for external interrupts

- 8-bit timer/counter with two operating modes

#### **OTP**

The KS86C6104 microcontroller is also available in OTP (One Time Programmable) version, KS86P6104. KS86P6104 microcontroller has an on-chip 4-Kbyte one-time-programmable EPROM instead of masked ROM. The KS86P6104 is comparable to KS86C6104, both in function and in pin configuration.

#### **FEATURES**

#### **CPU**

SAM87RI CPU core

#### **MEMORY**

- 4-Kbyte internal program memory (ROM)

- 128-byte RAM

- 16 bytes of working register

#### **INSTRUCTION SET**

- 41 instructions

- IDLE and STOP instructions added for powerdown modes

#### **INSTRUCTION EXECUTION TIME**

1.0 μs at 6 MHz f<sub>OSC</sub>

#### **INTERRUPTS**

- 12 interrupt sources with one vector

- One level, one vector interrupt structure

## **OSCILLATION CIRCUIT OPTIONS**

- 6 MHz crystal/ceramic oscillator

- External clock source

## **GENERAL I/O**

11 bit-programmable I/O pins

#### TIMER/COUNTER

- One 8-bit basic timer for watchdog function and programmable oscillation stabilization interval generation function

- One 8-bit timer/counter with Compare/Overflow counter

#### **USB SERIAL BUS**

- Compatible to USB low speed (1.5 Mbps) device 1.0 specification.

- Serial bus interface engine (SIE)

- Packet decoding/generation

- CRC generation and checking

- NRZI encoding/decoding and bit-stuffing

- Two 8-byte receive/transmit USB buffer

#### **OPERATING TEMPERATURE RANGE**

•  $-40^{\circ}$ C to  $+85^{\circ}$ C

#### **OPERATING VOLTAGE RANGE**

• 4.5 V to 5.5 V

#### **PACKAGE TYPES**

- 20-pin DIP

- 20-pin SOP

#### **COMPARATOR**

- 4-channel mode, 4-bit resolution

- 3-channel mode, external reference

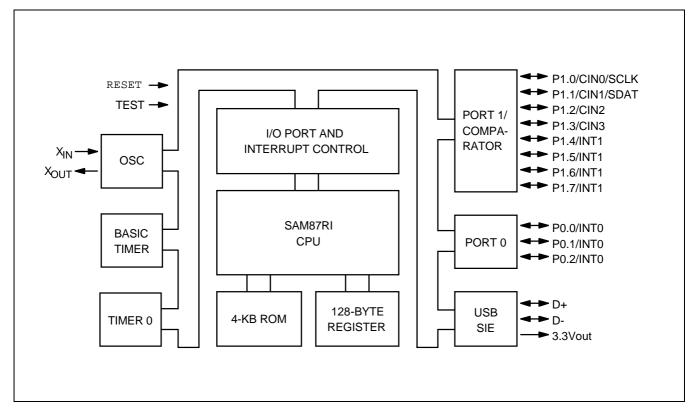

# **BLOCK DIAGRAM**

Figure 1-1. Block Diagram

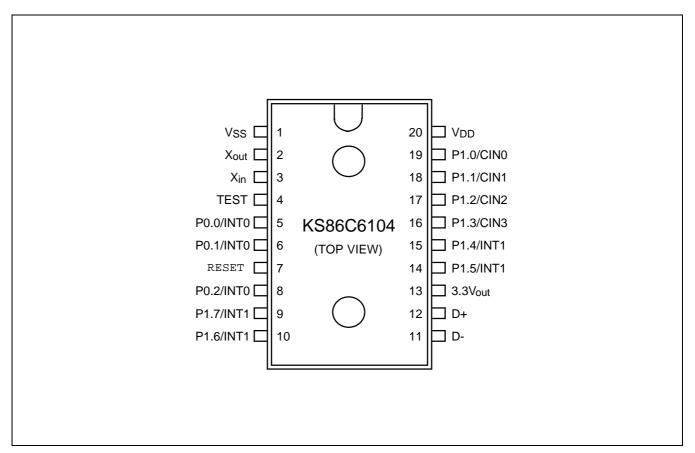

## **PIN ASSIGNMENTS**

Figure 1-2. Pin Assignment Diagram (20-Pin DIP/SOP Package)

# **PIN DESCRIPTIONS**

Table 1-1. KS86C6104/P6104 Pin Descriptions

| Pin<br>Names                       | Pin<br>Type | Pin<br>Description                                                                                                                                                                                                                                                        | Circuit<br>Number | Pin<br>Numbers | Share<br>Pins |

|------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|---------------|

| P0.0–P0.2                          | I/O         | Bit-programmable I/O port for Schmitt trigger input or push-pull output. Pull-up resistors are individually assignable to input pins by software and are automatically disable for output pins. Port0 can be individually configured as external interrupt inputs.        | D                 | 5, 6, 8        | INT0          |

| P1.0–P1.3                          | I/O         | Bit-programmable I/O port for Schmitt trigger input or push-pull output. Pull-up resistors are individually assignable to input pins by software. Port1.0–1.3 can be configured as comparator input                                                                       | F-8               | 19–16          | CIN0-<br>CIN3 |

| P1.4-P1.7                          | I/O         | Bit-programmable I/O port for Schmitt trigger input or push-pull output. Pull-up resistors are individually assignable to input pins by software and are automatically disabled for output pins. Port1.4–1.7 can be individually configured as external interrupt inputs. | D                 | 15, 14, 10, 9  | INT1          |

| D+/D-                              | I/O         | Only used as USB tranceive/receive port.                                                                                                                                                                                                                                  | _                 | 12–11          | _             |

| 3.3VOUT                            | 0           | Internal regulator 3.3 V output pin for referencing the voltage                                                                                                                                                                                                           | _                 | 13             | _             |

| X <sub>IN</sub> , X <sub>OUT</sub> | _           | System clock input and output pin (crystal/ceramic oscillator, or external clock source)                                                                                                                                                                                  | _                 | 3–2            | -             |

| INT0                               | I           | External interrupt for bit-programmable port0.                                                                                                                                                                                                                            | D                 | 5, 6, 8        | Port0         |

| INT1                               | I           | External interrupt for bit-programmable port1                                                                                                                                                                                                                             | D                 | 9, 10, 14, 15  | Port1         |

| RESET                              | I           | RESET signal input pin. Schmitt trigger input with internal pull-up resistor.                                                                                                                                                                                             | В                 | 7              | _             |

| TEST                               | I           | Test signal input pin (for factory use only; must be connected to V <sub>SS</sub> )                                                                                                                                                                                       | _                 | 4              | _             |

| V <sub>DD</sub>                    | _           | Power input pin                                                                                                                                                                                                                                                           | _                 | 20             | _             |

| V <sub>SS</sub>                    | _           | VSS is a ground power for CPU core.                                                                                                                                                                                                                                       | -                 | 1              | _             |

# **PIN CIRCUITS**

Table 1-2. Pin Circuit Assignments for the KS86C6104/P6104

| Circuit Number | Circuit Type | KS86C6104/P6104 Assignments    |

|----------------|--------------|--------------------------------|

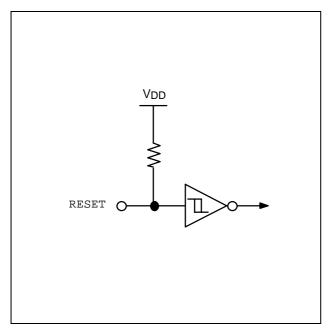

| В              | 1            | RESET signal input             |

| С              | 0            |                                |

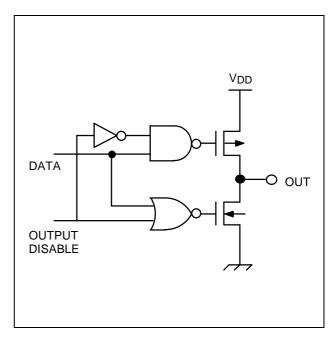

| D              | I/O          | Port0, Port1.4-1.7, INT0, INT1 |

| F-8            | I/O          | Port1.0-1.3                    |

**NOTE**: Diagrams of circuit types B–D, and F-8 are presented below.

Figure 1-3. Pin Circuit Type B

Figure 1-4. Pin Circuit Type C