# PRODUCT OVERVIEW

## SAM8 PRODUCT FAMILY

Samsung's SAM8 family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-programmable ROM sizes. Important CPU features include:

- Efficient register-oriented architecture

- Selectable CPU clock sources

- Idle and Stop power-down mode release by interrupt

- Built-in basic timer with watchdog function

A sophisticated interrupt structure recognizes up to eight interrupt levels. Each level can have one or more interrupt sources and vectors. Fast interrupt processing (within a minimum six CPU clocks) can be assigned to specific interrupt levels.

## KS88C6108/C6116/P6116 MICROCONTROLLERS

The KS88C6108/C6116/P6116 single-chip 8-bit microcontroller is based on the powerful SAM8 CPU architecture. The internal register file is logically expanded to increase the on-chip register space. The KS88C6108/C6116/P6116 have 8/16 K bytes of on-chip program ROM.

Following Samsung's modular design approach, the following peripherals were integrated with the SAM8 core:

- Four programmable I/O ports (total 28 pins)

- One 8-bit basic timer for oscillation stabilization and watchdog functions

- One 8-bit general-purpose timer/counter with selectable clock sources

- One 8-bit counter with selectable clock sources, including Hsync or Csync input

- One 8-bit timer for interval mode

- PWM block with seven 8-bit PWM circuits

- Sync processor block (for Vsync and Hsync I/O, Csync input, and Clamp signal output)

Multi master IIC-bus with DDC support.

The KS88C6108/C6116/P6116 are a versatile microcontroller that is ideal for use in multi-sync monitors or in general-purpose applications that require sophisticated timer/counter, PWM, sync signal processing, and multi-master IIC-bus support with DDC. It is available in a 42-pin SDIP or a 44-pin QFP package.

Figure 1-1. KS88C6108/C6116/P6116 Microcontrollers

SAMSUNG

# FEATURES

#### CPU

• SAM8 CPU core

#### Memory

- 8/16-Kbyte internal program memory (ROM)

- 272-byte general-purpose register area

#### **Instruction Set**

- 78 instructions

- IDLE and STOP instructions added for powerdown modes

#### Instruction Execution Time

• 500 ns minimum (with 12 MHz CPU clock)

#### Interrupts

- Nine interrupt sources

- Nine interrupt vectors

- Six interrupt levels

- Fast interrupt processing for a select level

#### General I/O

• Four I/O ports (total 28 pins):

#### 8-Bit Basic Timer

- Programmable timer for oscillation stabilization interval control or watchdog timer functions

- Three selectable internal clock frequencies

#### **Timer/Counters**

- One 8-bit general-purpose timer/counter with programmable operating modes and the following clock source options:

- Two selectable internal clock frequencies

- One 8-bit timer with interval operating mode

- One 8-bit counter with the following clock source options:

- Two selectable internal clock frequencies

- Hsync (or Csync) input from the sync processor block

- External clock source

#### **Pulse Width Modulator**

- Seven 8-bit PWM modules:

- 8-bit basic frame

- Four push-pull and three n-channel, open-drain output channels

- Selectable clock frequencies: 46.875 kHz at 12 MHz fosc.

#### Sync Processor

- Detection of sync input signals (Vsync-I, Hsync-I, and Csync-I)

- Sync signal separation and output (Hsync-O, Vsync-O, and Clamp-O)

- Pseudo sync signal output

- Programmable clamp signal output

#### **DDC and Multi-Master IIC-Bus**

- Serial peripheral interface

- Support for display data channel (DDC)

#### **Oscillator Frequency**

- 6 MHz to 12 MHz external crystal oscillator

- Interval Max. 12MHz CPU clock

#### **Operating Temperature Range**

•  $-40^{\circ}C$  to  $+85^{\circ}C$

#### **Operating Voltage Range**

• 4.5 V to 5.5 V

#### Package Types

• 42-pin SDIP, 44-pin QFP

# **BLOCK DIAGRAM**

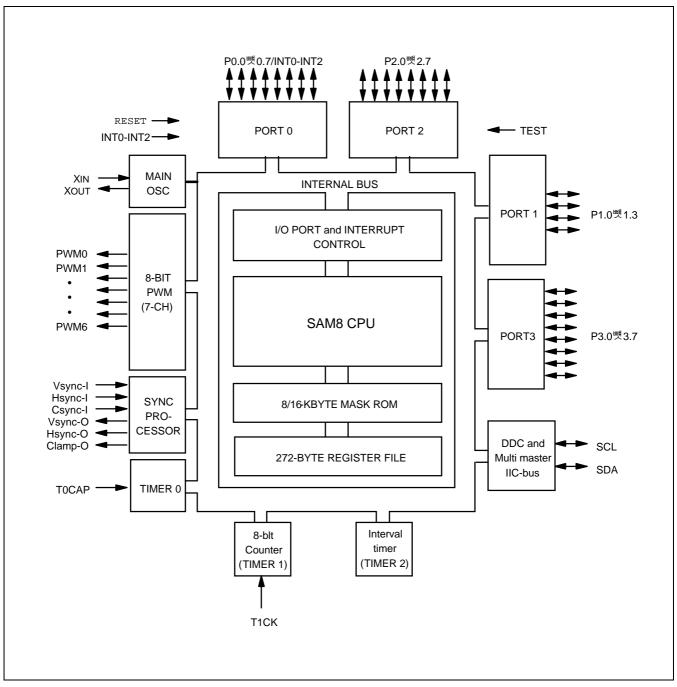

Figure 1-2. Block Diagram

## **PIN ASSIGNMENTS**

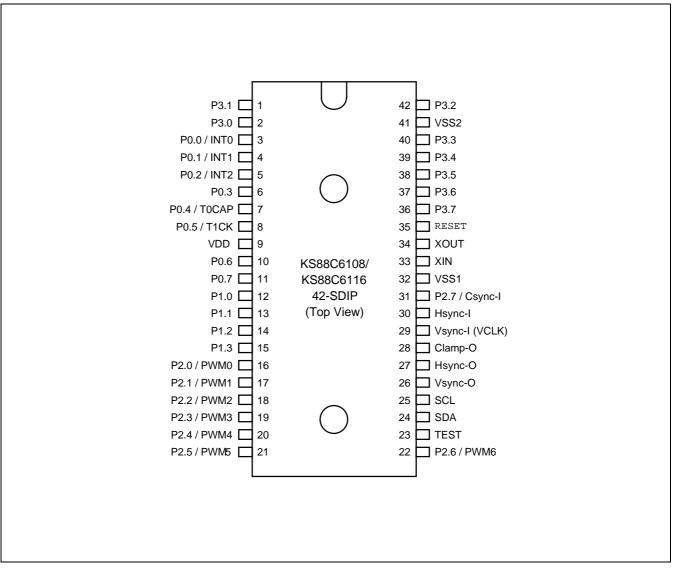

Figure 1-3. Pin Assignment Diagram (42-SDIP Package)

## **PIN ASSIGNMENTS (Cont.)**

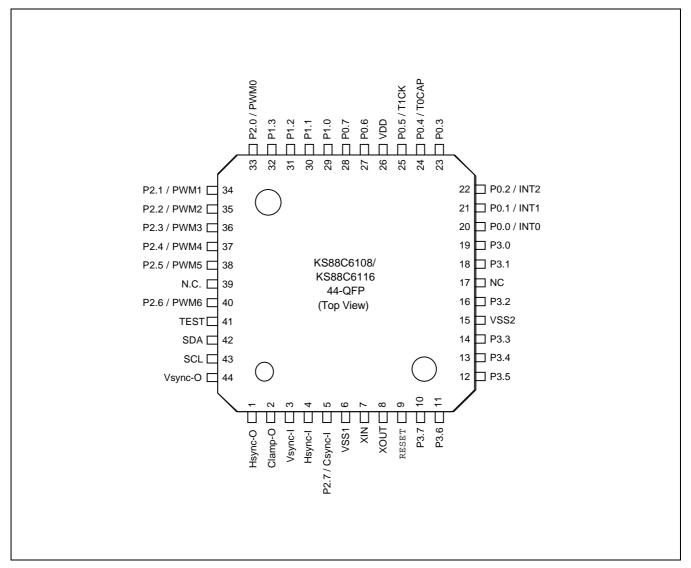

Figure 1-4. Pin Assignment Diagram (44-QFP Package)

# **PIN DESCRIPTIONS**

| Pin<br>Names                                                      | Pin<br>Type                   | Pin<br>Description                                                                                                                                                                                  | Circuit<br>Type                               | SDIP Pin<br>Numbers                          | Shared<br>Functions                                             |

|-------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------------------------------------|

| P0.0<br>P0.1<br>P0.2<br>P0.3<br>P0.4<br>P0.5<br>P0.6<br>P0.7      | I/O                           | General-purpose, 8-bit I/O port. Share<br>functions include three external interrupt<br>inputs, I/O for timers 0 and 1. You can<br>selectively configure port 0 pins to input or<br>output mode.    | D-1                                           | 3<br>4<br>5<br>6<br>7<br>8<br>10<br>11       | INT0<br>INT1<br>INT2<br>T0CAP<br>T1CK                           |

| P1.0–P1.3                                                         | I/O                           | General purpose, 8-bit I/O port. You can selectively configure port 1 pins to input or push-pull output mode.                                                                                       | D-1                                           | 12–15                                        | _                                                               |

| P2.0<br>P2.1<br>P2.2<br>P2.3<br>P2.4<br>P2.5<br>P2.6<br>P2.7      | I/O                           | General purpose, 8-bit I/O port. You can<br>selectively configure port 2 pins to input or<br>output mode. The port 2 pin circuit are<br>designed to push-pull PWM output and<br>Csync signal input. | D-1<br>D-1<br>D-1<br>E-1<br>E-1<br>E-1<br>D-1 | 16<br>17<br>18<br>19<br>20<br>21<br>22<br>31 | PWM0<br>PWM1<br>PWM2<br>PWM3<br>PWM4<br>PWM5<br>PWM6<br>Csync-I |

| P3.0-P3.7                                                         | I/O                           | General-purpose, 8-bit I/O port. You can selectively configure port 3 pins to input or output mode.                                                                                                 | E                                             | 2, 1, 42,<br>40–36                           | _                                                               |

| Hsync-I<br>Vsync-I<br>Clamp-O<br>Hsync-O<br>Vsync-O<br>SCL<br>SDA | <br> <br> <br> <br> /0<br> /0 | The pins are sync processor signal I/O and IIC-bus clock and data I/O                                                                                                                               | A<br>A<br>A<br>A<br>G-3<br>G-3                | 30<br>29<br>28<br>27<br>26<br>25<br>24       | _                                                               |

| V <sub>DD</sub><br>V <sub>SS1</sub> , V <sub>SS2</sub>            | -                             | Power supply pins                                                                                                                                                                                   | -                                             | 9<br>32, 41                                  | _                                                               |

| X <sub>IN</sub> , X <sub>OUT</sub>                                | _                             | System clock input and output pins                                                                                                                                                                  | -                                             | 33, 34                                       | -                                                               |

| RESET                                                             | I                             | System reset pin                                                                                                                                                                                    | В                                             | 35                                           | _                                                               |

| TEST                                                              | I                             | Factory test pin input<br>0 V: normal operation<br>5 V: factory test mode                                                                                                                           | -                                             | 23                                           | -                                                               |

## Table 1-1. KS88C6108/C6116/P6116 Pin Descriptions

**NOTE**: See 'Pin Circuit Diagrams' on next two pages for detailed information on circuit types A, B, D-1, E, E-1, and G-3.