Preliminary Data Sheet Publication Number 10-88-9408 July 1997 (Rev. 0.0)

# **OVERVIEW**

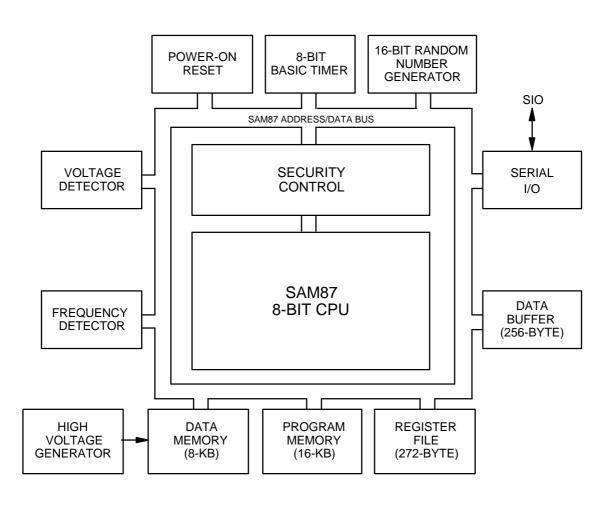

The KS88C9408 single-chip CMOS micro-controller is designed for low voltage smart card applications and is fabricated using an advanced 0.65-micron CSMOS process. Its fast and reliable 8-bit CPU is based on the proven Zilog Super8<sup>®</sup> architecture.

The KS88C9408 has 8 Kbytes of EEPROM, 528 bytes of SRAM, 16 Kbytes of program ROM, a 16-bit random number generator, an 8-bit basic timer, a power-on reset circuit, asynchronous serial I/O interface and numerous security options.

## **FEATURES**

#### CPU

- SAM87 8-bit CPU core

- 78 instructions, including multiply and divide

- STOP and IDLE instruction is added to reduce power consumption

#### **Memory Allocation**

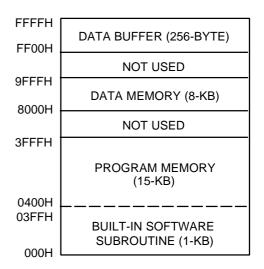

- 15 Kbytes of ROM for the application program and 1 Kbytes for the built-in subroutine(kernel)

- 8 Kbytes Data Memory (EEPROM)

- 256 bytes Static RAM

- 272 bytes for general-purpose register file

#### **EEPROM Write Operations**

- Programmable EEPROM erase/write time

- Byte-wise to Page-wise (32 bytes) EEPROM erase/write operations are supported

- 1.5ms fast erase/write time each (typical)

- More than 100,000 erase/write cycles

- Greater than 10 years data retention

# **KS88C9408** CMOS Microcontroller for Smart Card Applications

The time required to complete an EEPROM erase/write operation is a fast 1.5 ms each (typical).

The serial I/O module supports fast data transfer rates of 9.6, 19.2, and 38.4 Kbps.

For added data security and for easier programming, EEPROM erase/write and serial I/O subroutines are integrated in the KS88C9408 ROM.

The KS88C9408 either meets or exceeds all relevant ISO standards.

#### **Data Security**

- Secure (non-visible) ROM coding

- 32-byte security PROM, hardware protected

- Unique serial number for each chip

- Reset operation are selective if abnormal voltage or frequency is detected.

#### Serial I/O Interface

- Asynchronous half-duplex character transmission serial Interface (conforms to ISO standards 7816-3)

- Data transfer rates of 9.6, 19.2, or 38.4 Kbps at 3.57-MHz external clock

- Software (kernel) control

#### Random Number Generator

- One 16-bit random number generator with internal ring oscillator

- Start and Stop control

#### **Basic Timer**

• One 8-bit Basic timer for internal reset operation and watchdog timer functions

### **Reset Function**

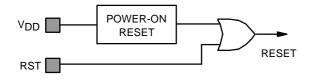

Power-on reset and External reset circuits

#### **Operating Characteristics**

- Single power supply: 2.7–5.5 V

- Operating frequency range: 1–5 MHz

- Operating temperature range: 25°C to + 70°C

#### Package

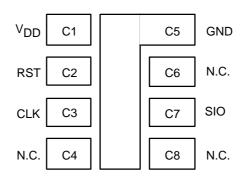

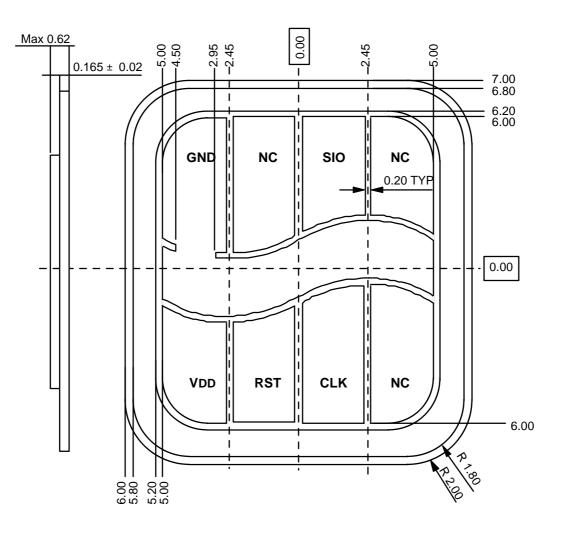

• 8-pin COB (conforms to ISO standard 7816)

Figure 1. KS88C9408 Block Diagram

Figure 2. Pin Assignments

| Table 1. | KS88C9408 | Pin | Descriptions |

|----------|-----------|-----|--------------|

|----------|-----------|-----|--------------|

| Pin<br>Number | Pin<br>Name     | Function<br>Description                                                                            | Pin<br>Type  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------|--------------|

| C1            | V <sub>DD</sub> | Power input                                                                                        |              |

| C2            | RST             | System reset input                                                                                 | Input        |

| C3            | CLK             | External clock input                                                                               | Input        |

| C4            | NC              | No connection                                                                                      | —            |

| C5            | GND             | Ground                                                                                             | —            |

| C6            | NC              | No connection                                                                                      | —            |

| C7            | SIO             | Serial data input and output pin: External pull-up resistor should be connected to $V_{\mbox{DD}}$ | Input/output |

| C8            | NC              | No connection                                                                                      | _            |

# **FUNCTION OVERVIEW**

#### CPU

The KS88C9408 8-bit CPU (SAM87) architecture is based on a 16-bit address bus and an 8-bit data bus. The internal bus supports memory, register, and stack operations, interrupt handling, clock, and power-down control logic.

#### **Instruction Set**

The SAM87 instruction set is designed to support a large register file and consists of 78 instructions, including multiply and divide.

The instruction set also supports decimal adjustment of binary-coded decimal (BCD) numbers, 16-bit word increment and decrement, and bit addressing, as well as rotate and shift operations.

### **Addressing Modes**

The KS88C9408 register architecture uses an efficient method of working register addressing to take full advantage of shorter instruction formats and to reduce execution times. An instruction can address a single 8-bit register or a 16-bit register pair. There are seven explicit addressing modes (not all addressing modes are available for each instruction):

- Register (R)

- Indirect Register (IR)

- Indexed (X)

- Direct Address (DA)

- Indirect Address (IA)

- Relative Address (RA)

- Immediate (IM)

#### Interrupts

The SAM87 interrupt structure has three components: level, source, and vector. The KS88C9408 uses one interrupt source and one vector (one vector for one source).

Interrupt source corresponds to one level. One interrupt level can be selected for the special fast interrupt processing feature.

### System Clock Control

Clock frequency input from an external device may range from 1–5 MHz. The typical input clock frequency is 3.57 MHz. To obtain this frequency, you must select a non-divided CPU clock using the appropriate system clock control register settings.

Please note that the data transfer rates which are supported by the KS88C9408 serial I/O interface (9.6, 19.2, and 38.4 Kbps) are based on the typical 3.57-MHz clock frequency value.

#### **Basic Timer**

The KS88C9408 8-bit basic timer has two functions:

- To provide an automatic reset mechanism (watchdog timer function) in the event of a system malfunction. If the 8-bit counter overflows, a system reset is initiated.

- To determine the length of the oscillation stabilization interval following a reset. When an external reset or interrupt occurs in Stop mode, or when a power-on reset occurs, the CPU waits for the reset release interval to elapse before resuming normal operation.

#### **Reset Operations**

When the power supplied to the KS88C9408 through the  $V_{DD}$  pin reaches a minimum level, an internal reset operation is initiated. A reset can also be triggered by the rising edge of the external reset signal through the RST pin.

The minimum Low level width of the external reset signal is 5  $\mu$ s. An overflow of the basic timer counter signals the CPU that the programmed oscillation stabilization interval has elapsed, and that it can enter normal operating mode.

The KS88C9408 has an integrated power-on reset circuit. When RESET is released and returns to High level, the CPU fetches the instruction stored at program memory location 100H (the reset vector address), and then jumps to the start address of the application program (400H).

Figure 3. Reset Logic

#### **Power-Down Modes**

Idle mode is invoked by the instruction, IDLE. In Idle mode, the CPU "sleeps" while select peripherals remain active. The internal clock signal is gated off to the CPU, but is supplied to the interrupt structure, basic timer, serial I/O block, or the random number generator.

Stop mode is invoked by the instruction, STOP. In Stop mode, the CPU and all peripheral functions "go to sleep", and all on-chip operations come to a halt.

The Idle mode or Stop mode power-down condition may be released in two ways:

- By an interrupt (After the interrupt is serviced, the instruction immediately following the one that initiated Idle mode is executed).

- By a reset operation (When RESET is released and returns to High level, the CPU fetches the instruction stored at memory location 0100H and executes the application program).

#### **Program Memory (ROM)**

The KS88C9408 has a 16-Kbyte, read-only program memory (ROM). The upper 15-Kbyte of the ROM is reserved for a user application program. The lower 1-Kbyte is reserved for a built-in subroutine (kernel).

#### Data Memory (EEPROM)

The KS88C9408 has an 8-Kbyte electrically erasable programmable read-only memory (EEPROM). The EEPROM area is organized as a 32-byte page.

A single EEPROM load operation consists of an erase and a write operation of from 1 to 32 bytes:

- In the erase operation, the selected data bytes within the address range are set to logic one.

- In the write operation, individual bits within the byte range are selectively changed from logic one to logic zero.

A built-in subroutine supports programming in data memory. The lower 32 bytes of the EEPROM (8000H–801FH) is a read-only information area. You can use this area to store manufacturing data about the chip or the smart card.

#### Data Buffer (SRAM)

The KS88C9408 has a 256-byte area (in SRAM) which serves as a buffer for serial data that is being transmitted or received through the SIO pin.

Figure 4. Memory Map

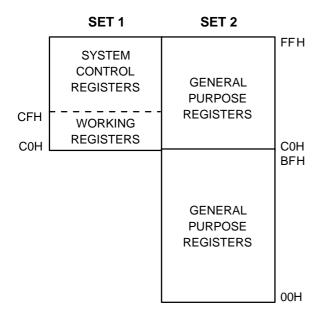

#### Register File (SRAM)

The KS88C9408 has a 272-byte area in SRAM for general-purpose registers and working registers, and another 25 bytes for mapped system control registers.

#### Serial I/O Interface

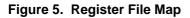

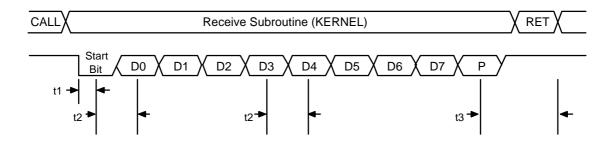

The KS88C9408 supports asynchronous half-duplex serial I/O in conformance with the ISO 7816-3 standard. A 10-bit frame (one start bit, eight data bits, LSB first and one even parity bit) is used for serial transmit and receive operations. Data transfer rates of 9.6, 19.2, and 36.4 Kbps (at 3.57 MHz) are supported.

Serial data transfer rates are fully compliant with ISO standards:

— Using the built-in software subroutine (kernel)

#### **Security Features**

The KS88C9408 voltage and frequency detectors perform the following functions:

- Detect abnormal V<sub>DD</sub> levels

- Detect abnormal clock frequencies

Using security control register setting, programmers can enable or disable the chip reset function, as required by the application.

#### **Random Number generator**

A 16-bit random number generator issues security keys which are used for authentication procedures in smart card applications.

# **ELECTRICAL DATA**

#### Table 2. Absolute Maximum Ratings

#### $(T_A = 25^{\circ}C)$

| Parameter               | Symbol           | Conditions | Rating                        | Unit |

|-------------------------|------------------|------------|-------------------------------|------|

| Supply voltage          | V <sub>DD</sub>  | _          | -0.3 to +7.0                  | V    |

| Input voltage           | VIN              |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage          | Vo               |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating temperature   | TA               |            | -25 to +70                    | °C   |

| Storage temperature     | T <sub>STG</sub> |            | -65 to +150                   | °C   |

| Electrostatic discharge | V <sub>ESD</sub> | _          | 5000                          | V    |

| Table 3. D.C. Electrical Characteristics $(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C, V_{DD} = 2.7 \text{ V to } 5.5 \text{ V})$ |                  |                                 |                     |     |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|---------------------|-----|--|--|

| Parameter                                                                                                                           | Symbol           | Conditions                      | Min                 | Тур |  |  |

| Supply voltage                                                                                                                      | V <sub>DD</sub>  | —                               | 2.7                 |     |  |  |

| Operating current                                                                                                                   | I <sub>DD1</sub> | f <sub>CLK</sub> = 3.57 MHz, 5V |                     | 3.5 |  |  |

|                                                                                                                                     |                  | f <sub>CLK</sub> = 3.57 MHz, 3V | —                   | 1.0 |  |  |

| Idle current (with clock)                                                                                                           | I <sub>DD2</sub> | f <sub>CLK</sub> = 3.57 MHz, 5V | —                   | 1.0 |  |  |

| Stop current (without clock)                                                                                                        | I <sub>DD3</sub> | f <sub>CLK</sub> = GND, 3V      | —                   | _   |  |  |

| High level input voltage                                                                                                            | V <sub>IH1</sub> | SIO                             | 0.7 V <sub>DD</sub> | _   |  |  |

|                                                                                                                                     | V <sub>IH2</sub> | RST                             | 0.8 V <sub>DD</sub> |     |  |  |

|                                                                                                                                     | V <sub>IH3</sub> | CLK                             | 0.7 V <sub>DD</sub> |     |  |  |

| High level input current                                                                                                            | l <sub>IH1</sub> | SIO                             | - 300               |     |  |  |

|                                                                                                                                     | I <sub>IH2</sub> | RST                             | -20                 | _   |  |  |

|                                                                                                                                     | I <sub>IH3</sub> | CLK                             | -20                 | _   |  |  |

| Low level input voltage                                                                                                             | VIL1             | SIO                             | 0                   | _   |  |  |

|                                                                                                                                     | V <sub>IL2</sub> | RST                             |                     |     |  |  |

|                                                                                                                                     | V <sub>IL3</sub> | CLK                             |                     |     |  |  |

| Low level input current                                                                                                             | I <sub>IL1</sub> | SIO                             | - 1000              |     |  |  |

|                                                                                                                                     | I <sub>IL2</sub> | RST                             | -200                | _   |  |  |

|                                                                                                                                     | I <sub>IL3</sub> | CLK                             | - 100               | _   |  |  |

| High level output voltage                                                                                                           | V <sub>OH</sub>  | SIO, I <sub>OH</sub> = −20 μA   | 0.7 V <sub>DD</sub> |     |  |  |

Vol

VLVD

VHVD

SIO,  $I_{OL} = 500 \ \mu A$

f<sub>CLK</sub> = 3.57 MHz

$f_{CLK} = 3.57 \text{ MHz}$

NOTE: Data for these parameters are for product verification purposes only.

Low level output voltage

Low-voltage detection voltage<sup>(note)</sup>

High-voltage detection voltage<sup>(note)</sup>

Max

5.5

10

5 2 10

$V_{DD}$

+ 20

+ 150 + 100 0.2 V<sub>DD</sub>

0.15 V<sub>DD</sub> 0.12 V<sub>DD</sub> + 20

> + 20 + 20

V<sub>DD</sub>

0.15 V<sub>DD</sub>

\_\_\_\_

\_\_\_\_

2.0

7.0

0

\_\_\_\_

\_\_\_

Unit

V

mΑ

μΑ

V

μΑ

V

μΑ

V

V

V

7

| Table 4. | A.C. | Electrical | Characteristics |

|----------|------|------------|-----------------|

|----------|------|------------|-----------------|

| $(T_A = -25^{\circ}C \text{ to } + 70^{\circ}C, V_{DD} = 25^{\circ}C \text{ to } + 70^{\circ}C, V_{DD} = 25^{\circ}C, V_{DD} = 25^{\circ}C \text{ to } + 70^{\circ}C, V_{DD} = 25$ | 2.7 V to | 5.5 V) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|

| Parameter                                               | Symbol                         | Conditions                                                              | Min     | Тур  | Max    | Unit   |

|---------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------|---------|------|--------|--------|

| Low-frequency detection frequency <sup>(1)</sup>        | flfd                           | V <sub>DD</sub> = 5 V                                                   | 200     | 500  | 800    | kHz    |

| High-frequency detection frequency <sup>(1)</sup>       | <sup>f</sup> HFD               | V <sub>DD</sub> = 5 V                                                   | 7       | 10   | 12     | MHz    |

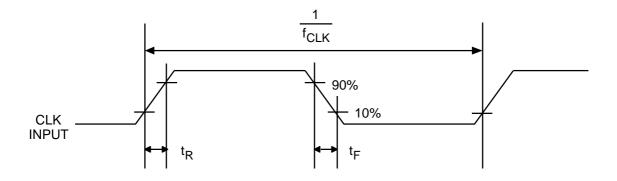

| External clock frequency                                | fCPU                           | CPU clock                                                               | 1       | 3.57 | 5      | MHz    |

| External clock duty <sup>(1)</sup>                      | t <sub>CW</sub>                | Clock width                                                             | 45      | 50   | 55     | %      |

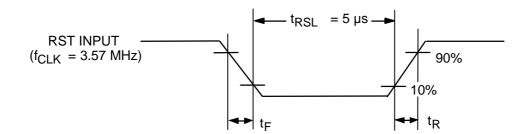

| RST Low level width (1)                                 | t <sub>RSL</sub>               | —                                                                       | 5       | _    | —      | μs     |

| EEPROM erase time                                       | tE                             | —                                                                       | —       | 1.5  | —      | ms     |

| EEPROM write time                                       | t <sub>W</sub>                 | —                                                                       | —       | 1.5  | —      | ms     |

| EEPROM data retention time <sup>(1)</sup>               | ts                             | _                                                                       | 10      | —    | —      | Years  |

| EEPROM endurance<br>(erase/write cycles) <sup>(1)</sup> | nE/W                           | _                                                                       | 100,000 | —    | —      | Cycles |

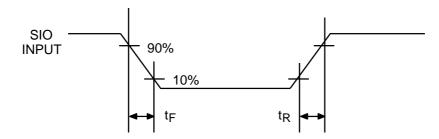

| Rise time, fall time <sup>(1)</sup>                     | t <sub>R,</sub> t <sub>F</sub> | SIO<br>C <sub>IN</sub> = 30 pF, C <sub>OUT</sub> = 30 pF                | —       | —    | 1      | μs     |

|                                                         |                                | RST<br>C <sub>IN</sub> = 30 pF, C <sub>OUT</sub> = 30 pF                |         |      | 1      |        |

|                                                         |                                | CLK <sup>(2)</sup><br>C <sub>IN</sub> = 30 pF, C <sub>OUT</sub> = 30 pF |         |      | 0.5×9% |        |

NOTES:

1.

Data for these parameters are for product verification purposes only. The rise time, fall time data for CLK assumes 9% of the period with a maximum time of 0.5 µs. This condition is 2. represented by the formula,  $0.09 \times 1$  / f<sub>CLK</sub>.

# SIO TIMING DIAGRAM

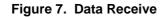

Figure 6. Data Receive

| bps   | t1      | t2  | t3  | t4  | t5 |  |

|-------|---------|-----|-----|-----|----|--|

| 9600  | 178–196 | 372 | 305 | 115 | 17 |  |

| 19200 | 86–104  | 186 | 161 | 115 | 17 |  |

| 38400 | 38–56   | 92  | 127 | 115 | 17 |  |

Table 5. Number of Clock for Sampling at 3.57 MHz

Figure 8. RST Input Wave Form

Figure 9. CLK Input Wave Form

Figure 10. SIO Input Wave Form

# **MECHANICAL DATA**

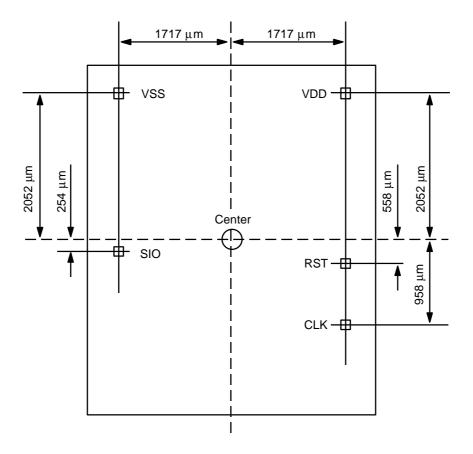

Figure 11. Chip Dimensions

#### NOTES:

- 1. Dimensions are in millimeters.

- 2. The 8-pad COB package dimensions shown above are only approximate. Actual dimensions are adapted to customer specifications.

#### Figure 12. Package Dimensions

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others.

© 1997 SAMSUNG ELECTRONICS