# L6503

# HAMMER SOLENOID CONTROLLER

# PRELIMINARY DATA

- DRIVES FOUR DARLINGTONS WITH UP TO 2.5 mA DRIVE CURRENT

- FEEDBACK LOOP CONTROLS DARLINGTON CURRENT

- PRESETTABLE CONDUCTION TIME

- LATCHED µC-COMPATIBLE INPUTS

- DIAGNOSTIC CIRCUITRY

### DESCRIPTION

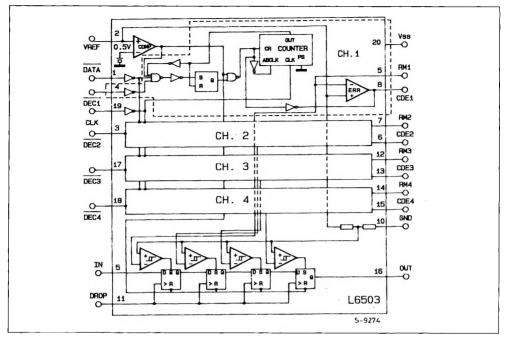

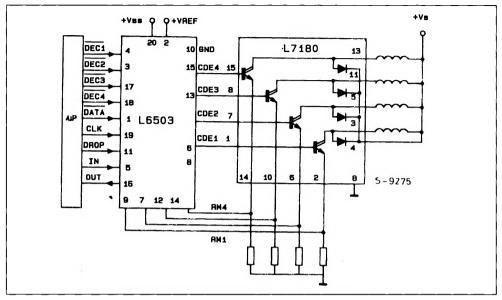

Designed primarily for selenoid driving applications, the L6503 Hammer Solenoid Controller includes all the circuitry needed to control four darlington power devices or a quad darlington array such as the SGS L7180.

The device is controlled by four latched logic inputs, which may be connected directly to a microcomputer chip, plus an analog input which sets the load current. Additionally, the conduction time of the outputs is controlled by a clock input which drives internal timers.

#### Fault conditions may be detected thanks to diagnostic circuitry which allows the control micro to read (serially) the load current status of the external darlingtons.

Assembled in a 20-pin DIP package, the L6503 operates on a single 5 V supply and is suitable for computer printers, solenoid valves and similar applications.

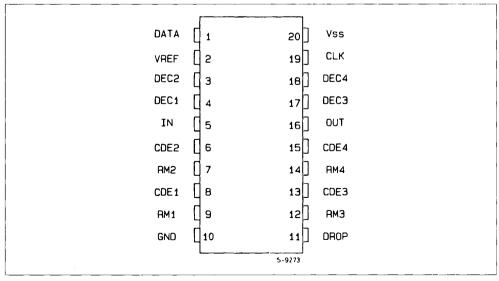

#### **CONNECTION DIAGRAM** (top view)

## **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS

| Symbol         | Parameter                                   | Value                      | Unit<br>V |  |

|----------------|---------------------------------------------|----------------------------|-----------|--|

| Vss            | Supply Voltage                              | 7                          |           |  |

| ICDE           | Output Current                              | 10                         | mA        |  |

| Vi             | Input Voltage (for analog and logic inputs) | 0 to V <sub>ss</sub> - 0.5 | V         |  |

| Top            | Operating Temperature                       | 0 to 70                    | °C        |  |

| $T_{stg}, T_j$ | Storage and Junction Temperature            | - 40 to 150                | °C        |  |

# THERMAL DATA

| Rth j-amb Thermal Resistance Junction-ambient | Max | 80 | °C/W |

|-----------------------------------------------|-----|----|------|

#### PIN FUNCTIONS DESCRIPTION

| N° | Name             | Function                                                                                                                     |

|----|------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1  | DATA             | Latches control command into the four inputs DEC1-DEC4 on the high-low transition.                                           |

| 2  | V <sub>ret</sub> | Analog reference input which sets the load current for all four channels ; when lower than 0.5 V resets the logic circuitry. |

| 3  | DEC2             | Data input for channel 2. Data is latched on the high-low transition of the DATA input.                                      |

| 4  | DEC1             | Data Input for Channel 1.                                                                                                    |

| 5  | IN               | Input for diagnostic shift register used to cascade several device.                                                          |

| 6  | CDE2             | Channel 2 output (connect to base ofdarlington). Up to 2.5 mA drive.                                                         |

| 7  | RM2              | Feedback input from sensing resistor of channel 2 darlington.                                                                |

| 8  | CDE1             | Channel 1 Output .                                                                                                           |

| 9  | RM1              | Feedback input for channel 1 sense resistor .                                                                                |

| 10 | GND              | Ground.                                                                                                                      |

| 11 | DROP             | Clock Input for Diagnostic Register.                                                                                         |

| 12 | RM3              | Feedback input for channel 3 sense resistor.                                                                                 |

| 13 | CDE3             | Channel 3 Output.                                                                                                            |

| 14 | RM4              | Feedback input for channel 4 sense resistor.                                                                                 |

| 15 | CDE4             | Channel 4 Output.                                                                                                            |

| 16 | OUT              | Output of Diagnostic Register.                                                                                               |

| 17 | DEC3             | Input for Channel 3.                                                                                                         |

| 18 | DEC4             | Input for Channel 4.                                                                                                         |

| 19 | CLK              | Input for clock signal which sets conduction time for all four channels.<br>$T_{on} = 128/f_{CLK}$ .                         |

| 20 | V <sub>ss</sub>  | 5 V Supply Input Voltage.                                                                                                    |

### FUNCTIONAL DESCRIPTION

The L6503 Hammer Solenoid Controller is designed to control a quad darlington array, such as the SGS-THOMSON L7180, in solenoid driving applications.

Compatible with 5 V microcomputer and peripheral chips, the L6503 is controlled by four logic inputs - one per channel ( $\overline{DEC1} - \overline{DEC4}$ ) - which are latched by a high-low transition on the DATA input.

When one of the channels is activated the corresponding darlington is driven, with up to 2.5 mA drive current. The conduction period is determined by the frequency applied to the CLK input which clocks the 7-bit timer in each channel. The conduction time is therefore 128/fCLK. Typically the CLK frequency will be of the order of 100KHz but the L6503's internal logic will operate at any clock rate within the range of practical conduction times.

During the conduction period the load current is controlled by feedback from a sense resistor in the

darlington's emitter and set by the voltage applied to the V<sub>ref</sub> input. The current depends on both the values of V<sub>ref</sub> and the sensing resistor :  $I = V_{ref}/R_{sense}$ .

The control microcomputer may verify correct operation of the complete drive subsystem thanks to a diagnostic circuit in the L6503. A four bit PISO shift register in the device monitors the feedback signals from the four output darlingtons and may be read serially after each command to check that the loads were driven.

Typically, this register, clocked by the DROP input, will be read a short time after each drive command has been latched into the device.

The input of this register (IN) is available externally so that multiple devices may be cascaded.

| Symbol          | Parameter                                           | Test Conditions                                             | Min.           | Тур. | Max.  | Unit |

|-----------------|-----------------------------------------------------|-------------------------------------------------------------|----------------|------|-------|------|

| V <sub>ss</sub> | Supply Voltage                                      | T <sub>j</sub> = 0 to 70 °C                                 | 4.75           | 5    | 5.25  | V    |

| l <sub>ss</sub> | Total Supply Current                                | I <sub>CDE</sub> = 2 mA<br>All Channels On                  |                | 75   | 90    | mA   |

| VREF            | Input Voltage Reference                             |                                                             | 1              |      | 2.4   | V    |

| VREF            | Reset Logic Function                                |                                                             | 0.3            |      | 0.65  | v    |

| IREF            | Input BIAS Reference Current                        | $V_{REF} = 0$ to 2.4 V                                      |                |      | - 5   | μA   |

| Vi              | Input Voltage (pin 1, 3, 4, 5, 11, 17, 18, 19)      | ViL                                                         |                |      | 0.4   | v    |

|                 |                                                     | ViH                                                         | 2.7            |      |       |      |

| Vout            | Output Logic Voltage (pin 16)                       | $V_{OL}$ $I_{OUT} = + 1.6$ mA                               |                |      | 0.4   | v    |

|                 |                                                     | $V_{OH} \qquad I_{OUT} = -100 \\ \mu A$                     | 2.7            |      |       |      |

| Ib              | Input Bias Current (pin 1, 3, 4, 5, 11, 17, 18, 19) | V <sub>IL</sub>                                             |                |      | - 100 |      |

|                 |                                                     | VIH                                                         |                |      | ± 10  | μΑ   |

| Iь              | Input Bias Current (pin 7, 9, 12, 14)               | $1 \le V_{RM} \le 2.4 V$                                    |                |      | - 100 | μA   |

| ICDE            | Output Current (pin 6, 8, 13, 15)                   | $V_{OUT} = V_{SS} - 0.5 V$                                  | 2.5            |      |       | mA   |

|                 | Output Voltage Range (pin 6, 8, 13, 15)             | V <sub>OL</sub>                                             |                |      | 0.2   | v    |

|                 |                                                     | V <sub>он</sub>                                             | $V_{ss} - 0.5$ |      |       |      |

|                 | Error Amplifier Input Offset Voltage                | $1 \text{ V} \leq \text{V}_{\text{REF}} \leq 2.4 \text{ V}$ |                |      | ± 10  | mV   |

# **ELECTRICAL** CHARACTERISTICS ( $V_{SS} = 5 V$ , $T_{amb} = 25 \text{ °C}$ , unless otherwise specified)

# TIMING SECTION

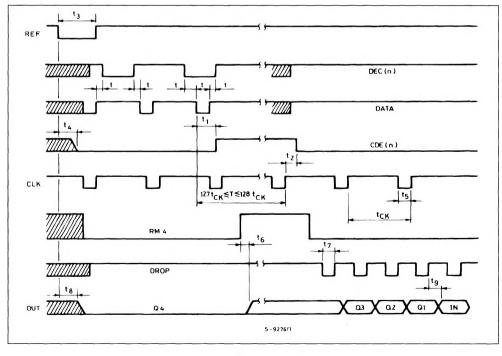

| Da  | ata Ability Time t               |                       | 160 |     |     | ns  |

|-----|----------------------------------|-----------------------|-----|-----|-----|-----|

| Da  | ata to CDE Delay Time t1 (1)     | V <sub>RM</sub> = 0 V |     | 0.8 | 1.5 | μs  |

| Cl  | ock to CDE Delay Time t2 (1)     | V <sub>RM</sub> = 0 V |     | 7   | 10  | μs  |

| Re  | eset Time t3                     |                       | 1.9 |     |     | μs  |

| Re  | eset to CDE Delay Time t4 (1)    |                       |     |     | 1.3 | μs  |

| Cli | ock Frequency                    |                       |     |     | 100 | KHz |

| Lo  | w Level Clock State t5 (1)       |                       | 500 |     |     | ns  |

| RM  | I to OUT Delay Time t6 (1)       |                       |     |     | 3   | μs  |

| Dr  | op Frequency                     |                       |     |     | 500 | KHz |

| Lo  | w Level Drop State t7            |                       | 500 |     |     | ns  |

| Re  | eset to Output Delay Time t8 (1) |                       |     |     | 1.3 | μs  |

| Dr  | op to in Delay.Time t9 (1)       |                       |     |     | 1.0 | μs  |

(1) 100% Tested

# Figure 1 : Application Diagram.

Figure 2 : Timing Diagram.