#

# CMOS 10-Bit A/D Converter with Track-and-Hold

#### **General Description**

The MAX177 is a complete CMOS sampling 10-bit analog-to-digital converter (ADC) that combines an on-chip track-and-hold and voltage reference along with high conversion speed and low power consumption. A conversion time of 8.33 $\mu$ s includes settling time for the track-and-hold. An internal buried zener reference provides low drift with low noise.

The MAX177 accepts -2.5V to +2.5V inputs. External components are limited to only decoupling capacitors for the power supply and reference voltages. On-chip clock circuitry can either be driven from an external clock source or a crystal.

The MAX177 employs a standard microprocessor interface. Three-state data outputs can be configured for 8- or 12-bit data buses. Data access and bus release timing specs are compatible with most popular microprocessors without resorting to wait states

#### **Applications**

Digital Signal Processing (DSP) Audio and Telecom Processing High Accuracy Process Control High Speed Data Acquisition

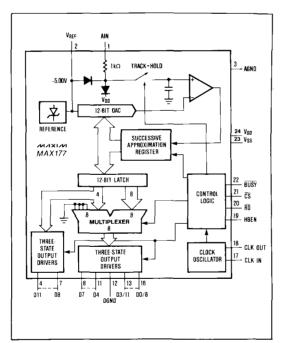

### Functional Diagram

#### Features

- 12-Bit Resolution and 10-Bit Linearity

- 8.33µs Conversion Time

- Internal Analog Track-Hold

- 6MHz Full Power Bandwidth

- On-Chip ±40ppm/°C Voltage Reference

- High Input Resistance (500M $\Omega$ )

- 100ns Data Access Time

- 180mW (Max) Power Consumption

- ♦ 24 Lead Narrow DIP and Wide SO Packages

#### **Ordering Information**

| PART      | TEMP. RANGE     | PACKAGE*    | ERROR  |

|-----------|-----------------|-------------|--------|

| MAX177CNG | 0°C to +70°C    | Plastic DIP | ±1 LSB |

| MAX177CWG | 0°C to +70°C    | Wide SO     | ±1 LSB |

| MAX177C/D | 0°C to +70°C    | Dice**      | ±1 LSB |

| MAX177ENG | -40°C to +85°C  | Plastic DIP | ±1 LSB |

| MAX177EWG | -40°C to +85°C  | Wide SO     | ±1 LSB |

| MAX177MRG | -55°C to +125°C | CERDIP      | ±1 LSB |

- \* All devices 24 lead packages

\*\* Consult factory for dice specifications.

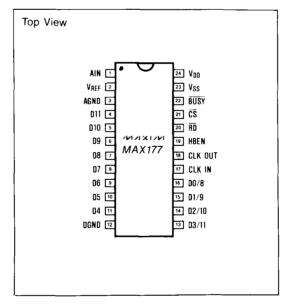

### Pin Configuration

/VI/IXI/VI

**Maxim Integrated Products 1**

ered trademark of Maxim Integrated Products.

3

# CMOS 10-Bit A/D Converter with Track-and-Hold

**ELECTRICAL CHARACTERISTICS (continued)** ( $V_{DO} = +5V \pm 5\%$ ,  $V_{SS} = -11.4V$  to -15.75V, Slow Memory Mode,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $f_{CLK} = 1.5MHz$  unless otherwise noted.)

| PARAMETER                                  | SYMBOL          | CONDITIONS                                                                                                  |                                                      | MIN | TYP   | MAX      | UNITS |

|--------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|-------|----------|-------|

| LOGIC INPUTS                               | •               |                                                                                                             |                                                      | •   |       |          |       |

| Input Low Voltage                          | VIL             | CS, RD, HBEN,                                                                                               | CLK IN                                               |     |       | 0.8      | V     |

| Input High Voltage                         | V <sub>IH</sub> | CS, RD, HBEN,                                                                                               | CLK IN                                               | 2.4 |       |          | V     |

| Input Capacitance (Note 4)                 | CIN             | CS, RD, HBEN,                                                                                               | CLK IN                                               |     |       | 10       | pF    |

| Input Current                              | I <sub>IN</sub> | V <sub>IN</sub> = 0V to V <sub>DD</sub>                                                                     |                                                      |     |       | 10<br>20 | μΑ    |

| LOGIC OUTPUTS                              |                 | •                                                                                                           |                                                      |     |       |          |       |

| Output Low Voltage                         | V <sub>OL</sub> | D11-D0/8, BUSY<br>I <sub>SINK</sub> = 1.6mA                                                                 | D11-D0/8, BUSY, CLK OUT<br>I <sub>SINK</sub> = 1.6mA |     |       | 0.4      | V     |

| Output High Voltage                        | V <sub>OH</sub> | D11-D0/8, BUSY, CLK OUT<br>I <sub>SOURCE</sub> = 200 <i>μ</i> A                                             |                                                      | 4   |       |          | V     |

| Three-State<br>Leakage Current             | ار              | D11-D0/8, V <sub>OUT</sub> = 0V to V <sub>DD</sub>                                                          |                                                      |     |       | ±10      | μΑ    |

| Three-State Output<br>Capacitance (Note 4) | co              | , , , ,                                                                                                     |                                                      |     |       | 15       | pF    |

| POWER REQUIREMENTS                         |                 |                                                                                                             |                                                      |     |       |          |       |

| Postive Supply Voltage                     | V <sub>DD</sub> | ±5% For Specif                                                                                              | ied Performance                                      |     | 5     |          | V     |

| Negative Supply Voltage                    | V <sub>ss</sub> | ±5% For Specif                                                                                              | ied Performance                                      | -12 |       | -15      | ٧     |

| Positive Supply Rejection                  |                 | FS Change, V <sub>SS</sub> = -15V or -12V<br>V <sub>DD</sub> = 4.75 to 5.25V                                |                                                      |     | ±0.01 |          | %     |

| Negative Supply Rejection                  |                 | FS Change, V <sub>DD</sub> = 5V<br>V <sub>SS</sub> = -14.24 to -15.75V<br>V <sub>SS</sub> = -11.4 to -12.6V |                                                      |     | ±0.01 |          | %     |

| Positive Supply Current                    | I <sub>DD</sub> | $\overline{CS} = \overline{RD} = V_{DD}$ , AIN = 5V                                                         |                                                      |     | 4     | 6        | mA    |

| Negative Supply Current                    | I <sub>ss</sub> | CS = RD = V <sub>DD</sub> ,                                                                                 | AIN = 5V                                             |     | 7     | 10       | mA    |

| Power Dissipation                          |                 | V <sub>DD</sub> = +5V, V <sub>SS</sub> =                                                                    | -12V                                                 |     | 104   | 150      | mW    |

- Note 1: Typical change over temp is ±1mV.

Note 2: Ideal last code transition = FS -1.8mV LSB, adjusted for offset.

Note 3: Full Scale Tempco = dFS/dT, where dFS is full scale change from T<sub>A</sub> = 25°C to T<sub>MIN</sub> or T<sub>MAX</sub>.

Note 4: Guaranteed by design, not subject to test.

Note 5: V<sub>REF</sub> Tempco = dV<sub>REF</sub>/dT, where dV<sub>REF</sub> is reference voltage change from T<sub>A</sub> = 25°C to T<sub>MIN</sub>T<sub>MAX</sub>.

Note 6: All input control signals are specified with t<sub>r</sub> = t<sub>f</sub> = 5ns (10% to 90% of +5V) and timed from a voltage level of +1.6V.

Note 7: This specification is 100% production tested.

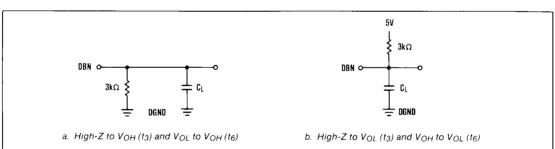

Note 8: t<sub>3</sub> and t<sub>6</sub> are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V

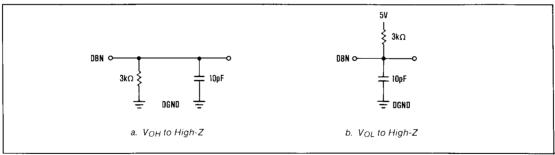

- Note 9:  $t_7$  is defined as the time required for the data line to change 0.5V when loaded with the circuits of Figure 2.

For additional information on using the MAX177, please refer to MAX163/164/167 data sheet.

| /VI/IXI/VI _ |      |      |  |

|--------------|------|------|--|

| /VI/1 ~ I/VI | <br> | <br> |  |

# CMOS 10-Bit A/D Converter with Track-and-Hold

**ELECTRICAL CHARACTERISTICS (continued)**  $(V_{DD} = +5V \pm 5\%, V_{SS} = -11.4V \text{ to } -15.75V, \text{ Slow Memory Mode, } T_A = T_{MIN} \text{ to } T_{MAX}, f_{CLK} = 1.5MHz \text{ unless otherwise noted.})$

| PARAMETER                                  | SYMBOL          | CONDITIONS                                                                                 |                                                                              | MIN | TYP   | MAX      | UNITS |

|--------------------------------------------|-----------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----|-------|----------|-------|

| LOGIC INPUTS                               | _               |                                                                                            |                                                                              |     |       |          | •     |

| Input Low Voltage                          | VIL             | CS, RD, HBEN,                                                                              | CLK IN                                                                       |     |       | 0.8      | V     |

| Input High Voltage                         | V <sub>IH</sub> | CS, RD, HBEN,                                                                              | CLK IN                                                                       | 2.4 |       |          | V     |

| Input Capacitance (Note 4)                 | CIN             | CS, RD, HBEN,                                                                              | CS, RD, HBEN, CLK IN                                                         |     |       | 10       | pF    |

| Input Current                              | I <sub>IN</sub> | V <sub>IN</sub> = 0V to V <sub>DD</sub> CS, RD, HBEN CLK IN                                |                                                                              |     |       | 10<br>20 | μΑ    |

| LOGIC OUTPUTS                              |                 |                                                                                            |                                                                              |     |       |          |       |

| Output Low Voltage                         | V <sub>OL</sub> | D11-D0/8, BUSY<br>I <sub>SINK</sub> = 1.6mA                                                | D11-D0/8, BUSY, CLK OUT<br>SINK = 1.6mA                                      |     |       | 0.4      | V     |

| Output High Voltage                        | V <sub>OH</sub> | D11-D0/8, BUS\<br>I <sub>SOURCE</sub> = 200μΑ                                              | D11-D0/8, BUSY, CLK OUT<br>I <sub>SOURCE</sub> = 200 <i>µ</i> A              |     |       |          | V     |

| Three-State<br>Leakage Current             | ار              |                                                                                            | D11-D0/8, V <sub>OUT</sub> = 0V to V <sub>DD</sub>                           |     |       | ±10      | μΑ    |

| Three-State Output<br>Capacitance (Note 4) | co              |                                                                                            |                                                                              |     |       | 15       | pF    |

| POWER REQUIREMENTS                         | •               |                                                                                            |                                                                              |     |       |          |       |

| Postive Supply Voltage                     | V <sub>DD</sub> | ±5% For Specif                                                                             | ied Performance                                                              |     | 5     |          | V     |

| Negative Supply Voltage                    | V <sub>SS</sub> | ±5% For Specif                                                                             | ied Performance                                                              | -12 |       | -15      | V     |

| Positive Supply Rejection                  |                 | FS Change, V <sub>SS</sub><br>V <sub>DD</sub> = 4.75 to 5.2                                | FS Change, V <sub>SS</sub> = -15V or -12V<br>V <sub>DD</sub> = 4.75 to 5.25V |     | ±0.01 |          | %     |

| Negative Supply Rejection                  |                 | FS Change, $V_{DD} = 5V$<br>$V_{SS} = -14.24$ to $-15.75V$<br>$V_{SS} = -11.4$ to $-12.6V$ |                                                                              |     | ±0.01 |          | %     |

| Positive Supply Current                    | I <sub>DD</sub> | CS = RD = V <sub>DD</sub> , AIN = 5V                                                       |                                                                              |     | 4     | 6        | mA    |

| Negative Supply Current                    | I <sub>ss</sub> | CS = RD = V <sub>DD</sub> , AIN = 5V                                                       |                                                                              |     | 7     | 10       | mA    |

| Power Dissipation                          |                 | V <sub>DD</sub> = +5V, V <sub>SS</sub> =                                                   | -12V                                                                         |     | 104   | 150      | mW    |

- Note 1: Typical change over temp is ±1mV.

Note 2: Ideal last code transition = FS -1.8mV LSB, adjusted for offset.

Note 3: Full Scale Tempco = dFS/dT, where dFS is full scale change from T<sub>A</sub> = 25°C to T<sub>MIN</sub> or T<sub>MAX</sub>.

Note 4: Guaranteed by design, not subject to test.

Note 5: V<sub>REF</sub> Tempco = dV<sub>REF</sub>/dT, where dV<sub>REF</sub> is reference voltage change from T<sub>A</sub> = 25°C to T<sub>MIN</sub>T<sub>MAX</sub>.

Note 6: All input control signals are specified with t<sub>f</sub> = t<sub>f</sub> = 5ns (10% to 90% of +5V) and timed from a voltage level of +1.6V.

Note 7: This specification is 100% production tested.

- Note 8: t<sub>3</sub> and t<sub>6</sub> are measured with the load circuits of Figure 1 and defined as the time required for an output to cross 0.8V or 2.4V.

- Note 9: 17 is defined as the time required for the data line to change 0.5V when loaded with the circuits of Figure 2.

For additional information on using the MAX177, please refer to MAX163/164/167 data sheet.

| /VI/IXI/VI                            | <br> | 3 |

|---------------------------------------|------|---|

| , , , , , , , , , , , , , , , , , , , | <br> |   |

# CMOS 10-Bit A/D Converter with Track-and-Hold

TIMING CHARACTERISTICS ( $V_{DD} = +5V$ ,  $V_{SS} = -12V$  or -15V,  $V_{A} = V_{MIN}$  to  $V_{MAX}$ , Note 6, specifications in bold type are 100% tested, others are guaranteed by design, unless otherwise noted.)

| PARAMETER                                  | SYMBOL          | CONDITIONS    |     | A = 25 | °C<br>MAX | MAX1<br>MIN | 77C/E<br>MAX | MAX<br>MIN | 177M<br>MAX | UNITS |

|--------------------------------------------|-----------------|---------------|-----|--------|-----------|-------------|--------------|------------|-------------|-------|

| CS to RD Setup Time                        | t <sub>1</sub>  |               | 0   |        |           | 0           |              | 0          |             | ns    |

| RD to BUSY Delay<br>(Note 7)               | t <sub>2</sub>  | CL = 50pF     |     | 80     | 170       |             | 220          |            | 260         | ns    |

| Data Access Time<br>(Notes 7, 8)           | t <sub>3</sub>  | CL = 100pF    |     | 50     | 100       |             | 130          |            | 150         | ns    |

| RD Pulse Width                             | t <sub>4</sub>  |               | 100 |        |           | 130         |              | 150        | -           | ns    |

| CS to RD Hold Time                         | t <sub>5</sub>  |               | 0   |        |           | 0           |              | 0          |             | ns    |

| Data Setup Time After<br>BUSY (Notes 7, 8) | t <sub>6</sub>  |               |     | 40     | 80        |             | 105          |            | 120         | ns    |

| Bus Relinquish Time<br>(Notes 7, 9)        | t <sub>7</sub>  |               |     | 30     | 50        |             | 65           |            | 75          | ns    |

| HBEN to RD Setup Time                      | t <sub>8</sub>  |               | 0   |        |           | 0           |              | 0          |             | ns    |

| HBEN to RD Hold Time                       | t <sub>9</sub>  |               | 0   |        |           | 0           |              | 0          |             | ns    |

| Delay Between<br>READ Operations           | t <sub>10</sub> |               | 200 |        |           | 200         |              | 200        |             | ns    |

| Delay Between<br>Conversions               | t <sub>11</sub> |               | 1   |        |           | 1           |              | 1          |             | μs    |

| Aperture Delay                             | t <sub>12</sub> | Jitter < 50ps |     | 25     |           |             |              |            |             | ns    |

Figure 1. Load Circuits for Access Time

Figure 2. Load Circuits for Bus Relinquish Time

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied.

Maxim reserves the right to change the circuitry and specifications without notice at any time.