### **General Description**

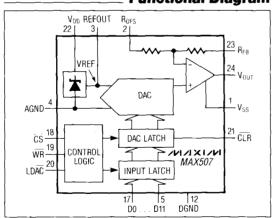

The MAX507/MAX508 are complete 12-bit, voltageoutput digital-to-analog converters (DACs). The DAC output voltage and the reference have the same polarity, allowing single-supply operation. Both DACs include an internal buried-zener reference. Integrating a DAC, voltage-output amplifier, and reference on one monolithic device greatly enhances reliability over multi-chip circuits.

Double-buffered logic inputs interface easily to microprocessors (µPs). Data is transferred into the input register either from a 12-bit-wide data bus (MAX507) for 16-bit µPs, or in a right-justified (8+4)-bit format (MAX508) for 8- or 16-bit µPs. All logic signals are level triggered and are TTL and CMOS compatible. Interface timing specifications insure compatibility with all common  $\mu Ps$ .

The DACs are specified and tested for both dual- and single-supply operation. Usable supplies range from single +12V to dual  $\pm$ 15V.

On-board gain-setting resistors allow three outputvoltage ranges: 0V to +5V and 0V to +10V can be generated when using either single or dual supplies. With dual supplies, ±5V is also available. The output amplifier can drive a  $2k\Omega$  load to +10V.

# **Applications**

Digital Offset and Gain Adjustment Industrial Controls Arbitrary Function Waveform Generators **Automatic Test Equipment Automated Calibration** Machine and Motion Control

## Features

*MAX507/MAX508*

- ♦ 12-Bit Voltage Output

- ♦ Internal Voltage Reference

- ♦ Fast μP Interface

- ♦ 12 (MAX507) and 8+4 (MAX508) Data-Bus Widths

- ♦ Single +12V to Dual ±15V Supply Operation

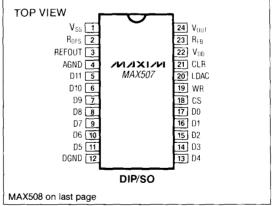

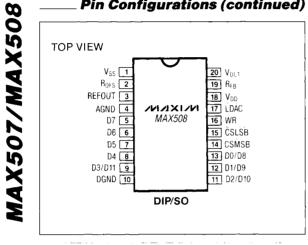

- ♦ 20- and 24-Pin DIP and Wide SO Packages

# **Ordering Information**

| PART       | TEMP. RANGE     | PIN-<br>PACKAGE       | ERROR<br>(LSBs) |

|------------|-----------------|-----------------------|-----------------|

| MAX507ACNG | 0°C to +70°C    | 24 Narrow Plastic DIP | ±1/2            |

| MAX507BCNG | 0°C to +70°C    | 24 Narrow Plastic DIP | ±3/4            |

| MAX507ACWG | 0°C to +70°C    | 24 Wide SO            | ±1/2            |

| MAX507BCWG | 0°C to +70°C    | 24 Wide SO            | ±3/4            |

| MAX507BC/D | 0°C to +70°C    | Dice*                 | ±3/4            |

| MAX507AENG | -40°C to +85°C  | 24 Narrow Plastic DIP | ±1/2            |

| MAX507BENG | -40°C to +85°C  | 24 Narrow Plastic DIP | ±3/4            |

| MAX507AEWG | -40°C to +85°C  | 24 Wide SO            | ±1/2            |

| MAX507BEWG | -40°C to +85°C  | 24 Wide SO            | ±3/4            |

| MAX507AMRG | -55°C to +125°C | 24 Narrow CERDIP**    | ±1/2            |

| MAX507BMRG | -55°C to +125°C | 24 Narrow CERDIP**    | ±3/4            |

# Ordering Information continued on page 12.

- Contact factory for dice specifications.

Contact factory for availability and processing to MIL-STD-883.

# **Functional Diagram**

# Pin Configurations

/VI/IXI/VI \_

Maxim Integrated Products 1

/VI/IXI/VI is a registered trademark of Maxim Integrated Products.

# **ABSOLUTE MAXIMUM RATINGS**

| VDD to AGND       -0.3V, +17V         VDD to DGND       -0.3V, +17V         VDD to VSS       -0.3V, +34V         AGND to DGND       -0.3V, VDD                                                                                                                                                                                                       | Continuous Power Dissipation (any package) to +75°C                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Input Voltage to GND       -0.3V, V <sub>DD</sub> +0.3V         V <sub>OUT</sub> to AGND (Note 1)       V <sub>SS</sub> , V <sub>DD</sub> V <sub>OUT</sub> to V <sub>SS</sub> (Note 1)       0V, +34V         V <sub>OUT</sub> to V <sub>DD</sub> (Note 1)       -34V, 0V         REFOUT to AGND (Note 1)       -0.3V, V <sub>DD</sub> +0.3V | MAX507_C, MAX508_C       0°C to +70°C         MAX507_E, MAX508_E       -40°C to +85°C         MAX507_M, MAX508_M_       -55°C to +125°C         Storage Temperature Range       -65°C to +150°C         Lead Temperature (soldering, 10 sec)       +300°C |

Note 1: The output can be shorted to either supply rail if the package power dissipation is not exceeded. Typical short-circuit current to AGND is 25mA.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

Single Supply ( $V_{DD}$  = +11.4V to +15.75V,  $V_{SS}$  = AGND = DGND = 0V,  $R_L$  = 2k $\Omega$ ,  $C_L$  = 100pF, REFOUT unloaded, all grades,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                        | SYMBOL | CONDITIONS                                |                         | MIN | TYP | MAX   | UNITS        |  |

|----------------------------------|--------|-------------------------------------------|-------------------------|-----|-----|-------|--------------|--|

| STATIC PERFORMANCE               |        | -                                         |                         | •   |     |       | •            |  |

| Resolution                       | N      |                                           |                         | 12  |     |       | Bits         |  |

| Relative Accuracy                |        | T .0500                                   | MAX507/508A             |     |     | ±1/2  |              |  |

|                                  | INII   | T <sub>A</sub> = +25°C                    | MAX507/508B             |     |     | ±3/4  | 1.00         |  |

|                                  | INL    | T T to T                                  | MAX507/508A             |     |     | ±3/4  | LSB          |  |

|                                  |        | TA = TMIN to TMAX                         | MAX507/508B             |     |     | ±1    | 1            |  |

| Differential Nonlinearity        | DNL    |                                           |                         |     |     | ±1    | LSB          |  |

| Uninclar Officet Error           |        | T <sub>A</sub> = +25° C                   |                         |     |     | ±3    | LSB          |  |

| Unipolar Offset Error            |        | TA = TMIN to TMAX                         |                         |     |     | ±5    | LSB          |  |

| DAC Gain Error                   |        |                                           |                         |     |     | ±2    | LSB          |  |

| Full-Scale Output Voltage Error  |        | 101                                       | T <sub>A</sub> = +25° C |     |     | ±0.2  | %FSR         |  |

| Full-Scale Output Voltage Error  |        | V <sub>DD</sub> = +12V or +15V            | TA = TMIN to TMAX       |     |     | ±0.6  | 7 %FSR       |  |

| Full Scale Output Valtage Change |        | V supr full rongs                         | T <sub>A</sub> = +25° C |     |     | ±0.12 | W ECD A      |  |

| Full-Scale Output Voltage Change |        | V <sub>DD</sub> over full range           | TA = TMIN to TMAX       |     |     | ±0.2  | -∤%FSR/\<br> |  |

| Full Cools Towns                 |        | MAX507/508_C/E                            | •                       |     |     | ±30   | ppm          |  |

| Full-Scale Tempco                |        | MAX507/508_M                              |                         |     |     | ±40   | FŚŔ/°C       |  |

| Unipolar Offset Error Change     |        | $V_{DD}$ = +12V $\pm$ 5% or +15V $\pm$ 5% |                         |     |     | ±1    | mV           |  |

\_\_\_\_\_/VI/XI/VI

**ELECTRICAL CHARACTERISTICS (continued)** Single Supply ( $V_{DD}$  = +11.4V to +15.75V,  $V_{SS}$  = AGND = DGND = 0V,  $R_L$  = 2k $\Omega$ ,  $C_L$  = 100pF, REFOUT unloaded, all grades,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                        | SYMBOL    | CON                                | DITIONS                 | MIN  | TYP | MAX     | UNITS    |

|----------------------------------|-----------|------------------------------------|-------------------------|------|-----|---------|----------|

| REFERENCE                        |           |                                    |                         |      |     |         | 1        |

| Reference Output                 |           | V <sub>DD</sub> = +12V or +15V     | T <sub>A</sub> = +25° C | 4.99 |     | 5.01    | V        |

| Reference Voltage Change         |           | $V_{DD}$ = +12V ± 5% or            | T <sub>A</sub> = +25°C  |      |     | 2       |          |

| neleterice voltage Change        | +15V ± 5% | TA = TMIN to TMAX                  |                         |      | 6   | mV/V    |          |

| Reference Temperature            |           | MAX507/508_C/E                     |                         |      | ±30 |         | ppm/°C   |

| Coefficient                      |           | MAX507/508_M                       |                         |      | ±40 |         | ppin/- c |

| Reference Load Sensitivity       |           | $I_{LOAD} = 0\mu A$ to $100\mu A$  | ·                       |      |     | ±1      | mV       |

| ANALOG OUTPUT                    |           |                                    |                         |      |     |         |          |

| Ranges (Note 2)                  |           |                                    |                         |      |     | 0 to 5  | V        |

|                                  | _         |                                    |                         |      |     | 0 to 10 |          |

| Output Range Resistors           |           |                                    |                         | 15   |     | 30      | kΩ       |

| DC Output Impedance              |           |                                    |                         |      | 0.5 |         | Ω        |

| Short-Circuit Current            |           |                                    |                         |      | 40  |         | mA       |

| <b>DYNAMIC PERFORMANCE</b> (Note | 3)        |                                    |                         |      |     |         |          |

| Voltage-Output Slew Rate         |           |                                    |                         | 2    |     |         | V/μs     |

| VOUT Settling Time               |           | To $\pm$ 1/2 LSB for full-s        | scale change            |      |     | 5       | μs       |

| Digital Feedthrough              |           |                                    |                         |      | 10  |         | nV-s     |

| Digtal-to-Analog Glitch Impulse  |           | Major carry transition             | 1                       | T    | 30  |         | nV-s     |

| Output Load Resistance (Note 2)  |           | V <sub>OUT</sub> = 0V to +10V      |                         | 2    |     |         | kΩ       |

| POWER SUPPLIES                   |           |                                    |                         |      |     |         |          |

| V <sub>DD</sub> Range            |           | For specified performance          |                         | 11.4 |     | 15.75   | V        |

| Ipp                              |           | Outputs uploaded                   | T <sub>A</sub> = +25° C |      |     | 9       | mA       |

| טטי                              |           | Outputs unloaded TA = TMIN to TMAX |                         |      |     | 12      | ] IIIA   |

**ELECTRICAL CHARACTERISTICS**Dual Supply ( $V_{DD}$  = +11.4V to +15.75V,  $V_{SS}$  = -11.4V to -15.75V, DGND = AGND = 0V,  $R_L$  = 2k $\Omega$ ,  $C_L$  = 100pF, REFOUT unloaded, all grades,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                     | SYMBOL | CONDITIONS                                                                 |                        | MIN  | TYP | MAX   | UNITS        |

|-----------------------------------------------|--------|----------------------------------------------------------------------------|------------------------|------|-----|-------|--------------|

| STATIC PERFORMANCE                            |        | <del>-</del>                                                               |                        |      |     |       |              |

| Resolution                                    | N      |                                                                            |                        | 12   |     |       | Bits         |

|                                               |        | 7                                                                          | MAX507/508A            |      |     | ±1/2  |              |

| - · · · ·                                     |        | T <sub>A</sub> = +25°C                                                     | MAX507/508B            |      |     | ±3/4  | T            |

| Relative Accuracy                             | INL    |                                                                            | MAX507/508A            |      |     | ±3/4  | LSB          |

|                                               |        | $T_A = T_{MIN}$ to $T_{MAX}$                                               | MAX507/508B            | 1    |     | ±1    | 1            |

| Differential Nonlinearity                     | DNL    |                                                                            |                        |      |     | ±1    | LSB          |

| Disabet 7 and 6 feet 5                        |        | MAN VEO 7/EO QA                                                            | T <sub>A</sub> = +25°C |      |     | ±2    |              |

|                                               | BZOE   | MAX507/508A                                                                | TA = TMIN to TMAX      |      |     | ±4    | 1            |

| Bipolar Zero Offset Error                     | BZUE   | MAX507/508B                                                                | T <sub>A</sub> = +25°C |      |     | ±3    | LSB          |

|                                               |        | MAX201/208B                                                                | TA = TMIN to TMAX      |      |     | ±5    | 1            |

| DAC Gain Error                                |        |                                                                            |                        |      |     | ±2    | LSB          |

|                                               |        | V <sub>DD</sub> = +15V,                                                    | T <sub>A</sub> = +25°C |      |     | ±0.2  |              |

| Full-Scale Output Voltage Error               |        | V <sub>DD</sub> = +12V,                                                    | TA = TMIN to TMAX      |      |     | ±0.6  | %FSR         |

|                                               |        |                                                                            | T <sub>A</sub> = +25°C |      |     | ±0.2  |              |

|                                               |        | V <sub>SS</sub> = -12V                                                     | TA = TMIN to TMAX      |      |     | ±0.6  |              |

| Full-Scale Output Change                      |        | $V_{DD}$ = +12V ± 5% or<br>+15V ± 5%<br>$V_{SS}$ = -12V or -15V            | T <sub>A</sub> = +25°C |      |     | ±0.12 | 0/ 500 /     |

| with V <sub>DD</sub>                          |        |                                                                            | TA = TMIN to TMAX      |      |     | ±0.2  | ⊣%FSR/\      |

| Full-Scale Output Change with V <sub>SS</sub> | Vss    | $V_{SS}$ = -12V $\pm$ 5% or -<br>$V_{DD}$ = +12V or +5V                    | 15V ± 5%               |      |     | 0.01  | %FSR/\       |

| F. II Cools Town                              |        | MAX507/508_C/E                                                             |                        |      |     | ±30   | ppm          |

| Full-Scale Tempco                             |        | MAX507/508_M                                                               |                        |      |     | ±40   | FSR/°C       |

| Dinalay Zaya Officet Ohanna                   |        | V <sub>DD</sub> = +12V ± 5% or +15V ± 5%<br>V <sub>SS</sub> = -12V or -15V |                        |      |     | ±1    |              |

| Bipolar Zero Offset Change                    |        | V <sub>SS</sub> = -12V ± 5% or -15V ± 5%<br>V <sub>DD</sub> = +12V or +15V |                        |      |     | ±1    | ⊣ mV         |

| REFERENCE                                     | •      | •                                                                          |                        | •    |     |       | <del>-</del> |

| Reference Output                              |        | V <sub>DD</sub> = +12V or +15V                                             | T <sub>A</sub> = +25°C | 4.99 |     | 5.01  | _ v          |

| Peferance Output Change                       |        | Van over full rease                                                        | T <sub>A</sub> = +25°C |      |     | 2     | m)//\/       |

| Reference Output Change                       |        | V <sub>DD</sub> over full range                                            | TA = TMIN to TMAX      |      |     | 6     | mV/V         |

| Reference Temperature                         |        | MAX507/508_C/E                                                             |                        |      | ±30 |       | /0/          |

| Coefficient                                   |        | MAX507/508_M                                                               |                        |      | ±40 |       | ppm/°C       |

|                                               |        | I <sub>LOAD</sub> = 0μA to 100μA                                           |                        |      |     |       |              |

\_ /VI/IXI/Vi

ELECTRICAL CHARACTERISTICS (continued) Dual Supply ( $V_{DD}$  = +11.4V.to +15.75V,  $V_{SS}$  = -11.4V to -15.75V, DGND = AGND = 0V,  $R_L$  = 2k $\Omega$ ,  $C_L$  = 100pF, REFOUT unloaded, all grades,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                       | SYMBOL | CON                            | DITIONS                   | MIN  | TYP                   | MAX    | UNITS |

|---------------------------------|--------|--------------------------------|---------------------------|------|-----------------------|--------|-------|

| ANALOG OUTPUT                   | -      | -                              |                           |      |                       |        |       |

| Ranges (Notes 2, 4)             |        |                                |                           | 0 1  | o +5 or +<br>-5 to +5 |        | ٧     |

| Output Range Resistors          |        |                                |                           | 15   |                       | 30     | kΩ    |

| DC Output Impedance             |        |                                |                           |      | 0.5                   |        | Ω     |

| Short-Circuit Current           |        |                                |                           |      | 40                    |        | mA    |

| DYNAMIC PERFORMANCE (Note       | e 3)   |                                |                           |      |                       |        |       |

| Voltage-Output Slew Rate        |        |                                |                           | 2    |                       |        | V/μs  |

| Vour Settling Time              |        | to ±1/2 LSB                    |                           |      |                       | 5      | μs    |

| Digital Feedthrough             |        |                                |                           |      | 10                    |        | nV-s  |

| Digtal-to-Analog Glitch Impulse |        | Major carry transitio          | n                         |      | 30                    |        | nV-s  |

| Output Load Resistance          |        | V <sub>OUT</sub> = -5V to +10V |                           | 2    |                       |        | kΩ    |

| POWER SUPPLIES                  | 1      |                                |                           |      |                       |        |       |

| V <sub>DD</sub> Range           |        | For specified perfori          | mance                     | 11.4 |                       | 15.75  | V     |

| Vss Range                       |        | For specified perform          | For specified performance |      |                       | -15.75 | V     |

|                                 |        | 0 1 1 1 1 1 1 1 1              | T <sub>A</sub> = +25°C    |      |                       | 9      |       |

| IDD                             |        | Outputs unloaded               | TA = TMIN to TMAX         |      |                       | 12     | mA    |

|                                 |        | 6                              | T <sub>A</sub> = +25° C   |      |                       | 3      | ^     |

| Iss                             |        | Outputs unloaded               | TA = TMIN to TMAX         |      |                       | 5      | mA    |

# MAX507/MAX508

# Voltage-Output, 12-Bit DACs with Internal Reference

## **ELECTRICAL CHARACTERISTICS**

Single or Dual Supply ( $V_{DD}$  = +11.4V to +15.75V,  $V_{SS}$  = 0V to -15.75V, DGND = AGND = 0V, REFOUT unloaded,  $R_L$  =  $2k\Omega$ ,  $C_L$  = 100pF, all grades,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                 | SYMBOL          | CONDITIONS        |                        | MIN | TYP | MAX  | UNITS |

|---------------------------|-----------------|-------------------|------------------------|-----|-----|------|-------|

| DIGITAL INPUTS            |                 | <del></del>       |                        | •   |     |      |       |

| VINH                      |                 |                   |                        | 2.4 |     |      | V     |

| VINL                      |                 |                   |                        |     |     | 8.0  | V     |

| Innut Current             | 1               | D0-D11            | T <sub>A</sub> = +25°C |     |     | ±1   | μΑ    |

| Input Current             | IIN             |                   | TA = TMIN to TMAX      |     |     | ±10  |       |

| 1                         |                 | CS, WR, LDAC, CLR | T <sub>A</sub> = +25°C |     |     | ±1   |       |

| INH                       |                 | CS, WH, LDAC, CLR | TA = TMIN to TMAX      |     |     | ±10  | μΑ    |

| 1                         |                 | CS, WR, LDAC, CLR | T <sub>A</sub> = +25°C |     |     | ±150 |       |

| INL                       | CS, WH, EDAC, C |                   | TA = TMIN to TMAX      |     |     | ±200 | μΑ    |

| Digital Input Capacitance |                 |                   |                        |     | 8   |      | pF    |

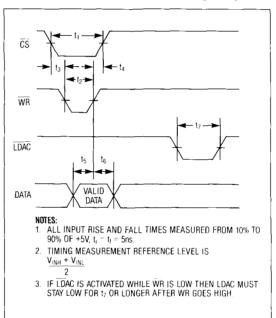

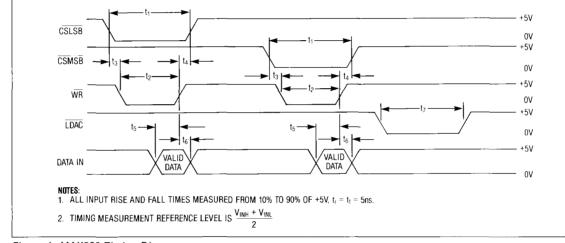

### **TIMING CHARACTERISTICS**

(All grades,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                    | SYMBOL         | CONDITIONS              | MIN | TYP | MAX | UNITS |  |

|------------------------------|----------------|-------------------------|-----|-----|-----|-------|--|

| OC Bules Width (Note 5)      | 4.             | T <sub>A</sub> = +25°C  | 80  |     |     |       |  |

| CS Pulse Width (Note 5)      | t <sub>1</sub> | TA = TMIN to TMAX       | 100 |     |     | ns    |  |

| WD Dules Width               |                | T <sub>A</sub> = +25° C | 80  |     |     |       |  |

| WR Pulse Width               | t <sub>2</sub> | TA = TMIN to TMAX       | 100 |     |     | ns    |  |

| CS to WR Setup Time (Note 5) | t <sub>3</sub> |                         | 0   |     |     | ns    |  |

| CS to WR Hold Time (Note 5)  | t4             |                         | 0   |     |     | ns    |  |

|                              | t <sub>5</sub> | T <sub>A</sub> = +25° C | 100 |     |     |       |  |

| Data to WR Setup Time        |                | TA = TMIN to TMAX       | 110 |     |     | ns    |  |

| Data to WR Hold Time         | t <sub>6</sub> |                         | 10  |     |     | ns    |  |

| T DAG Date - Wilde           |                | T <sub>A</sub> = +25°C  | 80  |     |     | ns    |  |

| LDAC Pulse Width             | t <sub>7</sub> | TA = TMIN to TMAX       | 100 |     |     |       |  |

| 0.00                         |                | T <sub>A</sub> = +25° C | 80  |     |     |       |  |

| CLR Pulse Width (MAX507)     | t <sub>8</sub> | TA = TMIN to TMAX       | 100 |     |     | ns    |  |

Note 2: V<sub>OUT</sub> must be less than (V<sub>DD</sub> - 2.5V).

Note 3: Dynamic performance is included for design guidance, not subject to test.

Note 4: The 0V to +5V or +10V ranges can be used with V<sub>SS</sub> = -5V with no degradation.

Note 5: CS = CSLSB and CSMSB for MAX508.

| <br> | <br>- /VI /I X I /I |

|------|---------------------|

# \_\_\_ Detailed Description Digital-to-Analog Converters

The MAX507/MAX508 are 12-bit, voltage-output DACs. The DAC output voltage has the same polarity as the reference, allowing single-supply operation.

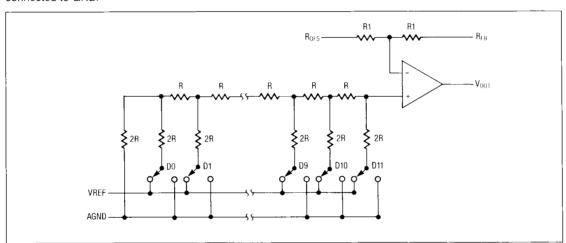

The basic DAC circuit consists of a laser-trimmed, thinfilm, R-2R resistor array with NMOS voltage switches (Figure 1).

### Output-Buffer Amplifier

The output amplifier is noninverting and configurable for a gain of 1 or 2. Three output voltage ranges can be configured for: 0V to +5V, 0V to +10V, and -5V to +5V. The output amplifier can drive  $2k\Omega$  in parallel with 100pF connected to GND.

The MAX507/MAX508 can operate from a single supply with a 0V to +5V or a 0V to +10V output range by tying VSS to 0V. However, the speed and current-sinking capability of the amplifier decreases as the output falls within 0.5V of VSS. Speed and current-sinking capability can be maintained by including a negative supply. Table 1 lists the allowable single and dual supplies for each range.

The output amplifier's small-signal bandwidth is typically 2MHz. Output noise is approximately 25nV/ $\sqrt{\rm Hz}$  at 1kHz, and output broadband noise is approximately 25 $\mu$ VRMs.

Figure 1. Simplified MAX507 DAC Circuit

Table 1. Output Voltage Range vs. Supply Voltage

|            | Single Supply      | Dual Supply        |                   |  |  |

|------------|--------------------|--------------------|-------------------|--|--|

| Range      | V <sub>DD</sub>    | V <sub>DD</sub>    | Vss               |  |  |

| 0V to +5V  | +11.4V to +15.75V  | +11.4V to +15.75V  | -4.5V to -15.75V  |  |  |

| 0V to +10V | +14.25V to +15.75V | +14.25V to +15.75V | -4.5V to -15.75V  |  |  |

| -5V to +5V |                    | +11.4V to +15.75V  | -11.4V to -15.75V |  |  |

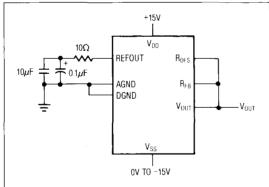

### Voltage Reference

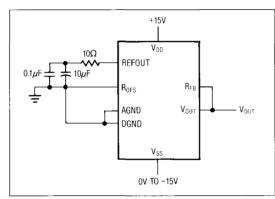

The voltage at REFOUT is 5V  $\pm$  10mV at +25°C. The reference is internally connected to the DAC and is buffered to accommodate the DAC's variable impedance. This buffer is capable of driving the DAC, the ROFS resistor, and up to  $500\mu A$  of external current. MAX507/ MAX508 specifications are determined with the internal reference. The reference should be decoupled at REFOUT with  $10\Omega$  in series with the recommended decoupling capacitors,  $10\mu F$  in parallel with  $0.1\mu F$ .

### Digital Inputs and Interface Logic

All logic inputs are compatible with both TTL and 5V CMOS logic. Supply current is specified for TTL input levels, but is reduced by about 450µA when the data inputs are driven near DGND or VDD. The control inputs (CLR, LDAC, WR, CS, CSMSB, and CSLSB) each draw 100µA from IDD when low.

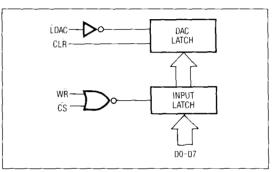

### MAX507 Interface

Table 2 is the MAX507 truth table. The MAX507 accepts a 12-bit input word that can be latched or transferred directly to the DAC. CS and WR control the input latch, and LDAC transfers information from the input latch to the DAC latch.

Table 2. MAX507 Truth Table

| CLR | LDAC | WR | CS  | Function                                            |

|-----|------|----|-----|-----------------------------------------------------|

| 1   | 0    | 0  | 0   | Both latches transparent                            |

| 1   | 1    | 1  | X   | Both latches latched                                |

| 1   | 1    | Х  | 1   | Both latches latched                                |

| 1   | 1    | 0  | 0   | Input latch transparent                             |

| 1   | 1    | 1  | 0   | Input latch latched                                 |

| 1   | 0    | 1  | 1   | DAC latch transparent                               |

| 1   | 1    | 1  | 1   | DAC latch latched                                   |

| 0   | X    | X  | Х   | DAC latch all 0s                                    |

| Ť   | 1    | 1  | 1   | DAC latch latched with 0s; output at 0V or -5V      |

| 1   | 0    | 0  | . 0 | Both latches transparent; output follows input data |

<sup>1 =</sup> High State X = Don't Care 0 = Low State † = Rising Edge

The input latch is transparent when  $\overline{CS}$  and  $\overline{WR}$  are low; the DAC latch is transparent when  $\overline{LDAC}$  is low. Data is latched within the input latch on the rising edge of  $\overline{WR}$  when  $\overline{CS}$  is low. The rising edge of  $\overline{LDAC}$  latches data into the  $\overline{DAC}$  when  $\overline{CS}$  and  $\overline{WR}$  are low. After  $\overline{CS}$  and  $\overline{WR}$  are high,  $\overline{LDAC}$  must be held low for to ronger (Figure 2).

Figure 2. MAX507 Timing Diagram

The DAC latch is reset to zeros with CLR low. CLR acts as a zero override when the input latch and DAC latch are transparent. Then, a low-to-high CLR transition loads all zeros into the DAC latch, and the output remains low (0V to -5V)

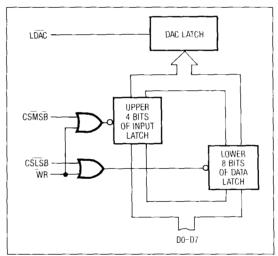

# MAX508 Interface

The MAX508's 8-bit-wide data bus interfaces with 8-bit  $\mu$ Ps. The MAX508 contains an input latch and a DAC latch. The data held in the DAC latch determines the output of the DAC. Table 3 is the MAX508 truth table, Figure 3 shows the input control logic, and Figure 4 shows the write-cycle timing.

# MAX507/MAX508

# Voltage-Output, 12-Bit DACs with Internal Reference

Table 3. MAX508 Truth Table

| CSLSB | СЅМЅВ | WR | LDAC | Function                                                         |

|-------|-------|----|------|------------------------------------------------------------------|

| 0     | 1     | 0  | 1    | Loads LSBs to input latches                                      |

| 0     | 1     | 1  | 1    | Locks LSBs in input latches                                      |

| 1     | 1     | 0  | 1    | Locks LSBs in input latches                                      |

| 1     | 0     | 0  | 1    | Loads MSBs to input latches                                      |

| 1     | 0     | 1  | 1    | Locks MSBs in input latches                                      |

| 1     | 1     | 0  | 1    | Locks MSBs in input latches                                      |

| 1     | 1     | 1  | 0    | Loads input into DAC latch                                       |

| 1     | 1     | 1  | 1    | Locks input into DAC latch                                       |

| 1     | 0     | 0  | 0    | Loads MSBs to input latches<br>and loads input into DAC<br>latch |

| 1     | 11    | 1  | 1    | No data transfer                                                 |

1 = High State 0 = Low State † = Rising Edge

Right-justified data is loaded into the MAX508 using CSMSB, CSLSB, and WR. Data can be latched into the input latch on the rising edge of WR for the most significant bit (MSB) and least significant bit (LSB), or on the rising edge of CSMSB for the MSB and CSLSB for the LSB. Either the MSB or the LSB can be loaded first

The complete, 12-bit word loads into the DAC register when LDAC is low, and latches on LDAC's rising edge. LDAC is asynchronous and independent of WR, so it is ideal for simultaneously updating multiple MAX508 outputs. Because LDAC can occur during a write cycle, it must stay low for t7 (or longer) after WR goes high to ensure correct data is latched to the output.

The MAX508 output can be updated in two write cycles by tying CSMSB and LDAC. In this automatic transfer mode, CSLSB and WR latch the lower 8 bits into the input latch; then CSMSB, WR, and LDAC load the upper 4 bits into the input latch and transfer the 12-bit word into the DAC latch. Alternatively, the MAX507 can be updated in two writes by tying CSLSB to LDAC if the upper 4 bits are input first, followed by the lower 8 bits.

Figure 3a. MAX507 Input Control Logic

Figure 3b. MAX508 Input Control Logic

# MAX507/MAX508

Figure 4. MAX508 Timing Diagram

# **Unipolar Configuration**

The MAX507/MAX508 are set up for a 0V to +5V unipolar output range by connecting ROFS, RFB, and VOUT (Figure 5). The converters operate from either a single or a dual supply in this configuration. See Table 4 for the DAC-latch contents (input) vs. analog output (output). In this range, 1LSB = VREF (2<sup>-12</sup>).

Figure 5. Unipolar Configuration (0V to +5V Output)

Table 4. Unipolar-Code Table (0V to +5V Output)

|      | •     |      | , , , , , ,                          |  |

|------|-------|------|--------------------------------------|--|

|      | INPUT |      | OUTPUT                               |  |

| 1111 | 1111  | 1111 | $(VREF) \frac{4095}{4096}$           |  |

| 1000 | 0000  | 0001 | (VREF) $\frac{2049}{4096}$           |  |

| 1000 | 0000  | 0000 | $(VREF) \frac{2048}{4096} = +VREF/2$ |  |

| 0111 | 1111  | 1111 | $(VREF) \frac{2047}{4096}$           |  |

| 0000 | 0000  | 0001 | (VREF) 1/4096                        |  |

| 0000 | 0000  | 0000 | ov                                   |  |

A 0V to +10V unipolar output range is set up by connecting ROFS to AGND and RFB to VOUT (Figure 6). See Table 5 for the DAC-latch contents (input) vs. analog output (output). The MAX507/MAX508 operate from either a single or a dual supply in this configuration. In this range, 1LSB = VREF  $(2^{-11})$ .

Figure 6. Unipolar Configuration (0V to +10V Output)

Table 5. Unipolar-Code Table (0V to +10V Output)

|      | •     |      | ,                                    |  |

|------|-------|------|--------------------------------------|--|

|      | INPUT |      | OUTPUT                               |  |

| 1111 | 1111  | 1111 | +2 (VREF) $\frac{4095}{4096}$        |  |

| 1000 | 0000  | 0001 | +2 (VREF) 2049<br>4096               |  |

| 1000 | 0000  | 0000 | +2 (VREF) $\frac{2048}{4096}$ =+VREF |  |

| 0111 | 1111  | 1111 | +2 (VREF) $\frac{2047}{4096}$        |  |

| 0000 | 0000  | 0001 | +2 (VREF) $\frac{1}{4096}$           |  |

| 0000 | 0000  | 0000 | 0V                                   |  |

Table 6. Bipolar-Code Table (-5V to +5V Output)

| to REFC<br>power s<br>content:<br>range, 1 | OUT and<br>upplies (<br>s (input<br>LSB = (2 | R <sub>FB</sub> to V<br>Table 1)<br>vs. an<br>V) VREF | Bipolar Configuration The is set up by connecting ROFS OUT, and operating from dual To See Table 6 for the DAC-latch Alog output (output). In this (2-11) = (VREF) 1/2048.  Table (-5V to +5V Output) | MAX507/MAX508 |

|--------------------------------------------|----------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                            | INPUT                                        |                                                       | OUTPUT                                                                                                                                                                                                | 2             |

| 1111                                       | 1111                                         | 1111                                                  | (+VREF) 2047<br>2048                                                                                                                                                                                  | NA.           |

| 1000                                       | 0000                                         | 0001                                                  | (+VREF) 1/2048                                                                                                                                                                                        | X5            |

| 1000                                       | 0000                                         | 0000                                                  | OV                                                                                                                                                                                                    | 0             |

| 0111                                       | 1111                                         | 1111                                                  | (-VREF) 1/2048                                                                                                                                                                                        | 00            |

| 0000                                       | 0000                                         | 0001                                                  | (-VREF) $\frac{2047}{2048}$                                                                                                                                                                           |               |

| 0000                                       | 0000                                         | 0000                                                  | (-VREF) $\frac{2048}{2048}$ = -VREF                                                                                                                                                                   |               |

## Pin Configurations (continued)

## \_\_\_Ordering Information (continued)

| PART       | TEMP. RANGE     | PIN-<br>PACKAGE       | ERROR<br>(LSBs) |

|------------|-----------------|-----------------------|-----------------|

| MAX508ACPP | 0°C to +70°C    | 20 Narrow Plastic DIP | ±1/2            |

| MAX508BCPP | 0°C to +70°C    | 20 Narrow Plastic DIP | ±3/4            |

| MAX508ACWP | 0°C to +70°C    | 20 Wide SO            | ±1/2            |

| MAX508BCWP | 0°C to +70°C    | 20 Wide SO            | ±3/4            |

| MAX508BC/D | 0°C to +70°C    | Dice*                 | ±3/4            |

| MAX508AEPP | -40°C to +85°C  | 20 Narrow Plastic DIP | ±1/2            |

| MAX508BEPP | -40°C to +85°C  | 20 Narrow Plastic DIP | +3/4            |

| MAX508AEWP | -40°C to +85°C  | 20 Wide SO            | ±1/2            |

| MAX508BEWP | -40°C to +85°C  | 20 Wide SO            | +3/4            |

| MAX508AMJP | -55°C to +125°C | 20 Narrow CERDIP**    | ±1/2            |

| MAX508BMJP | -55°C to +125°C | 20 Narrow CERDIP**    | ±3/4            |

Contact factory for dice specifications.

Contact factory for availability and processing to MIL-STD-883.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. Ne circuit patent bornses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1991 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Product: