#### **General Description**

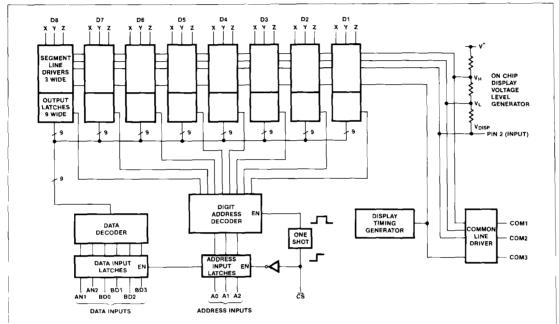

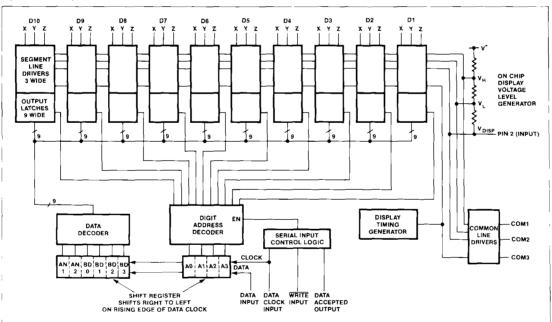

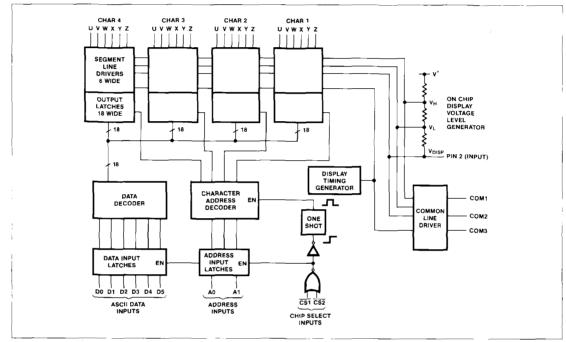

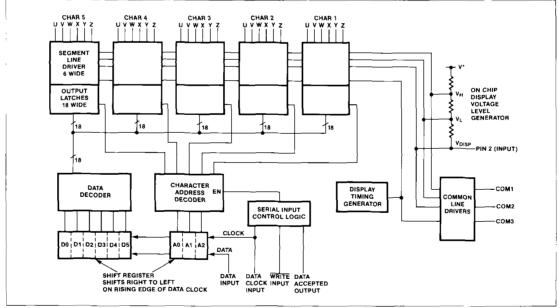

The MAX7231/32/33/34 family of integrated circuits is a complete line of triplexed liquid crystal display (LCD) drivers. These devices interface microprocessors (or digital systems) to multiplexed numeric and alphanumeric displays. The MAX7231 drives 8 digits and accepts data in a parallel format. The MAX7232 drives 10 digits and accepts data in a serial format. Both devices feature two independent annunciators per digit. The MAX7233 drives 4 alphanumeric 18 segment characters. The MAX7234 drives 5 alphanumeric 18 segment characters

Each device includes an input buffer, digit address decoding circuitry and mask-programmed ROM allowing six bits of input data to be decoded into 64 independent combinations of the output segments of each digit. This offloads the microprocessor system, reducing the ROM space and CPU time needed to service a display.

#### \_ Applications

These low-power LCD drivers are ideal for microprocessor-based portable applications where power consumption is a primary concern. Many applications also take advantage of the annunciator drive capability, which allows unlimited variations of display layout.

Portable instrumentation Industrial equipment Telecommunications Medical equipment Panel Meters Machine control

#### Features

- MAX7231 drives 8 digits/7 segments; parallel input format; 2 annunciators per digit

- MAX7232 drives 10 digits/7 segments; serial input format; 2 annunciators per digit

- MAX7233 drives 4 alphanumeric characters/ 18 segments; parallel input format

- MAX7234 drives 5 alphanumeric characters/ 18 segments; serial input format

- On-chip oscillator

- Direct interface to microprocessors

- Monolithic, Low Power CMOS Design

#### **Ordering Information**

| PART         | TEMP. RANGE    | PACKAGE             |

|--------------|----------------|---------------------|

| MAX7231AFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7231BFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7231CFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7232AFIPL | -20°C to ⋅85°C | 40 Lead Plastic DIP |

| MAX7232BFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7232CFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7233AFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7233BFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7234AFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

| MAX7234BFIPL | -20°C to +85°C | 40 Lead Plastic DIP |

Ordering information continued on next page

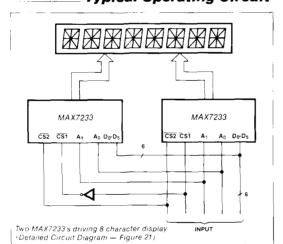

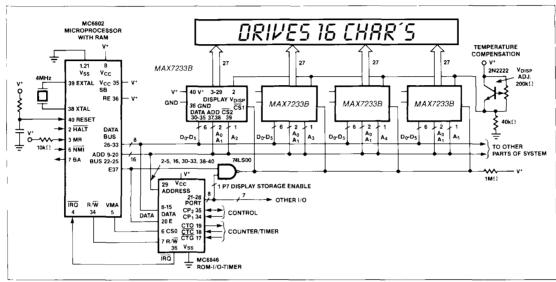

#### Typical Operating Circuit

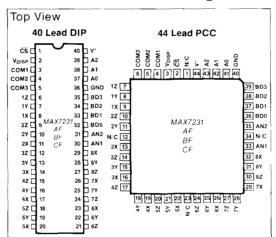

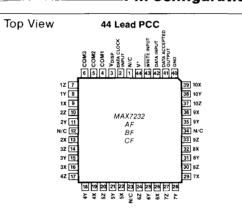

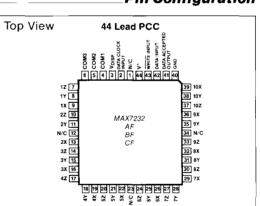

#### Pin Configuration

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

# MAX7231/32/33/34

# Triplexed LCD Decoder/Drivers

#### **OPTION TABLE**

| DEVICE    | OUTPUT CODE                                                | ANNUNCIATOR LOCATIONS                    | INPUT                                                 | OUTPUT                  |

|-----------|------------------------------------------------------------|------------------------------------------|-------------------------------------------------------|-------------------------|

| MAX7231AF | Hexdecimal                                                 | Both Annunicators                        | Parallel Entry                                        | 8 Digits                |

| MAX7231BF | Code B                                                     | on COM3                                  | 4 bit Data                                            | plus                    |

| MAX7231CF | Code B                                                     | 1 Annunciator COM1<br>1 Annunciator COM3 | 2 bit Annunciators<br>3 bit Address                   | 16 Annunciators         |

| MAX7232AF | Hexadecimal                                                | Both Annunciators                        | Serial Entry                                          | 10 Digits               |

| MAX7232BF | Code B                                                     | on COM3                                  | 4 bit Data<br>2 Bit Annunciators                      | plus<br>20 Annunciators |

| MAX7232CF | Code B                                                     | 1 Annunciator COM1<br>1 Annunciator COM3 | 4 bit Address                                         | 20 Amidiciators         |

| MAX7233AF | 64 Character (ASCII)<br>18 Segment<br>(Half width numbers) | No independent<br>Annunciators           | Parallel Entry 6 bit (ASCII)<br>Data<br>2 bit Address | Four<br>Characters      |

| MAX7233BF | 64 Character (ASCII)<br>18 Segment<br>(Full width numbers) | No Independent<br>Annunciators           | Parallel Entry 6 bit (ASCII)<br>Data<br>2 bit Address | Four<br>Characters      |

| MAX7234AF | 64 Character (ASCII)<br>18 Segment<br>(Half width numbers) | No Independent<br>Annunciators           | Serial Entry 6 bit (ASCII)<br>Data<br>3 bit Address   | Five<br>Characters      |

| MAX7234BF | 64 Character (ASCII)<br>18 Segment<br>(Full width numbers) | No Independent<br>Annunciators           | Serial Entry 6 bit (ASCII)<br>Data<br>3 bit Address   | Five<br>Characters      |

### Ordering Information (Continued from front page)

| PART        | TEMP. RANGE      | PACKAGE                      |

|-------------|------------------|------------------------------|

| MAX7231AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7231BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7231CFIQ | -20° C to +85° C | 44 Lead Plastic Chip Carrier |

| MAX7232AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7232BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7232CFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7233AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7233BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7234AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7234BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

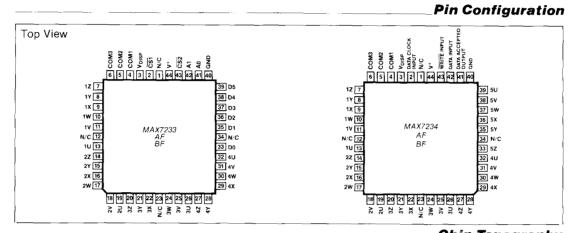

#### Pin Configuration

|                       |                    |                          |      | 2                     |                 |

|-----------------------|--------------------|--------------------------|------|-----------------------|-----------------|

|                       | ad DIP             | 40 Lead DIP              |      | 40 Lead D             | IP              |

| DATA CLOCK            | 40 b v.            | CS1 □ 7 40 □             | ) v+ | DATA CLOCK            | 10 D V-         |

| V <sub>DISP</sub> D 2 | 39 WRITE INPUT     | V <sub>DISP</sub>        | CS2  | V <sub>DISP</sub> □ 2 | 9 WRITE INPUT   |

| сом1 🗖 з              | 38 🗖 DATA INPUT    | COM-1 □ 3 38 □           | ) A1 |                       | BB DATA INPUT   |

| COM2 🗆 4              | 37 DATA ACCEPTED   | COM2 4 37                | A0   | COM2 ☐ 4 :            | 7 DATA ACCEPTED |

| COM3 ☐ 5              | 36 GND OUTPUT      | сомз 🗖 5 36 🗖            | GND  | сомз 🗖 5 :            | GND OUTPUT      |

| 1Z 🗆 6                | 35 🗖 10X           | 1Z 🗖 6 35 🗖              | D5   |                       | as 🗆 su         |

| 17 🗖 7                | 34 🗖 107           | 17 7 34                  | D4   | 17 🗖 7                | 14 □ 5V         |

| 1× 🗖 8,444            | X7232 33 10Z       | 1X   8 33   8 MAX7233 23 |      | 1X G 8<br>MAX7234     | 33 🗖 5W         |

|                       | Ar = ==            | ™ Ч° ΔF 32 F             |      | 1₩ 🗖 9 MAA / 234 :    | 32 🗖 5X         |

|                       | BF 31 ₽9Y          | 1V 🛶 10 BF 31 📙          |      | 1V □ 10 BF            | 31 🗅 5Y         |

|                       | CF 30 9Z           | 10 🛘 11 30 🖹             |      |                       | 30 🗖 5Z         |

| 3Z 🗖 12               | 29 BX              | 2Z 🗐 12 29 📴             |      |                       | 29 🗗 4∪         |

| 3Y 📙 13               | 28 B 8Y            | 2Y 🛚 13 28 🖺             |      | 7                     | 28 □ 4V         |

| 3X 🔲 14               | 27 BZ              |                          | ] 4W |                       | 27 🛭 4W         |

| 4Z 🔲 15               | 26 B 7X            | 2W 15 26                 |      |                       | 26 2 4X         |

| 4Y 🗒 16               | 25   7Y<br>24   7Z | 2V 16 25                 |      |                       | 25 P 4Y         |

| 4X   17<br>5Z   18    | 23 6x              | 20 17 24                 |      |                       | 24 P 42         |

| 52 L 18<br>57 L 19    | 22 6 67            | 3Z 18 23                 |      |                       | 23 🗎 3U         |

| 5X 🗆 20               | 21 62              | 3Y 19 22                 |      |                       | 22 D 3V         |

| 34 4 20               |                    | 3X 🗆 20 21               | ] 3W | 3X 🗀 20               | 21 3W           |

Continued on last page of data sheet.

\_/VI/XI/VI

#### **OPTION TABLE**

| DEVICE    | OUTPUT CODE                                                | ANNUNCIATOR LOCATIONS                                           | INPUT                                                 | OUTPUT                  |

|-----------|------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|-------------------------|

| MAX7231AF | Hexdecimal                                                 | Both Annunicators                                               | Parallel Entry                                        | 8 Digits                |

| MAX7231BF | Code B                                                     | on COM3                                                         | 4 bit Data                                            | plus                    |

| MAX7231CF | Code B                                                     | 1 Annunciator COM1<br>1 Annunciator COM3                        | 2 bit Annunciators<br>3 bit Address                   | 16 Annunciators         |

| MAX7232AF | Hexadecimal                                                | Both Annunciators                                               | Serial Entry                                          | 10 Digits               |

| MAX7232BF | Code B                                                     | on COM3                                                         | 4 bit Data<br>2 Bit Annunciators                      | plus<br>20 Annunciators |

| MAX7232CF | Code B                                                     | <ul><li>1 Annunciator COM1</li><li>1 Annunciator COM3</li></ul> | 4 bit Address                                         |                         |

| MAX7233AF | 64 Character (ASCII)<br>18 Segment<br>(Half width numbers) | No independent<br>Annunciators                                  | Parallel Entry 6 bit (ASCII) Data 2 bit Address       | Four<br>Characters      |

| MAX7233BF | 64 Character (ASCII)<br>18 Segment<br>(Full width numbers) | No Independent<br>Annunciators                                  | Parallel Entry 6 bit (ASCII)<br>Data<br>2 bit Address | Four<br>Characters      |

| MAX7234AF | 64 Character (ASCII)<br>18 Segment<br>(Half width numbers) | No Independent<br>Annunciators                                  | Serial Entry 6 bit (ASCII)<br>Data<br>3 bit Address   | Five<br>Characters      |

| MAX7234BF | 64 Character (ASCII) 18 Segment (Full width numbers)       | No Independent<br>Annunciators                                  | Serial Entry 6 bit (ASCII) Data 3 bit Address         | Five<br>Characters      |

## Ordering Information (Continued from front page)

| PART        | TEMP. RANGE      | PACKAGE                      |

|-------------|------------------|------------------------------|

| MAX7231AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7231BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7231CFIQ | -20° C to +85° C | 44 Lead Plastic Chip Carrier |

| MAX7232AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7232BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7232CFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7233AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7233BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7234AFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

| MAX7234BFIQ | -20°C to +85°C   | 44 Lead Plastic Chip Carrier |

#### Pin Configuration

| 40 Lead DIP          | 40                 | Lead DIF       | •       | 40 Lead [              | OIP               |

|----------------------|--------------------|----------------|---------|------------------------|-------------------|

| DATA CLOCK 1 40      | ı v¹               | 1 40           | DATA CI | OCK 1                  | 40 h v+           |

| V <sub>DISP</sub>    | WRITE INPUT VDISP  | 2 39           |         | V <sub>DISP</sub> [] 2 | 39 WRITE INPUT    |

| COM1 ☐ 3 38 ☐        | DATA INPUT COM1    | 3 38           |         | COM1 3                 | 38 DATA INPUT     |

| COM2 🗍 4 37          | DATA ACCEPTED COM2 | 4 37           | ] A0 (  | OM2 🗖 4                | 37 DATA ACCEPTED  |

| COM3 ☐ 5 36          | GOM3               | 5 36           | ] GND   | ОМЗ □ 5                | 36 GND OUTPUT     |

| 1Z 🗖 6 35            |                    | 6 35           | ] D5    | 1Z 🗖 6                 | 35 □ 5∪           |

| 17 7 34              | ] 10Y 1Y 🗆         |                | □ D4    | 1Y 🖂 7                 | 34 D 5V           |

| 1X [ 8<br>MAX7232 33 | ] 10Z 1X 🗖         | 8 444 77222 33 | ] D3    | 1X B MAX7234           | , 33 🗖 5 <b>W</b> |

| AF                   | · · · · ·          |                |         | 1₩ 🗖 9 📈 AF            | 32 🗖 5X           |

| 2Y 🛮 10 BF 31        |                    | 10 BF 31       |         | 1V 🗆 10 BF             | 31 57             |

| 2X 🖸 11 CF 30        |                    |                | ] 00    | 10 🗆 11                | 30 D 5Z           |

|                      | ] 8X 2Z 🗍          |                |         | 2Z 🔲 12                | 29 40             |

| 3Y 🛚 13 28           |                    |                |         | 2Y 🗆 13                | 28 AV             |

|                      |                    |                | ] 4W    | 2X 🖫 14                | 27 4W             |

| 4Z 🛘 15 26           |                    | 15 26          |         | 2W 🗆 15                | 26 🗆 4X           |

| 4Y 16 25             |                    | 16 25          |         | 2V 🗖 16                | 25 4Y             |

| 4X 17 24             |                    |                |         | 2U 🛭 17                | 24 🖸 4Z           |

| 5Z 18 23             |                    |                | ] 3U    | 3Z 🗐 18                | 23 🖸 3U           |

| 5Y 19 22             |                    |                | ⊒ 3V    | 3Y 🖳 19                | 22 D 3V           |

| 5X 🗖 20 21           | ] 6Z 3x 🗖          | 20 21          | ] 3₩    | 3X 🔲 20                | 21 🗖 3W           |

TERMINAL DEFINITIONS

MAX7231 PARALLEL INPUT NUMERIC DISPLAY

| TERMINAL                 | PIN NO.              | DESCI                                | DESCRIPTION                                          |                                   | FUNCTION                                                            |

|--------------------------|----------------------|--------------------------------------|------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|

| AN1<br>AN2               | 30<br>31             |                                      | nnunciator 1 Control Bit<br>nnunciator 2 Control Bit |                                   | See Table 1                                                         |

| BD0<br>BD1<br>BD2<br>BD3 | 32<br>33<br>34<br>35 | Least Significant  Most Significant  | 4 Bit Binary<br>Data Inputs                          | Input<br>Data<br>(See Table 2)    | HIGH – Logical One (1)                                              |

| A0<br>A1<br>A2           | 37<br>38<br>39       | Least Significant ) Most Significant | 3 Bit Digit<br>Address Inputs                        | Input<br>Address<br>(See Table 4) | LOW = Logical Zero (0)                                              |

| ĈŜ                       | 1                    | Data Input Strobe/<br>(Note 3)       | Chip Select                                          |                                   | e going) edge latches data,<br>ut to be decoded and sent<br>d digit |

Note 3: CS has a special "mid-level" sense circuit that establishes a test mode if it is held near 3V for several msec. Inadvertent triggering of this mode can be avoided by pulling it high when inactive, and driving it with fast rise and fall times.

MAX7233 PARALLEL INPUT ALPHA DISPLAY

| TERMINAL                         | PIN NO.                          | DESCRI                                | DESCRIPTION                  |                                | FUNCTION                                                                                          |

|----------------------------------|----------------------------------|---------------------------------------|------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------|

| D0<br>D1<br>D2<br>D3<br>D4<br>D5 | 30<br>31<br>32<br>33<br>34<br>35 | Least Significant                     | 6 Bit (ASCII)<br>Data Inputs | Input<br>Data<br>(See Table 3) | HIGH = Logical One (1)<br>LOW = Logical Zero (0)                                                  |

| A0<br>A1                         | 37<br>3                          | Least Significant<br>Most Significant | Address Inputs               | Input Add.<br>(See Table 5)    |                                                                                                   |

| CS1<br>CS2                       | 39<br>1                          | Chip Select Inputs<br>(Note 3)        |                              | Rising edge of e               | N, load data into input latches.<br>sither input causes data to be<br>d and sent out to addressed |

| TERMINAL                   | PIN NO. | DESCRIPTION                                    | FUNCTION                                                                                                                                                                                                                                                                     |

|----------------------------|---------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Input                 | 38      | Data + Address Shift Register Input            | HIGH - Logical One (1)<br>LOW - Logical Zero (0)                                                                                                                                                                                                                             |

| WRITE Input                | 39      | Decode, Output, and Reset Strobe               | When DATA ACCEPTED Output is LOW, positive going edge of WRITE causes data in shift register to be decoded and sent to addressed digit, then shift register and control logic is reset. When DATA ACCEPTED Output is HIGH, positive going edge of WRITE triggers reset only. |

| Data Clock<br>Input        | 1       | Data Shift Register and Control<br>Logic Clock | Positive going edge advances data in shift register. MAX7232: Eleventh edge resets shift register and control logic. MAX7234: Tenth edge resets shift register and control logic.                                                                                            |

| DATA<br>ACCEPTED<br>Output | 37      | Handshake Output                               | Output LOW when correct number of bits entered into shift register; MAX7232: 8, 9 or 10 bits. MAX7234: 9 bits.                                                                                                                                                               |

| TERMINAL                             | PIN NO.      | DESCRIPTION                                                                                                       | FUNCTION                                                                                                                 |

|--------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Display<br>Voltage V <sub>DISP</sub> | 2            | Negative end of on-chip resistor string used to generate intermediate voltage levels for display. Shutdown Input. | Display voltage control. When open (or less than 1V from V+) chip is shutdown; oscillator stops, all display pins to V+. |

| Common Line<br>Driver Outputs        | 3,4,5        |                                                                                                                   | Drive display commons, or rows.                                                                                          |

| Segment Line<br>Driver Outputs       | 6-29<br>6-35 | (On MAX7231/33)<br>(On MAX7232/34)                                                                                | Drive display segments, or columns.                                                                                      |

| V+                                   | 40           | Positive Supply                                                                                                   |                                                                                                                          |

| GND                                  | 36           | Ground                                                                                                            |                                                                                                                          |

Figure 1. Block Diagram of MAX7231.

Figure 2. Block Diagram of MAX7232

Figure 3. Block Diagram of MAX7233

Figure 4. Block Diagram of MAX7234

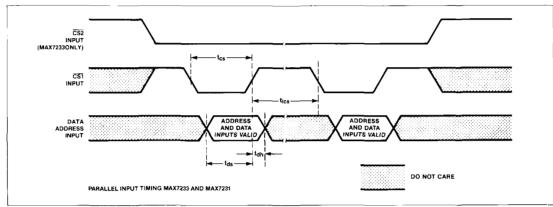

Figure 5. Parallel Input Timing

#### **Detailed Description**

Parallel Input Interface

The MAX7231 and MAX7233 have a parallel interface

allowing direct parallel connection to microprocessors. The address and data bits are latched on the positive going edge of the Chip Select. The positive going edge of Chip Select also triggers an internal monostable that enables the address decoder and latches the decoded data into the digit/character output latches.

Figure 5 shows the timing requirements for the parallel input devices (7231 and 7233). To ensure that the new data does not appear at the decoder inputs before the previous decoded data is written to the outputs, there is a minimum time required between CHIP SELECT pulses.

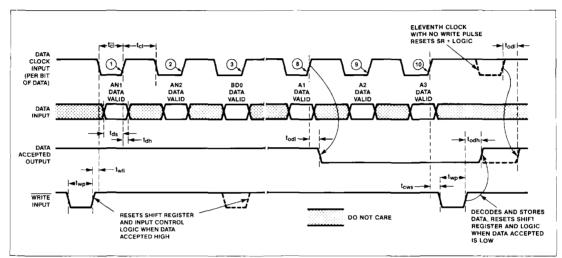

#### Serial Input Interface

A WRITE pulse while Data Accepted Output is high will reset the serial input control logic, but will not latch any data. A WRITE pulse while Data Accepted Output is low will cause the MAX7232 and MAX7234 to decode the data, latch the data into the output latches and then reset the serial input control logic.

This assures that each data bit will be entered into the correct position in the shift register, depending on the subsequent data clock inputs. The MAX7232's Data Accepted Output goes low after 8 Data Clock pulses, whereas the MAX7234's Data Accepted Output goes low after 9 Data Clock Inpulses. Further Data Clock pulses occuring before a WRITE pulse will cause the Data Accepted Output to go high after 11 Data Clock pulses in the MAX7232 and the 10 Data Clock pulses in the MAX7234. In both cases, the serial input control logic is also reset when Data Accepted goes high.

The serial input timing diagram shown in Figure 6 illustrates the recommended procedure for entering data.

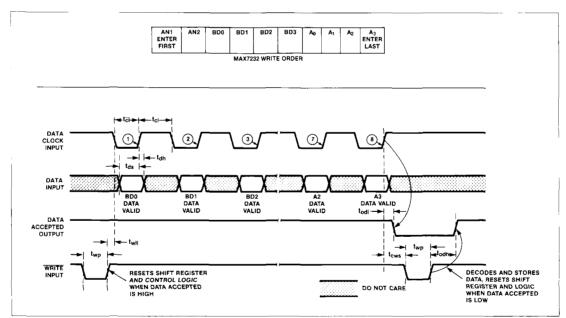

Note that the eleventh clock resets the shift register and control logic for the MAX7232, but the Data Accepted Output goes low after the eighth clock. As Figure 7 illustrates, this allows the user to reduce the data to eight bits. The MAX7232 then writes to the 7 segment display, but leaves the annunciators off. Nine Bits are clocked in if only AN2 is turned on.

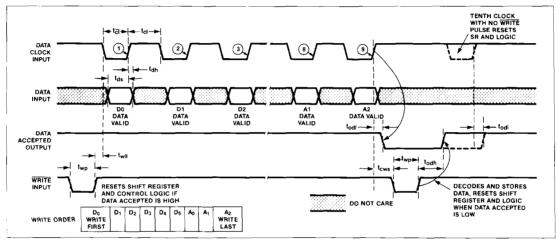

The control logic of the MAX7234 is similar to the MAX7232, but nine bits are always required. As illustrated in Figure 8, the data bits are only latched if the WRITE input occurs after the ninth data bit has been entered and Data Accepted Output is low.

Figure 6. One Digit Timing Diagram for the MAX7232, Writing Both Annunciators.

Figure 7. Input Timing Diagram of the MAX7232. Both Annunciators OFF.

Figure 8. One Character Input Timing Diagram of the MAX7234.

## Temperature Compensation Temperature Effects

Temperature affects the performance of liquid crystal displays (LCD's) in two ways. As the display temperature drops, the response time of the display becomes longer. At very low temperatures, some displays may take several seconds to change to a new character. However, high-speed liquid crystal materials are available for low temperature environments.

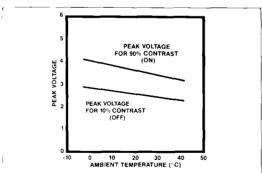

Temperature has a significant effect on the variation of liquid crystal threshold voltage. The peak voltage (Vp) required to turn on the display has a temperature coefficient of –7 to –14 mV/°C for typical liquid crystal materials used in multiplexed LCD's. This means that as the temperature increases, the threshold voltage

Figure 9. Temperature Dependence of Liquid Crystal Threshold.

decreases. Figure 9 illustrates the dependence of peak voltage (VP) on temperature for the same liquid crystal material described in Figure 10. Assuming a fixed value for VP, OFF segments begin to be visible when the threshold voltage drops below VP/3. To avoid this problem at high temperature, VP may be set at a fixed voltage chosen to make the RMS OFF voltage, VP/3, just below the threshold voltage at the highest temperature expected. This is appropriate where display temperatures do not vary widely.

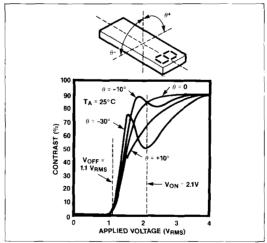

Figure 10. Applied RMS Voltage vs. Contrast.

#### Display Voltage

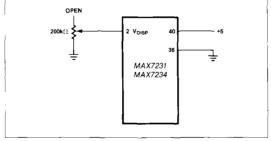

An internal resistor string of three equal value resistors is used to generate the display drive voltages. One end of the string is available at Pin 2 (VDISP) and the other end is connected to V+ on the chip. Pin 2, the user's input, allows the display voltage to be optimized for a particular liquid crystal material. Note that Vp should be three times the threshold voltage for the liquid crystal material used (Vp = V+ - VDISP). To avoid device latchup and possible destruction of the chip, never drive Pin 2 below Ground or above V+.

Figure 11 illustrates a simple method of generating a display voltage suitable for a particular display. A potentiometer with a maximum value of  $200 \rm k\,\Omega$  connected from Pin 2 to Ground gives sufficient range adjustment to suit most displays. Due to the positive temperature coefficient of the resistors on-chip, this method for generating display voltage should be used only in applications where the temperature variation of the chip and display will not vary more than  $\pm 5\,^{\circ}\mathrm{C}$  (15°F). The power supply voltage also effects the display voltage.

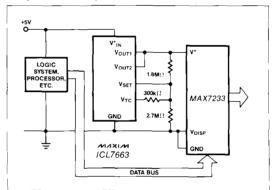

The chip may be operated at the display voltage with VDISP connected to Ground in battery powered applications where the display voltage is the same as the battery voltage (typically 3 to 4.5 volts). The inputs of the chip are designed such that they may be driven above V+ without damage. This allows the chip and display to operate at a regulated 3V while its inputs are driven by a microprocessor that is operating at a less well controlled 5V supply. Under no circumstances should the inputs be driven more than 6.5V above Ground. Independent adjustment of both voltage and temperature compensation is illustrated in Figure 12. Temperature compensation is performed by the ICL7663.

Another method of setting up a display voltage is illustrated in Figure 13. The five diodes (1N914 or equivalent), each have a forward drop of approximately 0.65V, with 20  $(\mu A)$  at room temperature. This configuration is suitable for the 3V display using the material properties as shown in Figures 9 and 10. More diodes may be added for higher voltage displays. Each diode has a negative temperature

Figure 11. Simple Display Voltage Adjustment.

coefficient of -2mV/°C (5 in series gives -10mV/°C). Consequently, this circuit will provide reasonable temperature compensation.

Figure 12. Flexible Temperature Compensation.

Figure 13. Diode String VDISP Generator.

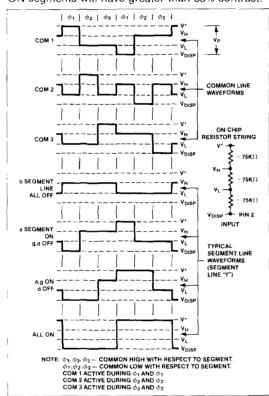

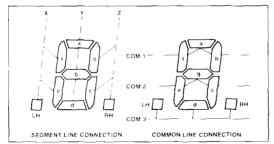

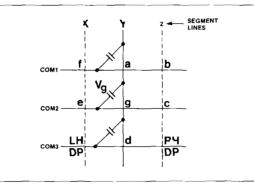

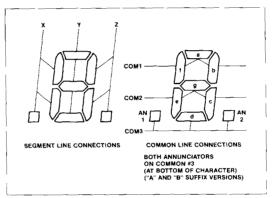

#### Triplexing

The connection diagram for a typical 7-segment display font with 2 annunciators is illustrated in Figure 15. The MAX7231 and MAX7232 (A and B suffix versions) numeric display drivers use this configuration. The voltage waveforms of the common lines and one segment line are illustrated in Figure 14. The "Y" segment line has been chosen as an example. This line intersects with COM1 to form the "A" segment, COM2 to form the "G" segment, and COM3 to form the "D" segment. Four different ON/OFF combinations of the "A", "G" and "D" segments and their corresponding waveforms of the "Y" segment line are illustrated in Figure 14. The schematic diagram in Figure 16 shows that each intersection acts as a capacitance from segment line to common line. Figure 17 illustrates the voltage across the "G" segment for the same four combinations of ON/OFF segments shown in Figure 14.

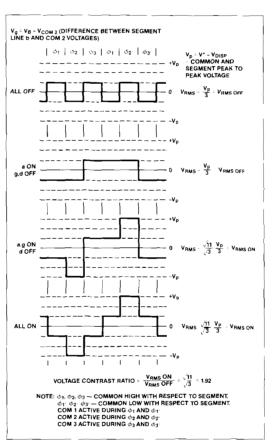

The RMS voltage across the segment determines the degree of polarization for the liquid crystal material and thus the contrast of the segment. The

RMS OFF voltage is always Vp/3, whereas the RMS ON voltage is always 1.92 Vp/3. This is illustrated in Figure 17. The ratio of RMS ON to OFF voltage is fixed at 1.92 for a triplexed liquid crystal display.

Contrast vs. applied RMS voltage is shown in Figure 10. With a Vp of 3.1V, the RMS ON voltage is 2.1V and the RMS OFF voltage is 1.1V. The OFF segment will have a contrast of less than 5%, while the ON segments will have greater than 85% contrast.

Figure 14. Display Voltage Waveforms.

Figure 15. Connection Diagrams for Typical 7-Segment Displays.

Figure 16. Schematic of Display.

Figure 17, Voltage Waveforms on Segment g (Vg).

#### **Output Codes and Display Fonts**

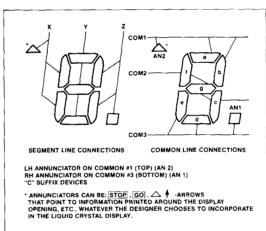

The MAX7231 and MAX7232 numeric display drivers are programmed to drive 7-segment displays plus 2 annunciators per digit. Refer to Table 1 for annunciator input controls. The display connections for one digit are shown in Figure 18. Both annunciators are placed on COM3 on the "A" and "B" suffix devices. The "A" devices offer a "hexadecimal" 7-segment output, while the "B" devices offer "Code B" outputs. This is illustrated in Table 2. Figure 19 illustrates the "C" device configuration. The Left

Table 1: Annunciator Decoding

| CODE<br>INPUT |         | DISPLAY OUTPUT                                                 |                                                                                  |  |

|---------------|---------|----------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| AN<br>2       | AN<br>1 | MAX7231 A/B<br>MAX7232 A/B<br>BOTH<br>ANNUNCIATORS<br>ON COM 3 | MAX7231C<br>MAX7232C<br>LH<br>ANNUNCIATOR<br>COM 1<br>RH<br>ANNUNCIATOR<br>COM 3 |  |

| 0             | 0       | 8                                                              | 8                                                                                |  |

| 0             | 1       | .8                                                             | 8.                                                                               |  |

| 1             | 0       | 8.                                                             | 8                                                                                |  |

| 1             | 1       | 8                                                              | 8.                                                                               |  |

Table 2: Binary Data Decoding (MAX7231/MAX7232)

|         | (1017/1201/1017/1202) |         |         |        |                   |  |  |

|---------|-----------------------|---------|---------|--------|-------------------|--|--|

|         | CODE<br>INPUT         |         |         |        | DISPLAY<br>OUTPUT |  |  |

| BD<br>3 | BD<br>2               | BD<br>1 | BD<br>0 | HEX    | CODE<br>B         |  |  |

| 0       | 0                     | 0       | 0       | 0      | 0                 |  |  |

| 0       | 0                     | 0       | 1       | 7      | 7                 |  |  |

| 0       | 0                     | 1       | 0       | 2      | 2                 |  |  |

| 0       | 0                     | 1       | 1       | 2      | <u>2</u><br>3     |  |  |

| 0       | 1                     | 0       | 0       | 4      | Ч                 |  |  |

| 0       | 1                     | 0       | 1       | S<br>8 | 5                 |  |  |

| 0       | 1                     | 1       | 0       | 5      | 8                 |  |  |

| 0       | 1                     | 1       | 1       | 7      | 7                 |  |  |

| 1       | 0                     | 0       | 0       | 8      | 8                 |  |  |

| 1       | 0                     | 0       | 1       | 9      | 3                 |  |  |

| 1       | 0                     | 1       | 0       | R      | _                 |  |  |

| 1       | 0                     | 1       | 1       | Ь      | Ε                 |  |  |

| 1       | 1                     | 0       | 0       | Ε      | Н                 |  |  |

| 1       | 1                     | 0       | 1       | d      | L                 |  |  |

| 1       | 1                     | 1       | 0       | E      | Р                 |  |  |

| 1       | 1                     | 1       | 1       | F      | BLANK             |  |  |

hand annunciator is placed on COM1 (AN2) and the right hand annunciator (usually a decimal point) is placed on COM3 (AN1). Only a "Code B" output is offered for the "C" devices.

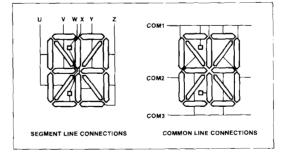

Both the MAX7233 and MAX7234 are supplied in "A" and "B" versions, decoding an ASCII 6-bit subset to an 18-segment display, with 16 "flag" segments and 2 "dots". Figure 20 illustrates the layout for a single character. The "A" devices have numbers which are half-width and the "B" devices have full-width numbers. Refer to Table 3 for output decoding.

Table 3: Data Decoding — 18 Segment

|            |    |    |       | DISPLAY OUTPUT |                |          |              |            |

|------------|----|----|-------|----------------|----------------|----------|--------------|------------|

| CODE INPUT |    |    | D5 D4 |                |                | VERSION  | B<br>VERSION |            |

| D3         | D2 | D1 | D0    | 0,0 0,1 1,0 1, |                | ,1       |              |            |

| 0          | 0  | 0  | 0     | C              | P              |          |              | CJ .       |

| 0          | 0  | 0  | 1     | A              | Ū              |          | T            | 7          |

| 0          | 0  | 1  | 0     | B              | R              | - 11     | -5           | 23 4       |

| 0          | 0  | 1  | 1     |                | 5              | Ŧ        | Ē            | 3          |

| 0          | 1  | 0  | 0     | Ī              | T              | <u> </u> | 4            | <u></u>    |

| 0          | 1  | 0  | 1     | E              | Ш              | %        | 5            | 55<br>65   |

| 0          | 1  | 1  | 0     | F              | $\overline{V}$ | L        | T 6          | <i>E</i> 5 |

| 0          | 1  | 1  | 1     | G              | W              | ī        | 7            | 7          |

| 1          | 0  | 0  | 0     | Н              | X              | <        | 8            | <i>E3</i>  |

| 1          | 0  | 0  | 1     | I              | Υ              | >        | 9            | 53         |

| 1          | 0  | 1  | 0     | J              | Z              | *        |              | :          |

| 1          | 0  | 1  | 1     | K              | Ī              | +        |              | ;          |

| 1          | 1  | 0  | 0     | L              | 1              | /        |              | ۷          |

| 1          | 1  | 0  | 1     | M              | ]              | _        |              | =          |

| 1          | 1  | 1  | 0     | N              | 7              |          |              | 7          |

| 1          | 1  | 1  | 1     |                | +              | /        | -            | 7          |

Table 4: Address Decoding (MAX7231/7232)

|                     | CODE | DISPLAY<br>OUTPUT |    |                   |

|---------------------|------|-------------------|----|-------------------|

| MAX<br>7232<br>ONLY | A2   | <b>A</b> 1        | ΑO | DIGIT<br>SELECTED |

| 0                   | 0    | 0                 | 0  | D1                |

| 0                   | 0    | 0                 | 1  | D2                |

| 0                   | 0    | 1                 | 0  | D3                |

| 0                   | 0    | 1                 | 1  | D4                |

| 0                   | 1    | 0                 | 0  | D5                |

| 0                   | 1    | 0                 | 1  | D6                |

| 0                   | . 1  | 1                 | 0  | D7                |

| 0                   | 1    | 1                 | 1  | D8                |

| 1                   | 0    | 0                 | 0  | D9                |

| 1                   | 0    | 0                 | 1  | D10               |

| 1                   | 0    | 1                 | 0  | NONE              |

| 1                   | 0    | 1                 | 1  | NONE              |

| 1                   | 1    | 0                 | 0  | NONE              |

| 1                   | 1    | 0                 | 1  | NONE              |

| 1                   | 1    | 1                 | 0  | NONE              |

| 4                   | 1    | 1                 | 1  | NONE              |

Table 5: Address Decoding (MAX7233/7234)

|                     | CODE | DIGIT<br>SELECTED |      |

|---------------------|------|-------------------|------|

| MAX<br>7234<br>ONLY |      |                   |      |

| A2                  | A1   | Α0                |      |

| 0                   | 0    | 0                 | D1   |

| 0                   | 0    | 1                 | D2   |

| 0                   | 1    | 0                 | D3   |

| 0                   | 1    | 1                 | D4   |

| 1                   | 0    | 0                 | D5   |

| 1                   | 0    | 1                 | NONE |

| 1                   | 1    | 0                 | NONE |

| 1                   | 1    | 1                 | NONE |

Figure 18. Display Fonts for MAX7231 and 7232. (Suffix Versions "A" and "B").

Figure 19. Display Fonts for MAX7231 and 7232. (Suffix Version "C").

Figure 20. Display Fonts for MAX7233 and 7234. (18-Segment Alphanumeric).

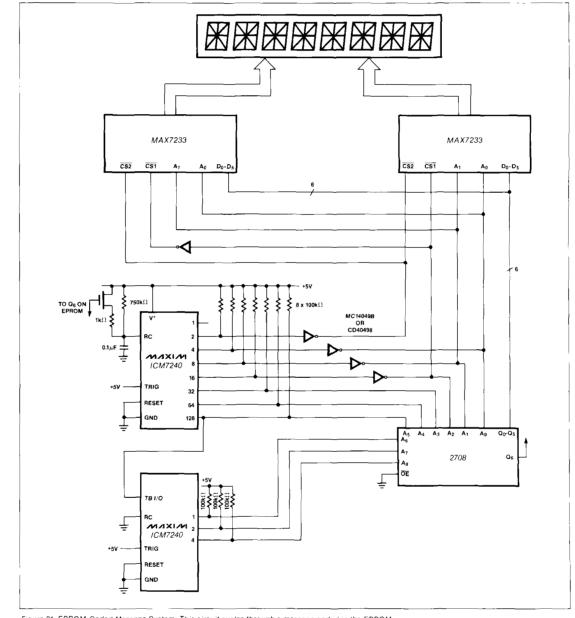

Figure 21. EPROM-Coded Message System. This circuit cycles through a message coded in the EPROM, pausing at the end of each line, or whenever coded on  ${\rm Q}_6$ .

14 \_\_\_\_\_\_/VI/XI/VI

Figure 22. MC6802 Microprocessor with 16 Character 16 Segment ASCII Liquid Crystal Display.

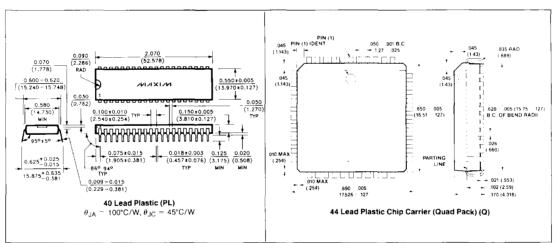

#### Package Information

Chip Topography MAX7231 MAX7232 A1 V V CS CS Vinise COM1 MAX7233

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1995 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Products.