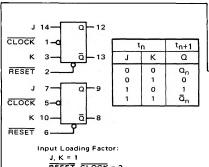

# MC3100/MC3000 series

**DUAL J-K FLIP-FLOP**

# MC3163F · MC3063F MC3163L · MC3063L,P (54H73) (74H73)

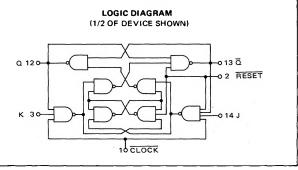

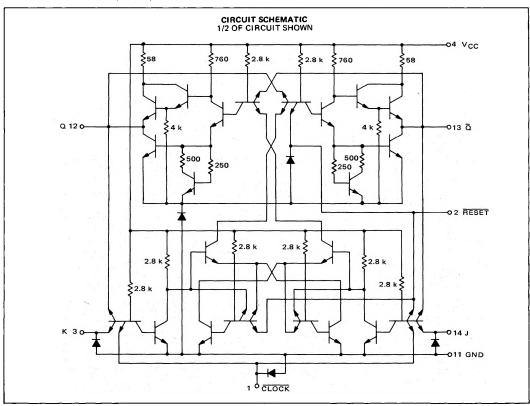

The MC3163/3063 dual J-K master-slave flip-flop is useful in simple register and counter designs, or where relatively slow rise times may be encountered. A similar function, the MC3155/3055 (MC54H72/74H72) AND input J-K flip-flop is available for applications requiring multiple ANDed inputs.

RESET, CLOCK = 2

Output Loading Factor = 10

Total Power Dissipation = 176 mW typ/pkg Propagation Delay Time = 10 ns typ Operating Frequency = 30 MHz typ

Pin numbers for the 54H73F/74H73F device are the same as the pin numbers for the MC3163F,L/3063F,L,P. These devices are available on special request.

See General Information section for packaging.

# **ELECTRICAL CHARACTERISTICS**

Test procedures are shown for only one flip-flop. The other flip-flop is tested in the same manner.

|                                                            |                 |               | c 12   | 1000                                |                  | 6    |                                  |              |       |       | TEST C    | URRENT | /VOLT    | GE VAL                            | UES (Al | TEST CURRENT/VOLTAGE VALUES (All Temperatures)     | atures) |        |                  |               |                                                 |   |

|------------------------------------------------------------|-----------------|---------------|--------|-------------------------------------|------------------|------|----------------------------------|--------------|-------|-------|-----------|--------|----------|-----------------------------------|---------|----------------------------------------------------|---------|--------|------------------|---------------|-------------------------------------------------|---|

|                                                            |                 |               | )      |                                     | 10               | 80   |                                  |              | μM    | 4     |           |        |          |                                   | Volts   |                                                    |         |        |                  | _             |                                                 | _ |

|                                                            |                 |               | 100    | RESET                               | ٩                |      |                                  |              | 101   | -о    | V         | ><br>E | VIHH     | >«                                | V, th.1 | Vtho                                               | ν ςς    | Vca    | V <sub>ссн</sub> |               |                                                 |   |

|                                                            |                 |               |        |                                     |                  |      | Z                                | MC3163       | 20    | -0.5  | 0.4       | 2.4    | 5.5      | 4.5                               | 2.0     | 8.0                                                | 5.0     | 4.5    | 5.5              |               |                                                 | _ |

|                                                            | . 1             |               | ÷      |                                     | 1                | ľ    | ×                                | MC3063       | 20    | -0.5  | 0.4       | 2.4    | 5.5      | 4.5                               | 2.0     | 8.0                                                | 5.0     | 4, 75  | 5, 25            |               |                                                 | _ |

|                                                            |                 | Pin<br>Under  | MC31   | 1C3163 Test Limits<br>-55 to +125°C | t Limits<br>25°C | MC3  | MC3063 Test Limits<br>0 to +75°C | Limits       |       | TE    | T CURE    | ENT/V( | JLTAGE   | APPLIE                            | T0 PI   | TEST CURRENT/VOLTAGE APPLIED TO PINS LISTED BELOW: | D BELO  |        |                  |               |                                                 |   |

| Characteristic                                             | Symbol          | Test          | Min    | Max                                 | Unit             | Min  | Max                              | Unit         | _6    | _ь    | ٧,        | >      | VIHH V   | >~                                | V#1     | V#0                                                | νς.     | Vccı   | VCCH             | *             | Gnd                                             | _ |

| Input Forward Current K K Reset Clock                      | I.F.            | 14<br>1       | 1111   | 2.2.0                               | mAdc             | 1511 | 2.0                              | mAdc         | 13.11 | 1111  | 1 2 3 3 4 | DEFE   |          | 1,2,3<br>1,2,14<br>1,14<br>2,3,14 | 1117    |                                                    |         | 2393   | 4                | 12<br>13<br>2 | 11*<br>**-                                      |   |

| Leakage Current J<br>Reset<br>Clock                        | IR1             | 14<br>2<br>1† |        | 50<br>50<br>100<br>50               | μAdc ←           |      | 50<br>50<br>100<br>50            | μAdc +       | 1111  | 1111  | 101       | 1234   | 1111     | 1 64 1 1                          | 1111    | . 111                                              |         | 1.13.1 | 4                | 16411         | 1,2,11*<br>1,11*<br>1,3,11,13,14*<br>2,3,11,14* |   |

| J<br>Reset<br>Clock                                        | <sup>1</sup> R2 | 14<br>2<br>1  | 1.11.1 | 1.0                                 | mAdc             |      | 1.0                              | mAdc         | 1101  | ritio | 1111      | 1111   | 14 3 2 1 | 1011                              | 1.131   |                                                    | 1111    | ri-i i | 4                | 10111         | 1,2,11*<br>1,11*<br>1,3,11*,13,14<br>2,3,11,14* |   |

| Output<br>Output Voltage                                   | NOT.            | 12            | 1.1    | 4.0                                 | Vdc              | 1.1  | 0.4                              | Vdc          | 12    | 64    | 7.1       | 1, 1   | 1.4      | 1,3,14                            | 1 23    | 63 1                                               | 7.1     | 44     | 0.4              | 13            | 1,3,11,14*                                      |   |

|                                                            | МОН             | 12<br>13      | 2.4    | 1.1                                 | Vdc              | 2.4  | 100                              | Vdc          | 1.1   | 12    | 1.1       | 1 1    | 1.1      | 1,3                               | 2 -     | 1 2                                                | 1.1     | 4      | 1.1.             | 13            | 11,14*                                          |   |

| Short-Circuit Current                                      | $^{1}_{\rm sc}$ | 121           | -40    | -100                                | mAdc<br>mAdc     | -40  | -100                             | mAdc<br>mAdc | 1.1   | 1.1   | 1.1       | + +    | i, i     | 1,3,14                            | 4.1     | 4 4                                                | 1.1     | 1.1    | 4                | 4.3           | 11,12,13* 2,11,13*                              |   |

| Power Requirements<br>(Total Device)<br>Power Supply Drain | IPD             | 4             | 1      | 90                                  | mAdc             | i.   | 20                               | mAde         |       | ď     | 7         | 3      | 1        | 1,2,5#                            | ī       | 1                                                  | i       | 2      | 4                | i             | 3,10,11                                         |   |

\*Ground inputs to flip-flop not under test.

\*\*Momentarily ground pin prior to taking measurement to set flip-flop in the desired state. (If pin is also in another column, the pin must be returned to that voltage or current for measurement.)

\*\*Test duration slob ms.

\*\*Under normal operating conditions this current is negative. This test guarantees that positive leakage current will not exceed the limit shown.

\*\*Apply momentarily 4.5 V, then ground to clock.

### **OPERATING CHARACTERISTICS**

Data must be applied to the J-K inputs while the clock is low. When the clock input goes to the positive logic "1" state, the data at the J and K inputs is transferred to the master section, where it is stored until the clock changes to the positive logic "0" state. Data at the J and K inputs must not be changed while the clock is high. When the clock returns to the positive logic "0" state, information in the master section is transferred to the slave section.

Application of a logic "0" to the RESET input will

force the  $\overline{\mathbf{Q}}$  output to the logic "1" state. The  $\overline{\text{RESET}}$  input overrides the clock.

Since no charge storage is involved in this flip-flop, rise and fall times are not important to its operation, Clock fall times as long as 1.0  $\mu$ s will not adversely affect the operation of the flip-flop. The clock pulse need only be wide enough to allow the data to settle in the master section. This time, which is the setup time for a logic "1", is 12 ns minimum.

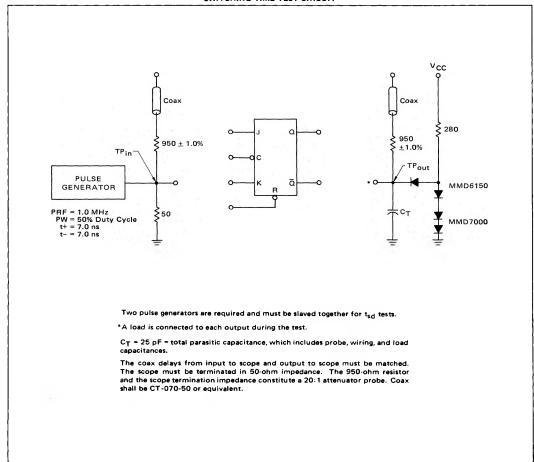

### SWITCHING TIME TEST CIRCUIT

### **TEST PROCEDURES**

| TEST                                | 0.44001          | 1 | INPUT |       | _   | ō |     | LIMITS |      |

|-------------------------------------|------------------|---|-------|-------|-----|---|-----|--------|------|

| 1551                                | SYMBOL           | Ĉ | J,K   | R     | o . |   | Min | Max    | Unit |

| Toggle Frequency                    | f <sub>Tog</sub> | Α | 2.4 V | 5.0 V | 1   | t | 25  | _      | MHz  |

| Turn-On Delay-<br>Clock to Output   | <sup>†</sup> pd+ | Α | 2,4 V | 2.4 V | С   | D | -   | 21     | ns   |

| Turn-Off Delay-<br>Clock to Output  | <sup>†</sup> pd- | А | 2.4 V | 2.4 V | С   | D | -   | 27     | ns   |

| *Turn-On Delay-<br>Reset to Output  | t <sub>pd+</sub> | А | 2,4 V | В     | С   | D | -   | 13     | ns   |

| *Turn-Off Delay-<br>Reset to Output | <sup>t</sup> pd- | A | 2.4 V | В     | С   | D | _   | 24     | ns   |

- Letters shown in test columns refer to waveforms shown.

\*Clock pulse negative edge must occur when reset pulse is in "1" state.

- †Output shall toggle with each input pulse.

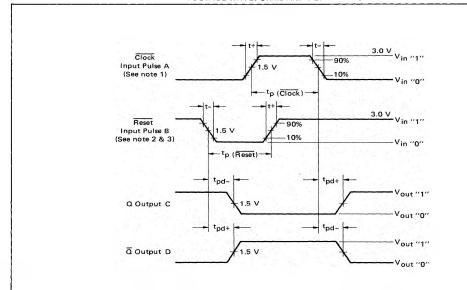

## **VOLTAGE WAVEFORMS AND DEFINITIONS**

# NOTES

- 1. When testing  $t_{Tog}$ ,  $\overline{Clock}$  characteristics are t+ = t-  $\leq$  3.0 ns,  $t_{D}$  ( $\overline{Clock}$ ) = 12 ns, PRF = 25 MHz. When testing  $t_{pd+}$ ,  $t_{pd-}$ ,  $\overline{Clock}$  characteristics are t+ = t-  $\leq$  7.0 ns,  $t_{D}$  ( $\overline{Clock}$ ) = 20 ns, PRF = 1.0 MHz.

- 2. Reset input dominates regardless of state of clock or J-K inputs.

- 3. Reset pulse characteristics t+ = t-  $\leq$ 7.0 ns, tp (Reset) = 16 ns, PRF = 1.0 MHz