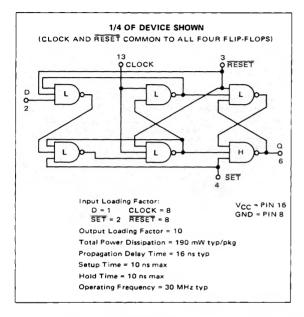

QUAD TYPE D FLIP-FLOP

## MC4015L,P\*

L suffix = 16-pin dual in-line ceramic package (Case 620).

P suffix = 16-pin dual in-line plastic package (Case 612).

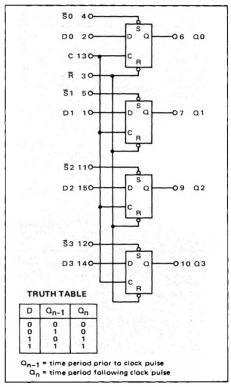

This quad type D flip-flop triggers on the positive edge of the clock input. During the clock transition the state of the D input is transferred to the Q output. The device is useful in shift registers and simple counters.

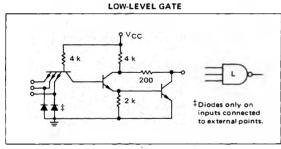

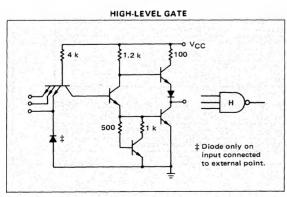

Power dissipation is minimized and output drive capability is maximized by connecting low and high-level gates as shown by the logic diagram to form each of the four flip-flops.

## OPERATING CHARACTERISTICS

Data must be present at the D input 10 ns prior to the rise of the clock, and remain 10 ns after the clock signal rises. Data may be changed any time during the clock cycle except the interval between the setup time (10 ns) and the hold time (10 ns) without affecting the operation of the flip-flop. The data input is inhibited when the clock is high. When the clock is in the low state, the input steering section continually reflects the state of the D input. Information present at the D input during the time interval between the setup and hold times is transferred to the bistable section on the positive edge of the clock, and outputs Q and  $\overline{\Omega}$  respond accordingly.

The flip-flops can be set or reset directly at any time, regardless of the state of the clock, by applying a low state to the direct  $\overline{\text{Set}}$  or  $\overline{\text{Reset}}$  inputs.

## INPUT and OUTPUT LOADING FACTORS with respect to MTTL and MDTL families

| FAMILY | MC4015<br>INPUT<br>LOADING<br>FACTOR | MC4015<br>OUTPUT<br>LOADING<br>FACTOR |

|--------|--------------------------------------|---------------------------------------|

| MC4000 | 1.0                                  | 10                                    |

| MC400  | 1.0                                  | 10                                    |

| MC2000 | 0.67                                 | 6                                     |

| MC3000 | 0.7                                  | 8                                     |

| MC7400 | 1.0                                  | 12                                    |

| MC830  | 1,15**                               | 10                                    |

Note: Differences in MC4000 series loading factors result from differences in specifications for each family.

\*\*Applies only when input is being driven by MDTL gate with 2.0 kilohm pullup resistor. Logic "1" state drive limitations of gates with 6.0 kilohm pullup resistors reduced rive capability to fan-out of 3.

## DC ELECTRICAL CHARACTERISTICS

$(T_A = 0 \text{ to } 75^{\circ}\text{C})$

| Characteristic        | Symbol              | Value           | Conditions                                                     |

|-----------------------|---------------------|-----------------|----------------------------------------------------------------|

| Input                 |                     |                 |                                                                |

| Forward Current - D   |                     | ~1.6 mAdc max   |                                                                |

| SET                   | lF1                 | -3.2 mAdc max   | V <sub>in</sub> = 0.4 Vdc, V <sub>CC</sub> = 5.25 Vdc          |

| RESET, CLOCK          |                     | -12.8 mAdc max  |                                                                |

| D                     |                     | -1.4 mAdc max   |                                                                |

| SET                   | 1F2                 | -2.8 mAdc max   | V <sub>in</sub> = 0.4 Vdc, V <sub>CC</sub> = 4.75 Vdc          |

| RESET, CLOCK          |                     | -11.2 mAdc max  |                                                                |

| Leakage Current - D   |                     | 40 μAdc max     |                                                                |

| SET                   | 1 <sub>R</sub>      | 80 μAdc max     | V <sub>in</sub> = 2.5 Vdc, V <sub>CC</sub> = 5.25 Vdc          |

| RESET, CLOCK          |                     | 320 μAdc max    |                                                                |

| Breakdown Voltage     | B∨in                | 5.5 Vdc max     | Iin = 1.0 mAdc, V <sub>CC</sub> = 5.25 Vdc, T <sub>A</sub> = 2 |

| Clamp Voltage         | V <sub>D</sub>      | -1.5 Vdc max    | ID = -10 mAdc, VCC = 4.75 Vdc, TA = 2                          |

| Threshold Voltage     | V <sub>th</sub> "1" | 2.0 Vdc         | T <sub>A</sub> = 0°C                                           |

|                       |                     | 1.8 Vdc         | T <sub>A</sub> = +25°C, or T <sub>A</sub> = +75°C              |

|                       | V <sub>th</sub> "0" | 1.1 Vdc         | T <sub>A</sub> = 0°C, or T <sub>A</sub> = +25°C                |

|                       |                     | 0.9 Vdc         | T <sub>A</sub> = +75°C                                         |

| Output                |                     |                 |                                                                |

| Output Voltage        | VOL                 | 0.4 Vdc max     | RESET = 0, IOL = 16 mAdc, VCC = 4.75                           |

|                       |                     | 0.4 Vdc max     | RESET = 0, IOL = 17.6 mAdc, VCC = 5.2                          |

|                       | Voн                 | 2.5 Vdc min     | SET = 0, I <sub>OH</sub> = -1.6 mAdc, V <sub>CC</sub> = 4.75   |

| Short-Circuit Current | <sup>I</sup> SC     | -20 to -65 mAdc | V <sub>CC</sub> = 5.0 Vdc, output grounded                     |