# MN3011 3328-STAGE BBD with 6 TAPS

#### General description

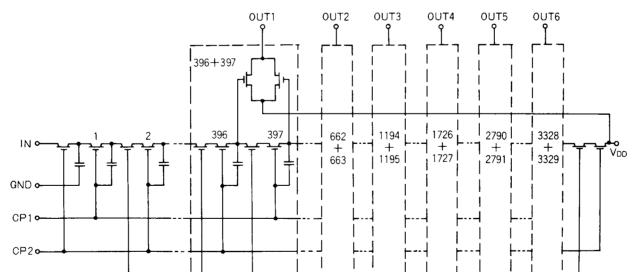

The MN3011 is a 3328-stage BBD with 6 tap outputs suitably used for reverberation effect in audio equipments such as electronic organs. Signal of different delay time is output from each of the 6 tap outputs. Natural reverberation effect can easily be realized by mixing these output signals properly. Dealy time is freely varied by changing the clock frequency.

#### Features

- 3328-stage audio signal delay device with 6 output taps.

- The stage of each output tap has no relation to multiplex, each other, therefore natural reverberation effect can be obtained by mixing output signals.

- Clock component cancellation capability.

- Dynamic rage:  $S/N \ge 76$ dB typ.

- No insertion loss: L<sub>i</sub> = 0dB typ.

- Low distortion: THD = 0.4% typ.

- P channel silicon gate process.

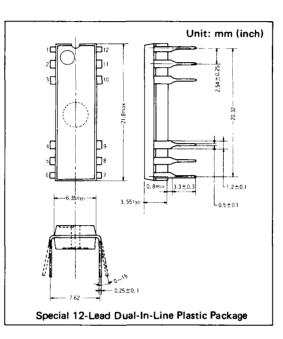

- Special 12-Lead Dual-In-Line Plastic Package.

#### Applications

- Reverberation effect in audio equipment.

- Chours effect in electronic musical instruments.

| Maximum | Delay | y Time t | y Tap ( | Output |

|---------|-------|----------|---------|--------|

|---------|-------|----------|---------|--------|

| Terminal of the Tap Output | OUT 1 | OUT 2 | OUT 3 | OUT 4 | OUT 5 | OUT 6 | Remarks     |

|----------------------------|-------|-------|-------|-------|-------|-------|-------------|

| Stages of BBD (Stage)      | 396   | 662   | 1194  | 1726  | 2790  | 3328  |             |

| Maximum Delay Time (mS)    | 19.8  | 33.1  | 59.7  | 86.3  | 139.5 | 166.4 | Clock 10KHz |

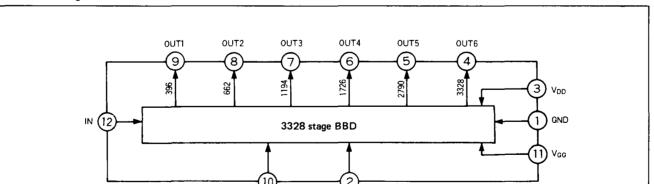

#### Block Diagram

Panasonic

-50-

#### MN3011

# **Absolute Maximum Ratings** (Ta = 25°C)

| Item                                 | Symbol                            | Ratings  | Unit | Remarks  |  |

|--------------------------------------|-----------------------------------|----------|------|----------|--|

| Terminal Voltage                     | V <sub>DD</sub> , V <sub>GG</sub> | -18~+0.3 | v    | GND = 0V |  |

| Input Terminal Voltage               | VI, VCP                           | -18~+0.3 | V    | 11       |  |

| Ouptut Voltage                       | Vo                                | -18~+0.3 | V    | 11       |  |

| <b>Operating Ambient Temperature</b> | Topr                              | -20~+70  | Ĉ    | 11       |  |

| Storage Temperature                  | Tstg                              | -55~+125 | Ĵ    | 4        |  |

#### **Operating Condition** (Ta = 25°C)

| Item                    | Symbol           | Condition                                     | Min. | Тур.            | Max.     | Unit |

|-------------------------|------------------|-----------------------------------------------|------|-----------------|----------|------|

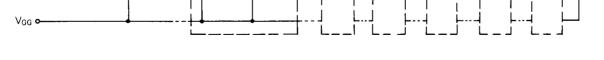

| Drain Supply Voltage    | V <sub>DD</sub>  |                                               | -14  | —15             | —16      | ۷    |

| Gate Supply Voltage     | V <sub>GG</sub>  | ·····                                         |      | $V_{DD} + 1$    |          | V    |

| Clock Voltage "H" Level | V <sub>СРН</sub> | · · · · · · · · · · · · · · · · · · ·         | 0    |                 | -1.3     | V    |

| Clock Voltage "L" Level | VCPL             | ,                                             |      | V <sub>DD</sub> |          | ٧    |

| Clock Input Capacitance | Сср              |                                               |      |                 | 2300     | pF   |

| Clock Frequency         | f <sub>CP</sub>  |                                               | 10   |                 | 100      | kHz  |

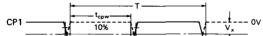

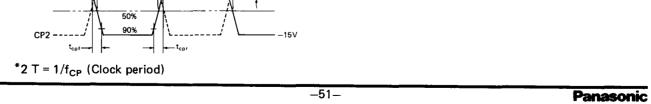

| Clock Pulse Width *1    | t <sub>cpw</sub> |                                               |      |                 | 0.5T*2   |      |

| Clock Rise Time *1      | t <sub>cpr</sub> |                                               |      |                 | 500      | ns   |

| Clock Fall Time *1      | t <sub>cpf</sub> |                                               |      |                 | 500      | ns   |

| Clock Cross Point *1    | Vx               | ,,, <u>,,</u> ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 0    |                 | <u> </u> | ٧    |

| Input DC Bias           | VBias            |                                               | - 5  |                 | -10      | ٧    |

Electrical Characteristics (Ta = 25°C,  $V_{DD} = V_{CPL} = -15V$ ,  $V_{CPH} = 0V$ ,  $V_{GG} = -14V$ ,  $R_L = 56k\Omega$ )

| Item                      | Symbol            | Condition                                                                | Min.  | Тур. | Max.  | Unit  |

|---------------------------|-------------------|--------------------------------------------------------------------------|-------|------|-------|-------|

| Signal Delay Time         |                   |                                                                          |       |      |       |       |

| OUT 1 Terminal            | t <sub>D1</sub>   |                                                                          | 1.98  |      | 19.8  | ms    |

| OUT 2 Terminal            | t <sub>D2</sub>   |                                                                          | 3.31  |      | 33.1  | ms    |

| OUT 3 Terminal            | t <sub>D3</sub>   | $f_{CP}=10$ kHz ~100kHz                                                  | 5.97  |      | 59.7  | ms    |

| OUT 4 Terminal            | t <sub>D4</sub>   |                                                                          | 8.63  |      | 86.3  | ms    |

| OUT 5 Terminal            | t <sub>D5</sub>   | ]                                                                        | 13.95 |      | 139.5 | ms    |

| OUT 6 Terminal            | t <sub>D6</sub>   |                                                                          | 16.64 |      | 166.4 | ms    |

| Input Signal Frequency    | fi                | $f_{CP} = 40 \text{kHz}$ , $-3 \text{dB}$                                | 10    |      |       | kHz   |

| Input Signal Voltage      | Vi                | THD=2.5%                                                                 | 1.0   |      |       | Vrms  |

| Insertion Loss            | Li                | $f_{CP}=40kHz$ , $f_i=1 kHz$                                             | -4    | 0    | 4     | dB    |

| Total Harmonic Distrotion | THD               | $f_{CP} = 40 \text{kHz}, f_i = 1 \text{ kHz}$<br>$V_i = 0.78 \text{Vms}$ |       | 0.4  | 2.5   | %     |

| Noise Voltage             |                   |                                                                          |       |      |       |       |

| OUT 1, OUT 2, OUT 3       | V <sub>no 1</sub> | f <sub>cp</sub> = 100kHz                                                 |       |      | 0.4   | mVrms |

| OUT 4, OUT 5, OUT 6       | V NO 1            | Weighted by "A" curve                                                    |       |      | 0.4   | mvms  |

| Signal to Noise Ratio     |                   |                                                                          |       |      |       |       |

| OUT 1, OUT 2, OUT 3       | S/N <sub>1</sub>  | f <sub>cp</sub> = 100kHz, Weighted by "A" curve                          |       | 76   |       | dB    |

| OUT 4, OUT 5, OUT 6       | 5/N1              | Vno vs. max. output signal                                               |       | . /0 |       |       |

\*1 Clock Pulse Waveforms

# MN3011

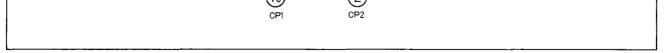

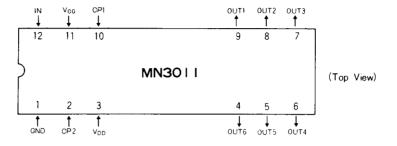

#### Terminal Assignments

#### Terminal Description

| Terminal No. | Symbol          | Terminal Name                     | Description                                                                                                                         |

|--------------|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1            | GND             | Earth terminal                    | Connected to the earth terminal.                                                                                                    |

| 2            | CP2             | Clock input 2                     | Basic clock pulse is applied to transfer the electron of BBD.                                                                       |

| 3            | V <sub>DD</sub> | V <sub>DD</sub> applying terminal | Supply voltage of -15V is applied.                                                                                                  |

| 4            | OUT 6           | Output terminal 6                 | Output of 3328th and 3329th-stage are composed and output is obtained by cancelling the clock components.                           |

| 5            | OUT 5           | Output terminal 5                 | Composed output of 2790th and 2791st-stage are obtained.                                                                            |

| 6            | OUT 4           | Output terminal 4                 | Composed output of 1726th and 1727th-stage are obtained.                                                                            |

| 7            | OUT 3           | Output terminal 3                 | Composed output of 1194th and 1195th-stage are obtained.                                                                            |

| 8            | OUT 2           | Output terminal 2                 | Composed output of 662nd and 663rd-stage are obtained.                                                                              |

| 9            | OUT 1           | Output terminal 1                 | Composed output of 396th and 397th-stage are obtained.                                                                              |

| 10           | CP1             | Clock input 1                     | Clock pulse of reverse phase to CP2 is applied.                                                                                     |

| 11           | V <sub>GG</sub> | V <sub>GG</sub> applying terminal | This terminal applies bias of $V_{GG} = V_{DD} + 1V$ to the MOS transistor gate that is inserted in series to transfer gate of BBD. |

| 12           | IN              | Signal input terminal             | Analog signal to be delayed is input.<br>Most suitable DC bias should be applied to this terminal.                                  |

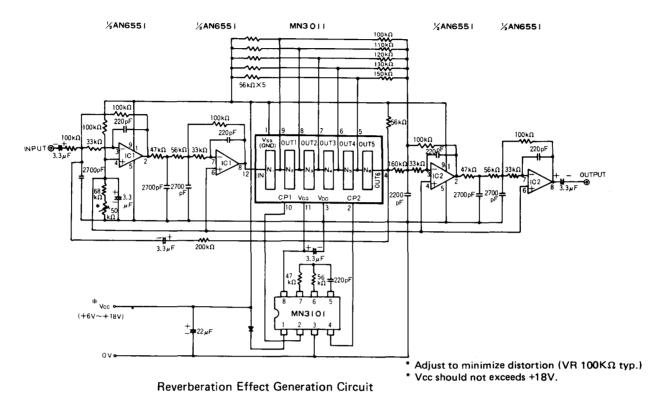

# 📕 Circuit Diagram

Panasonic

-52-

MN3011

#### Application Circuit

•

Pattern Drawing of the Printed Circuit Board (Real size)

Application Circuit Electrical Characteristics ( $V_{CC} = +15V$ , Ta = 25°C)

| ••                        |                 |                                                              | •        |          |             |           |

|---------------------------|-----------------|--------------------------------------------------------------|----------|----------|-------------|-----------|

| Item                      | Symbol          | Condition                                                    | Min.     | Тур.     | Max.        | Unit      |

| Supply Current            | loc             |                                                              |          | 11(8)    | 15(10)      | mA        |

| Power Dissipation         | Ptot            |                                                              |          | 165 (70) |             | mW        |

| Signal Delay Time         | t <sub>D</sub>  | OUT 6 : f <sub>CP</sub> =15~20kHz                            | 83       | 98       | 111         | ms        |

| Cut-off Frequency         | f <sub>co</sub> |                                                              |          | 3        |             | kHz       |

| Input Signal Swing        | Vi              | THD=2.5%                                                     |          |          | 1.1(0.5)    | Vrms      |

| Insertion Loss            | Li              | OUT 3: $f_i = 1 \text{ kHz}, V_i = 300 \text{ mV}$           | 0        | 2        | 4           | dB        |

| Total Harmonic Distortion | THD             | $f_i = 1 \text{ kHz}, V_i = V_i(\text{max.}) - 6 \text{ dB}$ |          | 0.4(0.5) |             | %         |

| Noise Voltage             | V <sub>no</sub> | $OUT 3: V_i = 0 V$                                           |          | 0.4(0.4) |             | mVrms     |

| Signal to Noise Ratio     | S/N             | $V_s = V_i (max.)$                                           |          | 70 (60)  | 1           | dB        |

|                           |                 |                                                              | nte of ( | moon the | figure et \ | 1-<br>1 c |

Contents of ( ) mean the figure at VCC = +9V

-53-

Panasonic