# **DKI** semiconductor MSM82C88AS/GS

# **BUS CONTROLLER**

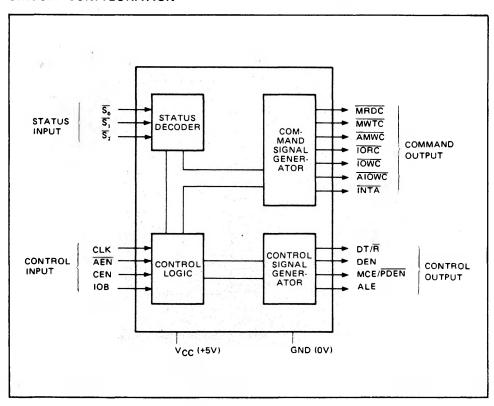

#### **GENERAL DESCRIPTION**

The MSM82C88 is a bus controller for the MSM80C86 and the MSM80C88 CPUs. Based on silicon gate CMOS technology, a low-power 16-bit microprocessor system can be realized.

The MSM82C88 generates commands control timing signals on reception of status signals from the CPU.

#### **FEATURES**

- · Silicon gate CMOS technology for low power consumption

- 3 to 6V wide voltage range and single power supply

- -40 to 85°C wide guaranteed operating temperature ranoe

- Advanced write control output

- Three-state command output driver

- System bus mode & I/O bus mode

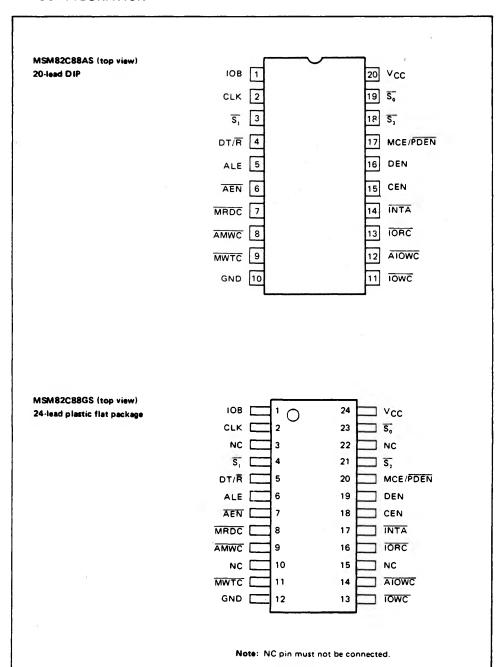

- 20-pin DIP (MSM82C88AS)

- 24-pin flat package (MSM82C88GS)

#### CIRCUIT CONFIGURATION

# PIN CONFIGURATION

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Sumbal | Candisiana             | Lin                         |            |      |  |

|----------------------|--------|------------------------|-----------------------------|------------|------|--|

| Parameter            | Symbol | Conditions             | MSM82C88AS                  | MSM82C88GS | Unit |  |

| Power Supply Voltage | Vcc    |                        | -0.5 ~ +7                   |            | ٧    |  |

| Input Voltage        | VIN    | With respect<br>to GND | -0.5 ~ V <sub>CC</sub> +0.5 |            | V    |  |

| Output Voltage       | Vout   |                        | -0.5 ~ \                    | ٧          |      |  |

| Storage Temperature  | Tstg   | -                      | <b>-55</b> ∼ 150            |            | °c   |  |

| Power Dissipation    | PD     | Ta = 25°C              | 1.1                         | 0.7        | w    |  |

# **OPERATING RANGES**

| Parameter             | Symbol | Limits   | Unit |

|-----------------------|--------|----------|------|

| Power Supply Voltage  | Vcc    | 3 ~ 6    | V    |

| Operating Temperature | TOP    | -40 ~ 85 | °C   |

# RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol           | Min. | Тур. | Max.                 | Unit |

|-----------------------|------------------|------|------|----------------------|------|

| Power Supply Voltage  | Vcc              | 4.5  | 5    | 5.5                  | ٧    |

| Operating Temperature | ТОР              | -40  | +25  | +85                  | °C   |

| "L" Input Voltage     | V <sub>IL1</sub> | -0.3 | -    | +0.8                 | V    |

| "H" Input Voltage     | V <sub>IH1</sub> | 3.0  | -    | V <sub>CC</sub> +0.3 | V    |

| "L" Input Voltage     | V <sub>IL2</sub> | -0.3 | -    | +0.8                 | V    |

| "H" Input Voltage     | V <sub>IH2</sub> | 2.2  | _    | V <sub>CC</sub> +0.3 | V    |

Note:  $V_{IL1}$  and  $V_{IH1}$  are input voltages for CLK,  $\overline{s_0}$ ,  $\overline{s_1}$ , and  $\overline{s_2}$ .  $V_{IL2}$  and  $V_{IH2}$  are input voltages for  $\overline{AEN}$ , CEN, and IOB.

$(V_{CC} = 4.5V \text{ to } 5.5V, Ta = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                      | Parameter Symbol Conditions |                              | Min. | Тур. | Max. | Unit | Remarks |

|--------------------------------|-----------------------------|------------------------------|------|------|------|------|---------|

| "L" Output Voltage             | VOL                         | Command output<br>IOL = 12mA | -    | _    | 0.45 | ٧    |         |

| E Output Voltage               | VOL                         | Control output               | -    | -    | 0.45 | ٧    |         |

| "H" Output Voltage             | V                           | Command output<br>IOH = -5mA | 3.7  | -    | -    | ٧    |         |

| H Output Voltage               | Voн                         | Control output<br>IOH = -1mA | 3.7  | -    | -    | v    |         |

| Input Leak Current             | ILI                         | 0 ≤ VIN ≤ VCC                | -10  | -    | 10   | μА   | Note 1  |

| Output Leak Current            | 'LO                         | 0 ≤ VOUT ≤ VCC               | -10  | _    | 10   | μА   |         |

| Status Input Current           | LIS                         | 0 ≤ VIN ≤ VCC                | -100 | -    | 10   | μА   | Note 2  |

| Operation Power Supply Current | Icco                        | CL = OpF                     | -    | -    | 10   | mA   |         |

| Standby Power Supply Current   | Iccs                        | Note 3                       | _    | _    | 100  | μА   |         |

Note 1. This input leak current is the leak current on input pins except status inputs  $(\overline{s}_0, \overline{s}_1, \text{ and } \overline{s}_2)$ .

Note 2. The status input leak current is the leak current at the status inputs  $(\overline{s_0}, \overline{s_1}, \text{ and } \overline{s_2})$ .

Note 3. The measuring conditions for the standby power supply current include the  $\overline{s_0}$ ,  $\overline{s_1}$ , and  $\overline{s_2}$  status inputs being at  $V_{CC}$  potential, and the other inputs being at  $V_{CC}$  or GND. All output pins are left open.

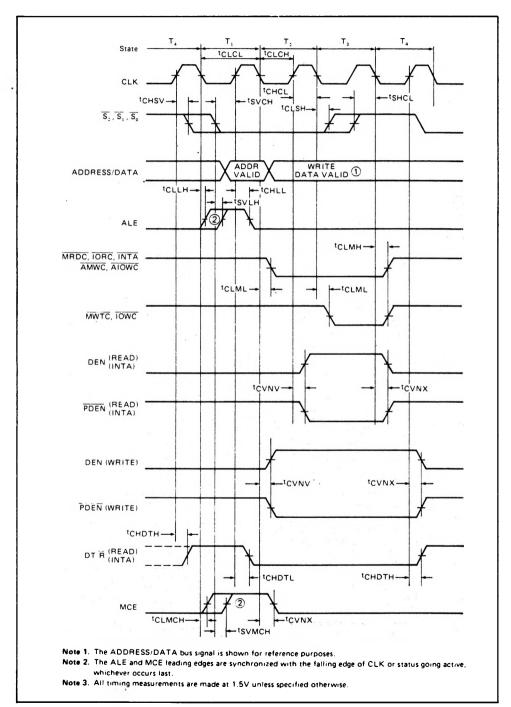

# AC CHARACTERISTICS

(V<sub>CC</sub> = 4.5V to 5.5V, Ta = -40°C to +85°C)

#### Timing conditions

| Parameter                  | Symbol            | Min. | Max. | Unit |

|----------------------------|-------------------|------|------|------|

| Clock Cycle                | †CLCL             | 200  | _    | nS   |

| Clock Low Time             | tCLCH             | 118  | _    | nS   |

| Clock High Time            | tCHCL             | 65   | _    | nS   |

| Status Active Setup Time   | <sup>t</sup> SVCH | 35   | _    | nS   |

| Status Inactive Hold Time  | tCHSV             | 10   | -    | n\$  |

| Status Inactive Setup Time | †SHCL             | 35   | -    | nS   |

| Status Active Hold Time    | <sup>†</sup> CLSH | 10   | -    | nS   |

# Timing response

| Paramèter                                                | Symbol             | Min. | Max.    | Unit | Test Circuit | Remarks           |

|----------------------------------------------------------|--------------------|------|---------|------|--------------|-------------------|

| Delay from CLK Leading Edge to DEN,<br>PDEN Active       | †CVNV              | 5    | 45      | nS   | 4            |                   |

| Delay from CLK Trailing Edge to DEN,<br>PDEN Inactive    | ¹CVNX              | 5    | 45      | nS   | 4            | -                 |

| Delay from CLK Trailing to ALE<br>Active                 | <sup>†</sup> CLLH  | - 6  | 35      | nS   | 4            |                   |

| Delay from CLK Trailing Edge to<br>MCE Active            | <sup>†</sup> CLMCH | _    | 35      | nS   | 4            |                   |

| Delay from Status Input Falling Edge to ALE Active       | <sup>†</sup> SVLH  | -    | 35      | nS   | 4            |                   |

| Delay from Status Input Falling Edge<br>to MCE Active    | <sup>1</sup> SVMCH | -    | 35      | nS   | 4            |                   |

| Delay from CLK Leading Edge to<br>ALE Inactive           | <sup>†</sup> CHLL  | 4    | 35      | nS   | 4            |                   |

| Delay from CLK Trailing Edge to<br>Command Output Active | <sup>†</sup> CLML  | 5    | 45      | nS   | 3            |                   |

| Delay from CLK Trailing Edge to Command Output Inactive  | <sup>t</sup> CLMH  | 5    | 45      | nS   | 3            |                   |

| Delay from CLK Leading Edge to DT/R Active               | tCHDTL .           | -    | 50      | nS   | 4            | *                 |

| Delay from CLK Leading Edge to DT/R Inactive             | tCHDTH             | -    | 35      | nS   | 4            |                   |

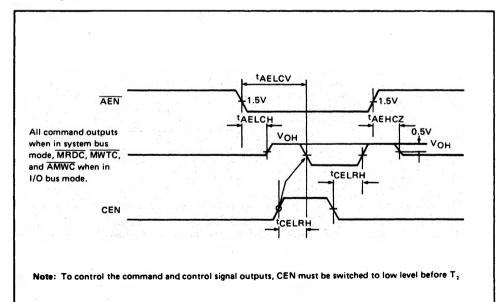

| Delay from AEN Leading Edge to<br>Command Enable         | <sup>1</sup> AELCH | _    | 45      | nS   | 2            |                   |

| Delay from AEN Trailing Edge to Command Disable          | <sup>t</sup> AEHCZ | _    | 40      | nS   | 1            |                   |

| Delay from AEN Leading Edge to<br>Command Output Active  | <sup>t</sup> AELCV | 90   | 250     | nS   | 3            |                   |

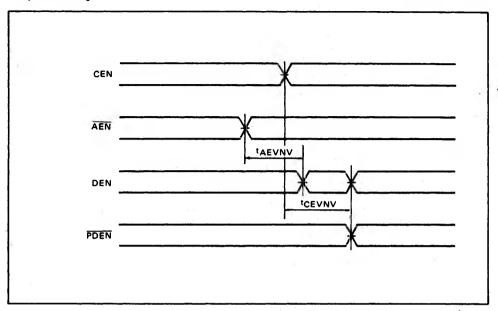

| Delay from AEN to DEN                                    | <sup>t</sup> AEVNV | _    | 35      | nS   | 4            |                   |

| Delay from CEN to DEN, PDEN                              | †CEVNV             | _    | 35      | nS   | 4            |                   |

| Delay from CEN to Command Output                         | tCELRH             | -    | CLML+20 | nS   | 3            |                   |

| Output Rise Time                                         | 10LOH              | _    | 20      | nS   | 3, 4         | From 0.8V to 2.2V |

| Output Fall Time                                         | tOHOL              | -    | 12      | nS   | 3,4          | From 2.2V to 0.8V |

Note: AC timing measurements are made at 1.5V for both logic "1" and "0". Input rise and fall times are

5 ± 2 nS between 0.8V and 2.2V for AEN, CEN and IOB.

$8 \pm 2$  nS between 0.8V and 3.0V for  $\overline{s_0}$ ,  $\overline{s_1}$ ,  $\overline{s_2}$  and CLK.

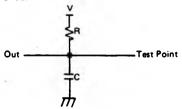

#### Test Circuit

| Test Circuit | V(V) | $R(\Omega)$ | C(PF) |

|--------------|------|-------------|-------|

| 1            | 1.5  | 180         | 50    |

| 2            | 1.5  | 300         | 150   |

| 3            | 2.74 | 190         | 150   |

| 4            | 3.34 | 360         | 80    |

#### TIME CHARTS

DEN, PDEN Timing

# **AEN** Timing

| Pin Name                                                           | Input/output      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>s<sub>0</sub></u> , <u>s<sub>1</sub></u> , <u>s<sub>2</sub></u> | Input             | These pins are input pins for status signals $(\overline{s_0}, \overline{s_1}, \text{ and } \overline{s_2})$ , output from the CPU (MSM80C86, 80C88). The MSM82C88 generates commands and control signals after decoding these status signals. Since these pins are connected to an internal pull-up resistor, they are set to high level when the CPU status output is at high impedance.                                                                                                                     |

| CLK                                                                | Input             | This pin is the input pin for clock signal output from the clock generator (MSM82C84A). The timing of all MSM82C88 output signals is controlled by this clock signal.                                                                                                                                                                                                                                                                                                                                          |

| ALE                                                                | Output            | Strobe signal for latching output address from the CPU to address latch.  Address latching occurs on the trailing edge of ALE.                                                                                                                                                                                                                                                                                                                                                                                 |

| DEN                                                                | Output            | Control signal for setting the data bus transceiver to data enable. The local bus or system bus transceiver is enabled when this signal is high. DEN is switched to low when the CEN input is low.                                                                                                                                                                                                                                                                                                             |

| DT/R                                                               | Output            | Control of the direction of data flow in the data bus transceiver. When the CPU is switched to write mode, this signal is high, and when switched to read mode, this signal is low.                                                                                                                                                                                                                                                                                                                            |

| AEN                                                                | Input             | Address enable signal.  • IOB = L (SYSTEM BUS MODE)  When the AEN input is switched to high level, all command outputs are switched to high impedance status.  • IOB = H (I/O BUS MODE)  When the AEN input is switched to high level, only the MRDC, MWTC and AMWC command outputs are switched to high impedance status.  When AEN is switched from high to low level, high impedance command outputs are not switched to active status (low level) for at least 90 nS irrespective of the IOB input status. |

| CEN                                                                | Input             | Command enable signal.  All command outputs, DEN and PDEN outputs are switched to inactive status when a low level input is applied to CEN. All command outputs, DEN and PDEN outputs are switched to active status when a high level input is applied to CEN.                                                                                                                                                                                                                                                 |

| IOB                                                                | Input             | I/O bus mode signal.  The MSM82C88 is switched to I/O bus mode when a high level input is applied to IOB, and to system bus mode when a low level input is applied.                                                                                                                                                                                                                                                                                                                                            |

| IOWC                                                               | 3-state output    | This pin is active-low, and three-state output. This signal is for writing data into the I/O device.                                                                                                                                                                                                                                                                                                                                                                                                           |

| AIOWC                                                              | 3-state<br>output | This pin is active-low and three-state output. Although this signal is also used for writing into I/O devices like the I/O write command (IOWC), it is made active one clock earlier than IOWC.                                                                                                                                                                                                                                                                                                                |

| IORC                                                               | 3-state<br>output | This pin is active-low and three-state output. This signal is for reading date from 1/O devices.                                                                                                                                                                                                                                                                                                                                                                                                               |

| MWTC                                                               | 3-state output    | This pin is active-low and three-state output. This signal is for writing data into memory.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AMWC                                                               | 3-state<br>oùtput | This pin is active-low and three-state output. Although this signal is also used for writing into memory like the memory write command (MWTC) it is made active one cycle earlier than MWTC.                                                                                                                                                                                                                                                                                                                   |

| MRDC                                                               | 3-state output    | This pin is active-low and three-state output. This signal is for reading data from memory.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INTA                                                               | 3-state<br>output | This pin is active-low and three-state output. This signal informs the inter-<br>rupt controller that the interrupt has been accepted, and then requests<br>output of a vector address onto the data bus.                                                                                                                                                                                                                                                                                                      |

| Pin Name        | Input/output | Function                                                                                                                                                                                                                                                                         |  |  |  |  |

|-----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MCE/PDEN Output |              | This pin has two functions.  MCE (IOB = Low) master cascade enable function.  This is an active-high signal and is used to enable a slave PIC (priority interrupt controller) to read the cascade address output on the data bus by the master PIC during an interrupt sequence. |  |  |  |  |

|                 | ×            | PDEN (IOB = High) peripheral data enable function.  This is a an active-low signal and is used to enable the data bus transceiver on the I/O bus.                                                                                                                                |  |  |  |  |

#### FUNCTION

#### **Command Logic**

The command output is decided by decoding status signals  $(\overline{s_0}$ ,  $\overline{s_1}$ ,  $\overline{s_2}$ ) output from the CPU.

These status signals have the following meanings.

| <u>s</u> | <u>s</u> , | <u>s</u> | CPU status            | Command output |

|----------|------------|----------|-----------------------|----------------|

| 0        | 0          | 0        | Interrupt acknowledge | INTA           |

| 0        | 0          | 1        | I/O read              | IORC           |

| 0        | 1          | 0        | I/O write             | IOWC, AIOWC    |

| 0        | 1          | 1        | Halt                  | _              |

| 1        | 0          | 0        | Instruction fetch     | MRDC           |

| 1        | 0          | 1        | Memory read           | MRDC           |

| 1        | 1          | 0        | Memory write          | MWTC, AMWC     |

| 1        | 1          | 1        | Passive               | _              |

#### I/O Bus Mode (IOB = High)

When an I/O access status signal is received from the CPU in I/O bus mode, one of the I/O commands (IORC, IOWC, AIOWC, INTA) corresponding to the status signal becomes active irrespective of the AEN status. At the same time, the PDEN and DT/R outputs which control the data bus transceiver are generated.

As in system bus mode, the memory commands (MRDC, MWTC, and AMWC) are not switched to low level for at least 90 ns after AEN is switched to low level.

#### System Bus Mode (IOB = Low)

When the bus is usable, the MSM82C88 is enabled by the  $\overline{AEN}$  signal from the bus arbiter. Consequently, no command output becomes active unless the  $\overline{AEN}$  signal becomes low. Also note that there is a delay of at least 90 ns before any command output becomes active after the  $\overline{AEN}$  signal is switched to low level.

System bus mode is used when more than one CPU is connected to a single bus, and the bus I/O, memory, etc. are used in common.

#### Command Outputs

The advanced write commands (AIOWC and AMWC) become active one cycle earlier than normal

write commands (IOWC and MWTC). This prevents the CPU from being switched to an additional period of wait status.

INTA (interrupt acknowledge) is output during the interrupt acknowledge cycle in the same way as MRDC in the read cycle. The purpose of this signal is to inform the device which has requested the interrupt that the interrupt has been accepted, and requests a vector address output on the data bus.

MRDC - Memory read command

MWTC - Memory write command

IORC - I/O read command

IOWC - I/O write command

AMWC — Advanced memory write command

AIOWC - Advanced I/O write command

INTA - Interrupt acknowledge

#### Control Output

The control output signals are DEN (Data Enable), DT/R (Transmit/Receive), and MCE/PDEN (Master Cascade Enable/Peripheral Data Enable).

The DEN signal enables the local bus or system bus, when it is high.

The DT/R signal determines the direction of the data on the local bus or system bus.

The function of the MCE/PDEN pin is switched according to IOB. The PDEN function is selected in I/O bus mode (IOB = high) to provide the I/O or peripheral/ system bus data enable signal. When the MCE function is selected in system bus mode (IOB = low), the MCE signal is active (high) level at an interrupt acknowledge status.

The MCE signal is used when a master and slave interrupt controller exists in the system.

#### ALE (Address Latch Enable)

ALE is generated in each machine cycle to latch the current address to the address latch.

#### **CEN (Commend Enable)**

This signal is used to enable command outputs. All command outputs become inactive if a low level input is applied to the CEN pin.