# **OKI** semiconductor

# MSM83C55-XXRS/GS

2048 x 8 BIT MASK ROM WITH I/O PORTS

### GENERAL DESCRIPTION

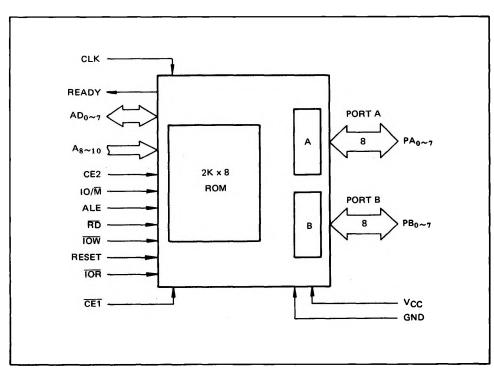

MSM83C55 is a combination of MROM and I/O devices used in a microcomputer system. Owing to the adoption of the CMOS silicon gate technology, it operates on a low power supply as small as  $100 \,\mu\text{A}$  (max.) in the standby current in the chip non-select status. As the ROM is composed of 2048 words x 8 bits and its access time (max.) is 400 ns, it can be applied without using the wait state in the 80C85A system, too. The I/O circuit is composed of 2 universal I/O ports. Each of these I/O ports has 8 port lines and each of these port lines can be programmed as input or output line independently.

## **FEATURES**

- High speed and low power consumption owing to adoption of silicon gate CMOS

- Composed of 2048 words x 8 bits

- 3 ~ 6 V single power supply

- Address latch circuit incorporated

- Provided with 2 universal 8-bit I/O ports

- TTL Compatible

- Indivisual I/O port line programmable as input or

- Time division address/data bus

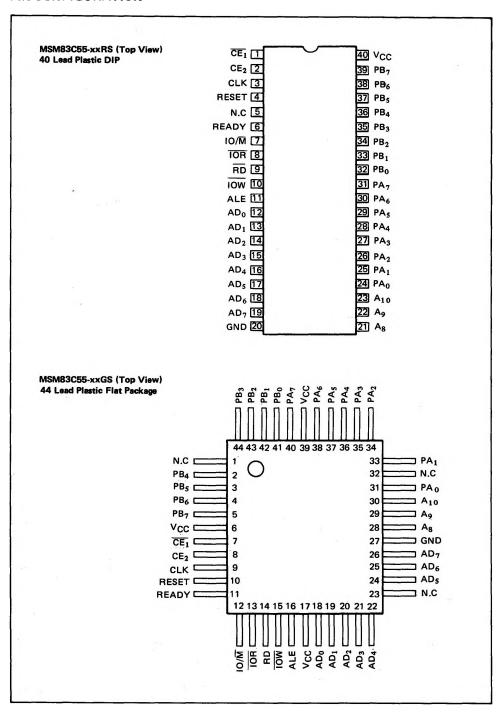

- 40-pin DIP (MSM83C55-xxRS)

- 44-pin flat package (MSM83C55-xxGS)

- Direct interface with MSM80C85A (3MHz)

## **CIRCUIT CONFIGURATION**

# **PIN CONFIGURATION**

# **ABSOLUTE MAXIMUM RATINGS**

| Da                  | 0      | 0 - 1121            | Lin         |            |      |  |

|---------------------|--------|---------------------|-------------|------------|------|--|

| Parameter           | Symbol | Conditions          | MSM83C55RS  | MSM83C55GS | Unit |  |

| Supply Voltage      | vcc    |                     | -0.5 to +   | 7          | V    |  |

| Input Voltage       | VIN    | With respect to GND | -0.5 to V   | V          |      |  |

| Output Voltage      | Vout   |                     | -0.5 to V   | V          |      |  |

| Storage Temperature | Tstg   |                     | -55 to +150 |            | °c   |  |

| Power Dissipation   | PD     | Ta=25°C             | 1.0         | 0.7        | w    |  |

# **OPERATING RANGE**

| Parameter             | Symbol | Limits     | Unit |  |

|-----------------------|--------|------------|------|--|

| Supply Voltage        | _ vcc  | 3 to 6     | ٧    |  |

| Operating Temperature | TOP    | -40 to +85 | °c   |  |

# **RECOMMENDED OPERATING RANGE**

| Parameter             | Symbol | Min. | Тур. | Max.                 | Unit |

|-----------------------|--------|------|------|----------------------|------|

| Supply Voltage        | Vcc    | 4.5  | 5    | 5.5                  | V    |

| Operating Temperature | ТОР    | -40  | +25  | +85                  | °c   |

| "L" Input Voltage     | VIL    | -0.3 |      | +0.8                 | V    |

| "H" Input Voltage     | ViH    | 2.2  |      | V <sub>CC</sub> +0.3 | V    |

# **DC CHARACTERISTICS**

| Parameter                       | Symbol | Conditions                                                                                                                                                                                                                                                                           |                               | Min. | Тур. | Ma×. | Unit        |

|---------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|------|------|-------------|

| "L" Output Voltage              | VOL    | IOL=2mA                                                                                                                                                                                                                                                                              |                               |      |      | 0.45 | V           |

| "H" Output Voltage              | VOH    | I <sub>OH</sub> =-400μA                                                                                                                                                                                                                                                              | 1                             | 2.4  |      |      | v           |

|                                 |        | I <sub>OH</sub> =-40μA                                                                                                                                                                                                                                                               | ]                             | 4.2  |      |      | <b>&gt;</b> |

| Input Leak Current              | ILI    | 0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                                                                                                                                                                                                                                                | V <sub>CC</sub> =4.5V to 5.5V | -10  |      | 10   | μΑ          |

| Output Leak Current             | lLO    | 0 ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>                                                                                                                                                                                                                                               | Ta=-40°C to +85°C             | -10  |      | 10   | μА          |

| Supply Current (standby)        | Iccs   | $\label{eq:center_constraint} \begin{split} \overline{\text{CE1}} & \geqq \text{V}_{\text{CC}}\text{-}0.2\text{V} \\ \text{CE2} & \leqq 0.2\text{V} \\ \text{V}_{\text{IH}} & \geqq \text{V}_{\text{CC}}\text{-}0.2\text{V} \\ \text{V}_{\text{IL}} & \leqq 0.2\text{V} \end{split}$ |                               |      | 0.1  | 100  | μΑ          |

| Average Supply Current (active) | lcc    | IO write<br>cycle time:<br>1 µs                                                                                                                                                                                                                                                      |                               |      |      | 5    | mA          |

# **AC CHARACTERISTICS**

(V<sub>CC</sub>=4.5V to 5.5V, Ta=-40°C to +85°C)

| Parameter                              | Symbol         | Min. | Max. | Unit |

|----------------------------------------|----------------|------|------|------|

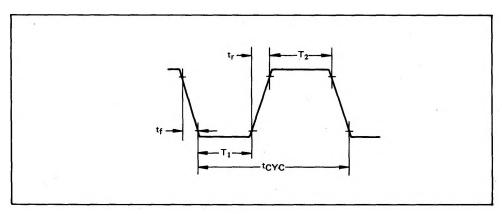

| Clock Cycle Time                       | tCYC           | 320  |      | ns   |

| Clock Pulse Width                      | T <sub>1</sub> | 80   |      | ns   |

| Clock Pulse Width                      | T <sub>2</sub> | 120  |      | ns   |

| Clock Rise and Fall Time               | tf, tr         |      | 30   | ns   |

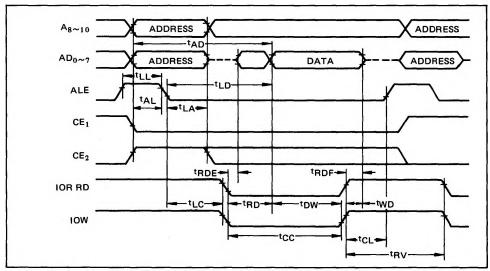

| Address to Latch Setup Time            | tAL            | 50   |      | ns   |

| Address Hold Time after Latch          | tLA            | 30   |      | ns   |

| Latch to READ/WRITE Control            | tLC            | 100  |      | ns   |

| Valid Data Out Delay from READ Control | tRD            |      | 170  | ns   |

| Address Stable to Data Out Valid       | tAD            |      | 400  | ns   |

| Latch Enable Width                     | tLL            | 100  |      | ns   |

| Data Bus Float after READ              | †RDF           | 0    | 100  | ns   |

| READ/WRITE Control to Latch Enable     | tCL            | 20   |      | ns   |

| READ/WRITE Control Width               | tcc            | 250  |      | ns   |

| Data In to WRITE Setup Time            | tDW            | 150  |      | ns   |

| Data In Hold Time after WRITE          | tWD            | 10   |      | ns   |

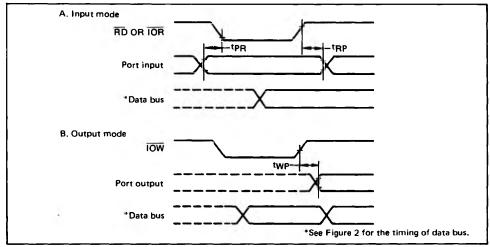

| WRITE to Port Output                   | twp            |      | 400  | ns   |

| Port Input Setup Time                  | tpR            | 50   |      | ns   |

| Port Input Hold Time                   | tRP            | 50   |      | ns   |

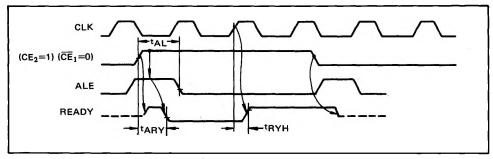

| READY Hold Time                        | tPYH           | 0    | 160  | ns   |

| Address to READY                       | tARY           |      | 160  | ns   |

| Recovery Time between Controls         | tRV            | 300  |      | ns   |

| Data Out Delay from READ Control       | tRDE           | 10   |      | ns   |

| ALE to Data Out Valid                  | tLD            |      | 350  | ns   |

Note: Timing is measured at V  $_L$  = 0.8 V and V  $_H$  = 2.2 V for both input and output Load condition:  $C_L$  = 150 pF

Fig. 1 Clock Signal for MSM83C55

Fig. 2 Timing for ROM Reading and for I/O Reading and Writing

Fig. 3 I/O Port Timing

Fig. 4 Wait State Timing (READY = 0)

# PIN DESCRIPTION

| Pin symbol | Function                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RESET      | When this signal becomes high level, ports A and B becomes the input mode.                                                                                                                                                                                                                                              |  |  |  |  |

| ALE        | This pin is used to fetch the AD 0~7, A 8~10, $IO/\overline{M}$ , $\overline{CE1}$ , and CE2 signals to their respective latch circuits at the fall of the ALE (Address Latch Enable) signal.                                                                                                                           |  |  |  |  |

| CE1, CE2   | When CE1 fetched to the latch circuit is high level or CE2 is low level, no read nor write operation is performed. The AD 0~7 and READY output signals are made into the floating status.                                                                                                                               |  |  |  |  |

| AD0~7      | Three-stake bidirectional address/data bus. This bus fetch 8-bit address information to the latch circuit upon the fall of the ALE signal. When CE1 in holding is low level and yet CE2 is high level, data is output from chip to bus if RD or IOR is low level and it i fetched from bus to chip if IOW is low level. |  |  |  |  |

| A8~10      | These are high order bits of ROM address and have no relation to I/O operation.                                                                                                                                                                                                                                         |  |  |  |  |

| 10/M       | When RD is low level, this pin selects I/O port if the IO/M in holding is high level or ROM if it is low level.                                                                                                                                                                                                         |  |  |  |  |

| RD         | If the $\overline{RD}$ is low level, the memory data is output to AD 0~7 when the ROM cycle is selected, but the selected port data is output to the same when the I/O cycle is selected                                                                                                                                |  |  |  |  |

| ĪŌR        | The port data selected at low level is output to AD 0~7. When turned to the low level, the IOR becomes the same function as that when IO/M is turned to the high level and RD to the low level. When both RD and IOR become high level, the output of AD 0~7 is made into the floating state.                           |  |  |  |  |

| ΙΟW        | At the low level, the AD 0~7 data is written to the selected port.                                                                                                                                                                                                                                                      |  |  |  |  |

| CLK        | This signal is used to generate the READY signal for the generation of 1 wait cycle built in 83C55.                                                                                                                                                                                                                     |  |  |  |  |

| READY      | This signal becomes low level when the ALE is high level and the $\overline{\text{CE1}}$ and CE2 are active. It becomes high level at the rise of CLK after the fall of the ALE.                                                                                                                                        |  |  |  |  |

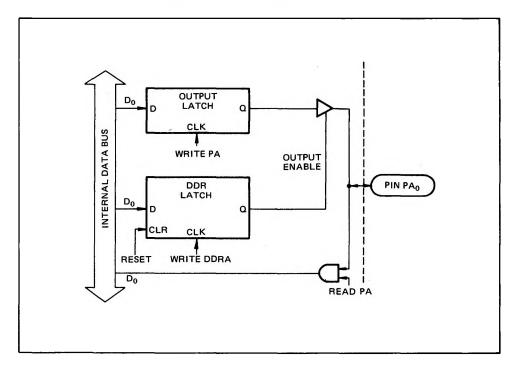

| PA0~7      | These are universal I/O pins and the input/output is determined by the content of the direction register. When writing data to port A, make the chip enable active and turn to IOW to low level after selecting AD 0, 1 to 0, 0. When reading it, turn the IOR to low level instead of IOW and IO/M to high level.      |  |  |  |  |

| PB0~7      | Same as the operation of PAO~7, excepting that ADO is selected to 1 and AD1 to 0.                                                                                                                                                                                                                                       |  |  |  |  |

| Vcc        | +5 V power supply                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| GND        | 0 V                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

## **OPERATIONAL DESCRIPTION**

#### **ROM Block**

The ROM block in the chip is specified in address by the chip enable and 11-bit address. Upon the fall of the ALE signal, the address and chip enable are fetched in the address latch circuit. When the chip enable is active and  $10/\bar{M}$  is low level, 8-bit content of ROM at the address held in the address latch circuit is transmitted to the bus through the output buffer of AD  $0\sim7$  upon the fall of the  $\overline{RD}$ .

#### I/O Block

The I/O block in the chip is specified in address by the value of 2-bits of AD 0~1 and chip enable. Two 8-bit data direction registers (DDR) built in MSM83C55 are used to turn corresponding individual port pins to the input mode or output mode. It becomes the input mode when set to 0 and the output mode when set to 1. It is impossible to read the DDR from outside, however.

| AD <sub>1</sub> | AD <sub>0</sub> | Selection                             |

|-----------------|-----------------|---------------------------------------|

| 0               | 0               | Port A                                |

| 0               | 1               | Port B                                |

| 1               | 0               | Port A data direction register (DDRA) |

| 1               | 1               | Port B data direction register (DDRB) |

Upon the fall of  $\overline{IOW}$  when the chip enable is active, the AD 0~7 data is written to the I/O port to be determined by the value of AD 0~1 in holding. During this operation, selected side I/O bits are all subject to its influence irrespective of the I/O status and IO/M status. The output level remains unchanged until the  $\overline{IOW}$  returns to high level. The data can be read from ports when the chip enable in holding is active and IO/M is high level and yet the  $\overline{RD}$  or  $\overline{IOR}$  signal falls. In both input and output, the data on the selected side exists on the line of AD 0~7. The function of I/O ports and DDR (data direction register) is shown in the block diagram below:

Writing "0" to the DDR is equivalent to the RESET operation when the port output is made into the High impedance status and the input mode is specified. Note that the data can be written to the ports even if the

output pin was already in the high impedance status (input mode) by the DDR. Likewise, it is also possible to read the data once set to those ports.