19-3126; Rev 0; 4/91

## High-Speed 12-Bit A/D Converters With External Reference Input

#### **General Description**

The MX7672 is a 12-bit, high-speed, BiCMOS, analog-todigital converter (ADC) that performs conversions in as little as  $3\mu$ s while consuming only 110mW of power. The MX7672 is a plug-in replacement for AD7672.

The MX7672 requires an external -5V reference. A buffered reference input minimizes reference current requirements and allows a single reference to drive several ADCs. External reference specifications can be chosen to suit the accuracy of the application. The ADC clock can be driven from either a crystal or an external clock source, such as a microprocessor (µP) clock.

Analog input range is pin-selectable for 0 to +5V, 0 to +10V, or ±5V, making the ADC ideal for data-acquisition and analog input/output cards. A high-speed digital interface (125ns data-access time) with three-state data outputs is compatible with most µPs.

#### Applications

Telecommunications Sonar and Radar Signal Processing High-Speed Data-Acquisition Systems Personal Computer I/O Boards

#### **Features**

**MX7672**

- Plug-In Replacement for AD7672

- ♦ 12-Bit Resolution and Accuracy

- ♦ Fast Conversion Times:

- MX7672\_\_\_03 3μs MX7672\_\_\_05 5μs MX7672\_\_\_10 -10μs

- ♦ Operates with +5V and -12V Supplies

- Buffered Reference Input

- ♦ Low 110mW Power Consumption

- ♦ Choice of +5V, +10V or ±5V Input Ranges

- ♦ Fast 125ns Bus-Access Time

#### **Ordering Information**

TEMP. RANGE PIN-PACKAGE LINEARITY (LSBs) PART 3µs Maximum Conversion Time MX7672KN03 0°C to +70°C 24 Plastic DIP ±1 MX7672KP03 0°C to +70°C 28 PLCC<sup>†</sup> ±1 MX7672BE03 -40°C to +85°C 28 LCC<sup>†</sup> ±1 MX7672BQ03 -40°C to +85°C 24 CERDIP ±1

Ordering information continued on last page + Contact factory for availability.

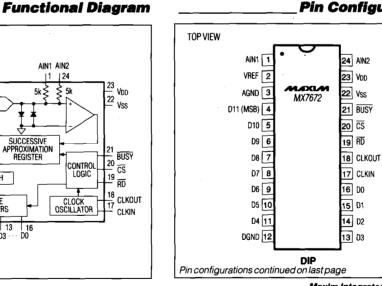

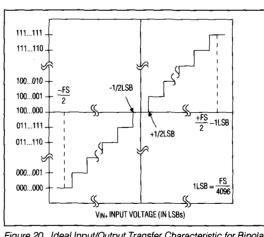

#### **Pin Configurations**

## **ABSOLUTE MAXIMUM RATINGS MX7672**

| ABSOLUTE MAAIMUM NATIN         |                    |

|--------------------------------|--------------------|

| Vpp to DGND                    | 0.3V to +7V        |

| Vss to DGND                    | +0.3V to -17V      |

| AGND to DGND                   | -0.3V to VDD+0.3V  |

| AIN1, AIN2 to AGND             | 15V to +15V        |

| VREF to AGND Vs                | s-0.3V to VDD+0.3V |

| Digital Input Voltage to DGND  |                    |

| (CLKIN, CS, RD)                | -0.3V to VDD+0.3V  |

| Digital Output Voltage to DGND |                    |

| (D11-D0, BUSY, CLKOUT)         | -0.3V to VDD+0.3V  |

|                                |                    |

| 7V | Continuous Power Dissipation (any package) |

|----|--------------------------------------------|

| 7V | to +75°C                                   |

| 3V | derate above +75°C by 10mW/°C              |

| 5V | Operating Temperature Ranges:              |

| 3V | MX7672K_/L0°C to +70°C                     |

|    | MX7672B_ /C                                |

| 3V | MX7672T_ /U                                |

|    | Storage Temperature Range                  |

| 3V | Lead Temperature (soldering, 10 sec)       |

|    |                                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**ELECTRICAL CHARACTERISTICS** (VDD =  $+5V \pm 5\%$ , Vss =  $-12V \pm 10\%$ ; VHEF = -5V; Slow-Memory Mode; fcLK = 4MHz for MX7672\_\_03, fcLK = 2.5MHz for MX7672\_\_05, fcLK = 1.25MHz for MX7672\_\_10; TA = TMIN to TMAX, unless otherwise noted.)

| PARAMETER                             | PARAMETER SYMBOL CONDITIONS |                                                                  |                                 |       |  | MAX   | UNITS |  |

|---------------------------------------|-----------------------------|------------------------------------------------------------------|---------------------------------|-------|--|-------|-------|--|

| ACCURACY (Note 1)                     |                             |                                                                  |                                 |       |  |       |       |  |

| Resolution                            | N                           |                                                                  |                                 | 12    |  |       | Bits  |  |

|                                       |                             |                                                                  | MX7672C/L                       |       |  | ±1/2  |       |  |

| Laborated bits and the second second  | 15.0                        | Tested range ±5V                                                 | MX7672U, T <sub>A</sub> = +25°C |       |  | ±1/2  | LSB   |  |

| Integral Nonlinearity                 | INL                         |                                                                  | MX7672U                         |       |  | ±3/4  |       |  |

|                                       |                             |                                                                  | MX7672B/K/T                     |       |  | ±1    |       |  |

| Differential Nonlinearity             | DNL                         | 12 bits, no missing c                                            | codes over temp.                |       |  | ±0.9  | LSB   |  |

|                                       |                             | MX7672C/L/U                                                      | T <sub>A</sub> = +25°C          |       |  | ±3    |       |  |

|                                       |                             | WIX/6/2C/L/U                                                     | $T_A = T_{MIN}$ to $T_{MAX}$    |       |  | ±4    | LSB   |  |

| Unipolar Offset Error                 |                             | МХ7672В/К/Т                                                      | T <sub>A</sub> = +25°C          |       |  | ±5    | LSD   |  |

|                                       |                             | WIX/0/2D/N/1                                                     | $T_A = T_{MIN}$ to $T_{MAX}$    |       |  | ±6    |       |  |

|                                       |                             | MX7672C/L/U                                                      | T <sub>A</sub> = +25°C          |       |  | ±4    | LSB   |  |

| Unipolar Gain Error                   |                             | WIX70720/L/0                                                     | TA = TMIN to TMAX               |       |  | ±6    |       |  |

| Unipolar Gain Eiror                   |                             | MX7672B/K/T                                                      | T <sub>A</sub> = +25°C          |       |  | ±5    |       |  |

|                                       |                             | WIX7072B/R/T                                                     | $T_A = T_{MIN}$ to $T_{MAX}$    |       |  | ±7    |       |  |

|                                       |                             | MX7672C/L/U<br>MX7672B/K/T                                       | T <sub>A</sub> = +25°C          |       |  | ±3    | LSB   |  |

| Bipolar Zero Error                    |                             |                                                                  | $T_A = T_{MIN}$ to $T_{MAX}$    |       |  | ±4    |       |  |

| BIDOIAI ZEIO EITOI                    |                             |                                                                  | T <sub>A</sub> = +25°C          |       |  | ±5    |       |  |

|                                       |                             |                                                                  | $T_A = T_{MIN}$ to $T_{MAX}$    |       |  | ±6    |       |  |

|                                       |                             | MX7672C/L/U                                                      | T <sub>A</sub> = +25°C          |       |  | ±4    |       |  |

| Bipolar Gain Error                    |                             | WIX70720/L/0                                                     | $T_A = T_{MIN}$ to $T_{MAX}$    |       |  | ±6    | LSB   |  |

| Bipolar Gain Error                    |                             | MX7672B/K/T                                                      | TA = +25°C                      |       |  | ±5    | LSB   |  |

|                                       |                             | WIA/0/20/N/1                                                     | $T_A = T_{MIN}$ to $T_{MAX}$    |       |  | ±7    |       |  |

|                                       |                             |                                                                  | MX767203                        |       |  | 3.125 |       |  |

|                                       |                             | Synchronous Clk<br>(12.5 clks)                                   | MX767205                        |       |  | 5     |       |  |

| Conversion Time                       | TCONV                       | (12.0 0 0 0)                                                     | MX767210                        |       |  | 10    | ]     |  |

| Conversion nime                       | CONV                        |                                                                  | MX767203                        | 3.0   |  | 3.25  | μs    |  |

|                                       |                             | Asynchronous Clk<br>(12 to 13 clks)                              | MX767205                        | 4.8   |  | 5.2   |       |  |

|                                       |                             |                                                                  | MX767210                        | 9.6   |  | 10.4  |       |  |

| ANALOG AND REFERENC                   | E INPUTS                    |                                                                  |                                 |       |  |       |       |  |

| Analog Input Current,<br>AIN1 or AIN2 |                             | Unipolar input ranges 0V to +5V, 0V to +10V<br>Bipolar range ±5V |                                 |       |  | 3.5   | mA    |  |

|                                       |                             |                                                                  |                                 |       |  | ±1.75 |       |  |

| VREF Input Range (Note 2)             |                             |                                                                  |                                 | -5.05 |  | -4.95 | V     |  |

| VREF Input Current                    |                             |                                                                  |                                 |       |  | ±3    | μA    |  |

ELECTRICAL CHARACTERISTICS (continued) (VDD = +5V ±5%, VSS = -12V ±10%; VREF = -5V; Slow-Memory Mode; fcLk = 4MHz for MX7672\_\_03, fcLk = 2.5MHz for MX7672\_\_05, fcLk = 1.25MHz for MX7672\_\_10; TA = TMIN to TMAX, unless otherwise noted.

| PARAMETER                                  | SYMBOL | CONDITIONS                                                          | MIN   | TYP  | MAX             | UNITS |  |

|--------------------------------------------|--------|---------------------------------------------------------------------|-------|------|-----------------|-------|--|

| LOGIC                                      |        |                                                                     |       |      |                 |       |  |

| Input Low Voltage                          | VINL   | CS, RD, CLKIN                                                       |       |      | 0.8             | V     |  |

| Input High Voltage                         | VINH   | CS, RD, CLKIN                                                       | 2.4   |      |                 | V     |  |

| leave Current                              |        | $\overline{CS}$ , $\overline{RD}$ ; $V_{IN} = 0$ to $V_{DD}$        |       |      | ±10             |       |  |

| Input Current                              | lin    | CLKIN; VIN = 0 to VDD                                               |       |      | ±20             | μΑ    |  |

| Input Capacitance (Note 2)                 | CIN    |                                                                     |       |      | 10              | pF    |  |

| Output Low Voltage                         | VoL    | D11-D0, BUSY, CLKOUT; ISINK = 1.6mA                                 |       |      | 0.4             | V     |  |

| Output High Voltage                        | Voн    | D11-D0, BUSY, CLKOUT; ISOURCE = 200µA                               | 4.0   |      |                 | V     |  |

| Floating State Leakage Current             | ILKG   | D11-D0; $V_{OUT} = 0V$ to $V_{DD}$                                  |       |      | ±10             | μΑ    |  |

| Floating State Output Capacitance (Note 2) | Соит   |                                                                     |       |      | 15              | pF    |  |

| POWER REQUIREMENTS                         |        |                                                                     |       |      |                 |       |  |

| Suzzki Voltana                             | VDD    |                                                                     | 4.75  | 5    | 5.25            | v     |  |

| Supply Voltage                             | Vss    |                                                                     | -13.2 | -12  | -10.8           | •     |  |

|                                            | IDD    | $\overline{CS} = \overline{RD} = V_{DD}$ , AIN1 = AIN2 = 5V,        |       |      | 7               |       |  |

| Supply Current                             | Iss    | BUSY = HIGH                                                         |       |      | -12             | - mA  |  |

| Power Dissipation                          | PD     | $V_{DD} = 5V, V_{SS} = -12V$                                        |       | 110  | 17 <del>9</del> | mW    |  |

| Power-Supply Rejection, VDD Only           |        | FS Change, V <sub>SS</sub> = -12V, V <sub>DD</sub> = 4.75V to 5.25V |       | ±1/4 | ±2              | LSB   |  |

| Power-Supply Rejection, Vss Only           |        | FS Change, VDD = 5V, VSS = -10.8V to -13.2V                         |       | ±1/2 | ±1              | LSB   |  |

TIMING CHARACTERISTICS (VDD = +5V, VSS = -12V; 100% production tested, unless otherwise indicated.) (Note 3, Figures 7, 9, 10)

| PARAMETER                                   | SYMBOL | CONDITIONS |     | a = +25<br>_ GRAI | _   |     | T <sub>MIN</sub> to T <sub>MAX</sub><br>672K/L/B/C |     | Г <sub>МІN</sub> to Т <sub>МАХ</sub><br>(7672Т/U | UNITS |

|---------------------------------------------|--------|------------|-----|-------------------|-----|-----|----------------------------------------------------|-----|--------------------------------------------------|-------|

|                                             |        |            | MIN | TYP               | MAX | MIN | TYP MAX                                            | MIN | TYP MA)                                          | K     |

| CS to RD Setup Time (Note 2)                | t1.    |            | 0   |                   |     | 0   |                                                    | 0   |                                                  | ns    |

| RD to BUSY Delay                            | t2     | CL = 50pF  |     | 70                | 190 |     | 230                                                |     | 270                                              | ns    |

| Data-Access Time (Note 4)                   | t3     | CL = 100pF |     | 50                | 125 |     | 150                                                |     | 170                                              | ns    |

| RD Pulse Width (Note 2)                     | t4     |            | t3  |                   |     | t3  |                                                    | t3  |                                                  | ns    |

| CS to RD Hold Time (Note 2)                 | t5     |            | 0   |                   |     | 0   |                                                    | 0   |                                                  | ns    |

| Data-Setup Time After BUSY<br>(Note 4)      | t6     | CL = 100pF |     | 40                | 70  |     | 90                                                 |     | 100                                              | ns    |

| Bus-Relinquish Time (Note 5)                | t7     |            |     | 30                | 75  |     | 85                                                 |     | 90                                               | ns    |

| Delay Between Read<br>Operations            | t8     |            | 200 |                   |     | 200 |                                                    | 200 |                                                  | ns    |

| CLKIN to BUSY Delay (Note 2)                | t9     |            |     |                   | 120 |     | 150                                                |     | 180                                              | ns    |

| RD to CLKIN Setup/Hold Time<br>(Notes 2, 6) | t10    |            | 25  |                   | 100 | 25  | 100                                                | 25  | 100                                              | ns    |

Note 1: V<sub>DD</sub> = +5V, V<sub>SS</sub> = -12V, 1LSB = FS/4096. Performance over power-supply tolerance is guaranteed by power-supply rejection test.

Note 2: Guaranteed by design.

Note 3: All inputs are 0V to +5V swing with tr = tf = 5ns (10% to 90% of +5V) and timed from a voltage level of +1.6V.

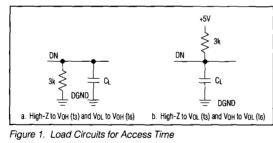

Note 4: t3 and t6 are measured with the load circuits of Figure 1 and defined as the time required for an output to cross +0.8V or +2.4V.

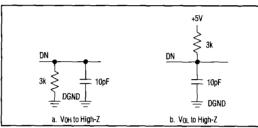

Note 5: t7 is defined as the time required for the data lines to change 0.5V when loaded with the circuit of Figure 2.

Note 6: For predictable conversion times, RD to CLKIN falling edge must be outside this window. If t10 < 25ns, conversion will skip first falling CLKIN edge and start on second falling CLKIN edge. If t10 > 100ns, conversion will start on first falling CLKIN edge.

**MX7672**

**MX7672**

| Pin | Descri | iption |

|-----|--------|--------|

| 24-PIN | 28-P1N    | NAME   | FUNCTION                                                                                                                                                        |

|--------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1,8,15,22 |        | No Connect                                                                                                                                                      |

| 1      | 2         | AIN1   | Analog Input                                                                                                                                                    |

| 2      | 3         | VREF   | Voltage-Reference Input                                                                                                                                         |

| 3      | 4         | AGND   | Analog Ground                                                                                                                                                   |

| 4-11   | 5-13      | D11-D4 | Three-State Data Outputs. They are active when CS and RD are low. D11 is the most significant bit.                                                              |

| 12     | 14        | DGND   | Digital Ground                                                                                                                                                  |

| 13-16  | 16-19     | D3-D0  | Three-State Data Outputs                                                                                                                                        |

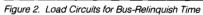

| 17     | 20        | CLKIN  | Clock Input. Connect an exter-<br>nal TTL- compatible clock to<br>CLKIN. Alternatively, insert a<br>crystal or ceramic resonator be-<br>tween CLKIN and CLKOUT. |

| 18     | 21        | CLKOUT | Clock Output. When using an ex-<br>ternal clock, an inverted CLKIN<br>signal appears on CLKOUT. See<br>CLKIN description.                                       |

| 19     | 23        | RD     | READ Input. Along with CS, this active low signal enables the three-state drivers and starts a conversion.                                                      |

| 20     | 24        | ĊS     | CHIP SELECT. Along with RD,<br>this active low signal enables the<br>three-state drivers and starts a<br>conversion.                                            |

| 21     | 25        | BUSY   | BUSY. Low while a conversion is<br>in progress. BUSY indicates con-<br>verter status.                                                                           |

| 22     | 26        | Vss    | Negative Supply, -12V                                                                                                                                           |

| 23     | 27        | VDD    | Positive Supply, +5V                                                                                                                                            |

| 24     | 28        | AIN2   | Analog Input                                                                                                                                                    |

4

#### **Detailed Description**

#### **Converter Operation**

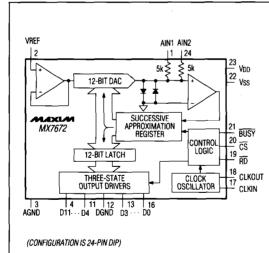

The MX7672 uses a successive approximation technique to convert an analog input to a 12-bit digital output code. The control logic provides easy interface to most  $\mu$ Ps (Figure 3).

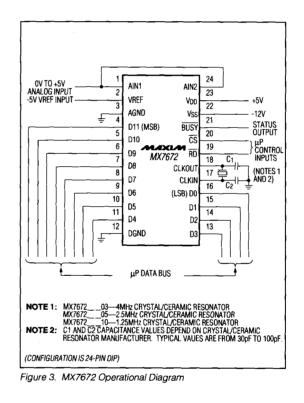

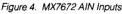

Figure 4 shows the MX7672 analog-equivalent circuit. The internal D/A converter (DAC) is controlled by a successive approximation register (SAR), has an output impedance of  $2.5 k\Omega$ , and connects directly to the comparator input. The analog inputs AIN1 and AIN2 connect to the same comparator input through  $5 k\Omega$  resistors.

A conversion starts at the falling edge of  $\overline{CS}$  and  $\overline{RD}$  and cannot be restarted after initiation. The BUSY output goes low when the conversion starts and can be used to control an external sample-and-hold when measuring wide bandwidth input signals.

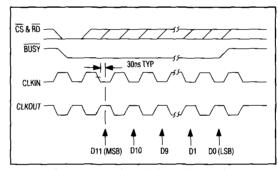

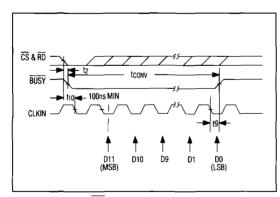

The SAR is set, asynchronously with the clock input, to half scale when  $\overline{CS}$  and  $\overline{RD}$  go low. At the second falling edge of CLKIN (or rising edge of CLKOUT) following a conversion start, the output of the comparator is latched into the SAR most significant bit (MSB/D11) (Figure 5). The MSB is kept if the analog input is greater than half scale or dropped if it is smaller. The next bit (D10) is then set with the DAC output either at 1/4 scale (if the MSB was dropped) or 3/4 scale (if the MSB was kept). The conversion continues in this manner until the LSB is tried. At conversion end, following a falling CLKIN signal, BUSY goes high and the SAR result is latched into three-state output buffers.

## \_\_\_\_ Clock

#### Internal Clock Oscillator

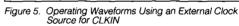

Figure 6 shows the MX7672 clock circuitry. Minimize the capacitive load on the CLKOUT pin for low power dissipation and to avoid digital coupling of the CLKOUT buffer current to the comparator. CLKOUT should be left open if an external clock source is used to drive CLKIN. Connect a crystal/ceramic resonator between CLKOUT and CLKIN if the internal oscillator is used.

#### Control Inputs Synchronization

When  $\overline{\text{RD}}$  is not synchronized with the ADC clock, the conversion time can vary from 12 to 13 clock cycles. The SAR changes state on the falling edge of the CLKIN input (or rising edge on the CLKOUT pin). Use the following guidelines to ensure a fixed conversion time: The MAX7672 RD input should go low at the rising edge of CLKIN. In this case, the conversion lasts 12.5 clock cycles,

Figure 6. MX7672 Internal Clock Circuit

MX7672

and the conversion time is  $3.125\mu$ s when  $f_{CLK} = 4MHz$ , 5 $\mu$ s when  $f_{CLK} = 2.5MHz$ , and 10 $\mu$ s when  $f_{CLK} = 1.25MHz$ . The delay from the falling edge of RD to the falling edge of CLKIN must not be less than 100ns to ensure the 12.5 clock cycle conversion time (Figure 7). This gives the external sample-and-hold 1.5 clock cycles to settle from hold transients. An additional 1/2 clock cycle of settling can be allowed for the sample-and-hold by having RD go low at the falling edge of CLKIN. This results in a 13-cycle conversion time (3.25µs, 5.2µs, and 10.4µs).

**WX7672**

#### **Digital Interface**

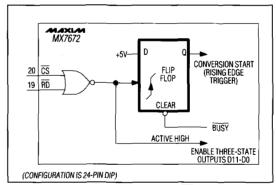

**Timing and Control**

CS and RD control conversion start and data-read operations. Figure 8 shows the logic equivalent for the conversion and the data-output control circuitry. A logic low at both inputs starts a conversion. Once a conversion is in progress, it cannot be restarted. The BUSY output remains low during the entire conversion cycle.

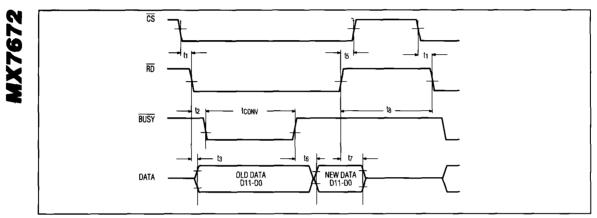

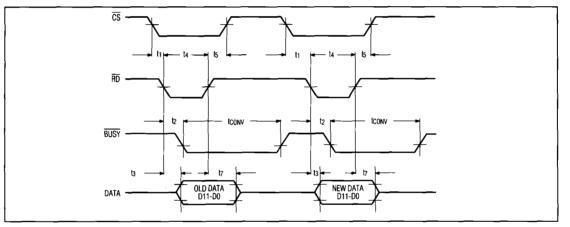

Figures 9 and 10 outline the two interface modes (slow memory and ROM). Slow-memory mode is for  $\mu$ Ps that can be forced into a wait state for periods as long as the MX7672 conversion time. ROM mode is for  $\mu$ Ps that cannot be forced into a wait state. In both interface modes, a processor read operation to the ADC address starts the conversion. In the ROM mode, a second read operation accesses the conversion result.

#### Slow-Memory Mode

The timing diagram in Figure 9 illustrates slow- memory mode, which is designed for  $\mu$ Ps with a wait state. CS and RD go low, triggering a conversion, and are kept low until the conversion is complete. BUSY responds by going low, and data from the previous conversion remains on the three-state data outputs. At conversion end, BUSY returns high, and the output latches transfer the new conversion results to the three-state data outputs. The  $\mu$ P completes the read operation by taking  $\overline{CS}$ and RD high.

#### **ROM Mode**

The ROM mode avoids placing the  $\mu P$  into a wait state. <u>A conversion begins with a read operation</u>. While  $\overline{CS}$  and RD are low, data from the last conversion is available on the data outputs. A second read operation reads the new data and begins the conversion process again. A delay at least as long as the MX7672 conversion time must be allowed between read operations. The data on the output bus is in a parallel format in either mode

#### **Application Hints Digital Bus Noise**

If the data bus connected to the ADC is active during a conversion, coupling from the data pins to the ADC comparator may cause LSBs of error. Using slowmemory mode avoids this problem by placing the  $\mu P$ into a wait state during the conversion. In ROM mode, if the data bus is active during the conversion, use three-state drivers to isolate the bus from the ADC.

Figure 7. MX7672 RD and CLKIN for Synchronous Operation and conversion time of 12.5 clock cycles

Figure 8. Logic for Control Inputs CS and RD Internal

#### **ROM Mode**

Digital noise is generated in the ADC when  $\overline{RD}$  or  $\overline{CS}$  go high, and the output data drivers are disabled after a conversion is started. This noise will feed into the ADC comparator and cause large errors if it coincides with the time the SAR is latching a bit decision. To avoid this problem,  $\overline{RD}$  and  $\overline{CS}$  should be active for less than one clock cycle. In other words, the  $\overline{RD}$  and  $\overline{CS}$  low pulse should be less than 250ns for the MX7672\_\_03, 400ns for the MX7672\_\_05, and 1us for the MX7672\_\_10. If this cannot be done, the  $\overline{RD}$  or  $\overline{CS}$  signal must go high at a rising edge of CLKIN, since the comparator output is always latched at falling edges of CLKIN.

#### **Physical Layout**

For best system performance, printed circuit boards should be used for the MX7672; wire-wrap boards are not recommended. Separate the digital-analog-signal lines as much as possible in the board layout. Do not run analog and digital lines parallel to each other or digital lines underneath the MX7672 package.

#### Grounding

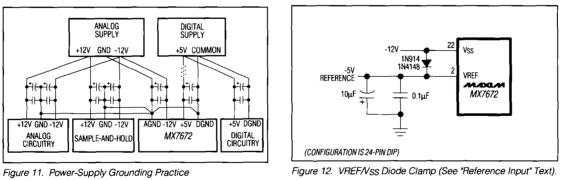

Figure 11 shows the recommended system ground connections. Establish a single-point analog ground (star ground), separate from the logic ground, at AGND of the MX7672. Connect all other analog grounds and DGND of the MX7672 to this star ground (no other digital grounds should be connected to this point). For noise-free operation of the ADC, use a low-impedance ground return to the power supply from this star ground.

#### **Power-Supply Bypassing**

The ADC's high-speed comparator is sensitive to high-frequency noise in the VDD and Vss power supplies. These supplies should be bypassed to the analog star ground with  $0.1\mu$ F and  $10\mu$ F bypass capacitors with minimum lead length for supply noise rejection. If the +5V power supply is very noisy, a small ( $10\Omega$ - $20\Omega$ ) resistor can be connected (Figure 11) to filter external noise.

#### **Driving The Analog Input**

The input signal leads to AIN and the input return leads to AGND should be as short as possible to minimize input noise coupling. Use shielded cables if the leads must be long.

The input impedance at each AIN is typically  $5k\Omega$ . The amplifier driving AIN must have low enough DC output impedance for low gain error. Furthermore, low AC output impedance is needed, since the analog input current is modulated at the clock rate during a conversion (up to 4MHz for MX7672\_\_\_03, 2.5MHz for MX7672\_\_\_05, or 1.25MHz for the MX7672\_\_\_10). The output impedance of the driving amplifier is equal to its open-loop output

impedance divided by the loop gain at the frequency of interest.

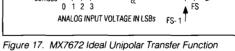

**MX7672\_\_\_05/10** – The MX7672\_\_\_05/10 maximum clock rate of 2.5MHz makes it possible to drive AIN with amplifiers like the OP42, AD711 or a Maxim OP27. A MAX400 or a Maxim OP07 can also be used up to 1.25MHz clock rate.

**MX7672** \_\_\_03 – The MX7672\_\_\_03, with a maximum 4MHz clock rate, might exhibit settling problems with the above amplifiers. An LF356, LF400 or LT1056 can be used to drive the input. Alternatively, an emitter follower buffer inside the feedback loop of a Maxim OP27, an OP42, or an AD711 improves high-frequency output impedance.

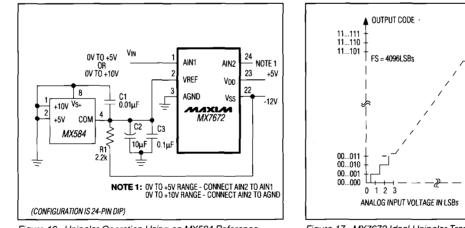

#### **Reference Input**

VREF connects to an external -5V source. This may be either a precision negative reference, a positive reference (such as the MX584) connected as a two-terminal device to provide -5V (Figure 16), or an existing system reference. The allowed input range at REFIN is -5.1V to -4.9V. VREF (and AIN2 in bipolar input operation) should be bypassed to ground with a  $10\mu$ F electrolytic capacitor in parallel with a  $0.1\mu$ F ceramic capacitor.

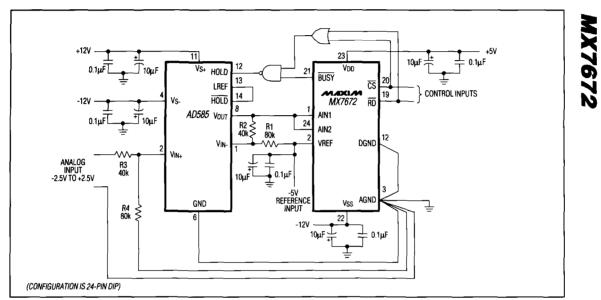

If the external reference is biased from a power supply other than VSS, care must be taken to ensure that VSS is applied to the ADC before VREF. If supply sequencing is uncertain, connect a diode between VSS and VREF, as shown in Figure 12. No diode is needed if the reference source is powered from the same supply as VSS.

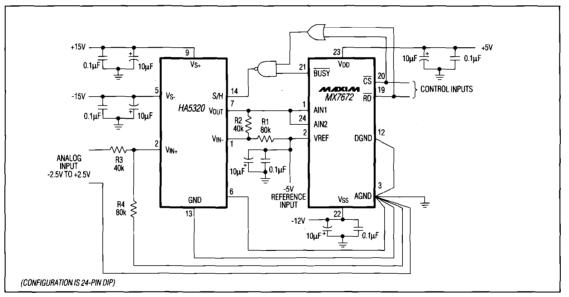

#### MX7672 to Sample-and-Hold Interface

The analog input to the ADC must be stable to within 1/2LSB during the entire conversion for specified 12-bit accuracy. This limits the input-signal bandwidth to less than 6Hz for sinusoidal inputs, even when using the faster MX7672\_\_\_03. A sample-and-hold should be used for higher bandwidth signals.

The BUSY output from the MX7672 may be used to provide the TRACK/HOLD signal to the sampleand-hold amplifier. However, since the ADC's DAC is switched at approximately the same time as the BUSY signal goes low, sample-and-hold transients caused by DAC switching may result in code-dependent errors due to sample-and-hold aperture delay. Adding a NAND (inverted AND) gate ensures that the sample-and-hold is switched to the hold mode BEFORE any disturbances occur (Figures 13 and 14). The NAND gate solution works only if the width of the RD pulse is wider than the RD to BUSY delay in the MX7672. If this is not the case, use a flip-flop, which is set by the falling edge of RD and reset by the rising edge of BUSY. MX7

Figure 9. Slow-Memory Mode Timing Diagram

Figure 10. ROM-Mode Timing Diagram

8

Figure 12. VREF/Vss Diode Clamp (See "Reference Input" Text).

ΜΙΧΙΜ

Figure 13. MX7672—AD585 Sample-and-Hold Interface

9

Figure 14. MX7672-HA5320 Sample-and-Hold Interface

For synchronous RD and CLKIN, the hold settling time **MX7672** allowed for the sample-and-hold is 375ns (MX76762\_\_\_ 03), 600ns (MX7672\_\_05), and 1.5µs (MX7672\_\_10).

The maximum sampling rate is 125kHz with a 2.5MHz clock and 64.5kHz with a 1MHz clock, allowing for a  $3\mu$ s sample-and-hold acquisition time.

Although this circuit works well for the 1MHz clock rate, a faster sample-and-hold amplifier, such as the HA5320, is recommended at a 2.5MHz clock rate.

MX7672\_\_03 - Figure 14 is the MX7672\_\_03 to HA5320 interface. The maximum sampling rate is 210kHz with a 4MHz clock, which allows a 1.5µs acquisition time. The HA5320 can also be replaced by a HA5330 for higher throughput.

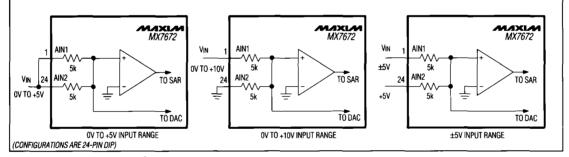

#### **Analog Input Ranges**

The MX7672 provides three selectable analog input ranges: 0V to +5V, 0V to +10V, and ±5V. Figure 15 shows the, configuration for the two analog inputs (AIN1 and AIN2) for these ranges.

#### **Unipolar Operation**

Figure 16 shows unipolar operation using an MX584 voltage reference configured for -5V.

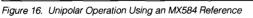

Figure 17 shows the nominal input/output transfer function of the MX7672. Code transitions occur halfway between successive integer LSB values. The output coding is binary with 1LSB = Full Scale (FS)/4096. FS is either +5V or +10V, based on the analog input configurations.

#### **Offset and Full-Scale Adjustment**

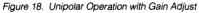

In applications requiring offset and FS range adjustment, use the circuit in Figure 18. Note: The amplifier shown could also be a sample-and-hold. Offset should be adjusted first. Apply 1/2LSB (0.61mV) at the analog input (AIN1 or AIN2) and adjust the offset of the amplifier until

Figure 15. Analog Input Range Configurations

the digital output code changes between 0000 0000 0000 and 0000 0000 0001.

0V to +5V range: 1/2LSB = 0.61mV

0V to +10V range: 1/2LSB = 1.22mV

To adjust the full-scale range, apply FS-3/2LSB (last code transition) at the analog input and adjust R1 until the output code switches between 1111 1111 1110 and 1111 1111 1111.

0V to +5V range: FS-3/2LSB = 4.99817V 0V to +10V range: FS-3/2LSB = 9.99634V

#### **Bipolar Operation**

The bipolar input range is  $\pm 5V$ . VIN is applied to AIN1, +5V to AIN2, and -5V to VREF. This requires two reference voltages: -5V for the VREF input and +5V for the AIN2 input. Figure 19 shows these reference voltages are produced from a MAX675 reference and a MAX400 op amp configured as an inverting amplifier.

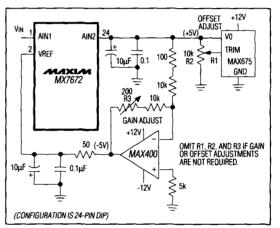

The ideal input/output transfer characteristic after offset and gain adjustment is shown in Figure 20. The LSB is 2.44mV (10V/4096).

The resistors used in bipolar applications should be the same type from the same manufacturer to obtain low temperature drifts. 0.1% resistors are recommended for applications where offset and full-scale adjustments must be made in bipolar circuits. If low tolerances are used, larger value potentiometers must be used, which results in poor trim resolution and higher temperature drift.

#### Offset and Gain Adjustment

In bipolar operation, the offset is trimmed at negative full scale and should always be adjusted first. For offset,

apply -FS/2 + 1/2LSB (-4.99878V) at VIN and adjust the 10k $\Omega$  potentiometer (Figure 18) until the output code switches between 0000 0000 0000 and 0000 0000 0001.

Gain is adjusted at full scale or bipolar zero. For full-scale adjustment, apply FS/2 - 3/2LSBs (4.99634V) to VIN and adjust the  $200\Omega$  potentiometer until the output code switches between 1111 1111 1110 and 1111 1111 1111.

# **MX7672**

Alternatively, to adjust gain at bipolar zero, apply -1.22mV at VIN and adjust the  $200\Omega$  potentiometer until the output code switches between 0111 1111 1111 and 1000 0000 0000.

Figure 19. Bipolar Operation with Offset and Gain-Error Adjust

Figure 20. Ideal Input/Output Transfer Characteristic for Bipolar Operation

| N |  |

|---|--|

| N |  |

| 9 |  |

| C |  |

| 2 |  |

| 2 |  |

| _ Ordering | Information ( | (continued) |

|------------|---------------|-------------|

|------------|---------------|-------------|

| PART                        | TEMP. RANGE     | PIN-PACKAGE           | LINEARITY<br>(LSBs) |  |  |  |  |  |

|-----------------------------|-----------------|-----------------------|---------------------|--|--|--|--|--|

| 5µs Maximum Conversion Time |                 |                       |                     |  |  |  |  |  |

| MX7672KN05                  | 0°C to +70°C    | 24 Plastic DIP        | ±1                  |  |  |  |  |  |

| MX7672LN05                  | 0°C to +70°C    | 24 Plastic DIP        | ±1/2                |  |  |  |  |  |

| MX7672KP05                  | 0°C to +70°C    | 28 PLCC <sup>†</sup>  | ±1                  |  |  |  |  |  |

| MX7672LP05                  | 0°C to +70°C    | 28 PLCC <sup>†</sup>  | ±1/2                |  |  |  |  |  |

| MX7672BQ05                  | -40°C to +85°C  | 24 CERDIP             | ±1                  |  |  |  |  |  |

| MX7672CQ05                  | -40°C to +85°C  | 24 CERDIP             | ±1/2                |  |  |  |  |  |

| MX7672TE05                  | -55°C to +125°C | 28 LCC <sup>† *</sup> | ±1                  |  |  |  |  |  |

| MX7672UE05                  | -55°C to +125°C | 28 LCC <sup>† *</sup> | ±3/4                |  |  |  |  |  |

| MX7672TQ05                  | -55°C to +125°C | 24 CERDIP*            | ±1                  |  |  |  |  |  |

| MX7672UQ05                  | -55°C to +125°C | 24 CERDIP*            | ±3/4                |  |  |  |  |  |

|                             | 10µs Maximum C  | onversion Time        |                     |  |  |  |  |  |

| MX7672KN10                  | 0°C to +70°C    | 24 Plastic DIP        | 1                   |  |  |  |  |  |

| MX7672LN10                  | 0°C to +70°C    | 24 Plastic DIP        | ±1/2                |  |  |  |  |  |

| MX7672KP10                  | 0°C to +70°C    | 28 PLCC <sup>†</sup>  | ±1                  |  |  |  |  |  |

| MX7672LP10                  | 0°C to +70°C    | 28 PLCC <sup>†</sup>  | ±1/2                |  |  |  |  |  |

| MX7672BQ10                  | -40°C to +85°C  | 24 CERDIP             | ±1                  |  |  |  |  |  |

| MX7672CQ10                  | -40°C to +85°C  | 24 CERDIP             | ±1/2                |  |  |  |  |  |

| MX7672TE10                  | -55°C to +125°C | 28 LCC <sup>†*</sup>  | ±1                  |  |  |  |  |  |

| MX7672UE10                  | -55°C to +125°C | 28 LCC <sup>† *</sup> | ±3/4                |  |  |  |  |  |

| MX7672TQ10                  | -55°C to +125°C | 24 CERDIP*            | ±1                  |  |  |  |  |  |

| MX7672UQ10                  | -55°C to +125°C | 24 CERDIP*            | ±3/4                |  |  |  |  |  |

Contact factory for availability.

Contact factory for processing to MIL-STD-883.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. 12 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-Z600

© 1991 Maxim Integrated Products