# Signetics

### Linear Products

### DESCRIPTION

The NE/SE5060 is a high-performance, monolithic sample-and-hold amplifier that features high accuracy, low droop rate, and fast acquisition times required in high-speed data acquisition systems.

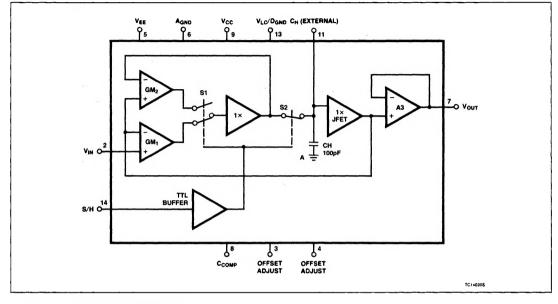

The circuit consists of two high impedance buffer amplifiers connected by an analog switch. In the sample mode, the device is in a non-inverting unity-gain configuration. The switch (S2) (see Block Diagram) is implemented as a unique switchable output stage of the input buffer which has been optimized for fast charging of the hold capacitor and a low sample-to-hold step size. In the hold mode, the input signal is effectively disconnected from the circuit by switch S1 to give a low feedthrough, and GM2 maintains 0V across the switch S2, ensuring a low droop rate. The device includes a 100pF hold capacitor. If lower droop rates and smaller sample-to-hold step error is desired at the expense of acquisition time, additional hold capacitance may be added externally. The voltage at the hold capacitor is buffered by the output buffer amplifier to drive the external load.

The device utilizes high voltage ionimplanted JFETs to obtain the low droop rates. The circuit has been designed to minimize the initial zero offset error. which is trimmed at the wafer level to be less than 0.5mV. The NE5060 operates from ±9V to ±17V power supplies with little or no change in the specification as long as the peak input voltage is not within 4V of the supplies.

# **NE/SE5060** Precision High-Speed Sample-and-Hold Amplifier

0.99970

0.5mV

1mV

0.2µV/µs

2.0µV/µs

150.0µV/µs

Preliminary Specification

### FEATURES

- Voltage gain

- Low signal non-linearity 0.0035%

- Low offset error Fast acquisition time

- 850ns

- Low sample-to-hold step 0.2µV/µs

- Low droop rate +25°C (SE/NE5060)

- +70°C (NE5060)

- + 125°C (SE5060)

- Internal 100pF hold capacitor

- TTL CMOS Logic compatible

- Functional equivalent replacement for HA2420, HA2425, HA5320, AD583 and SMP11

#### APPLICATIONS

- Precision data acquisition systems

- D/A converter deglitching

- Auto-zero circuits

- Peak detectors

#### ORDERING INFORMATION

| DESCRIPTION            | TEMPERATURE RANGE | ORDER CODE |

|------------------------|-------------------|------------|

| 14-Pin Hermetic Cerdip | 0 to +70°C        | NE5060F    |

| 14-Pin Hermetic Cerdip | -55°C to +125°C   | SE5060F    |

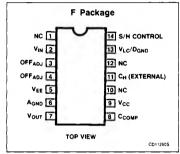

### PIN CONFIGURATION

**Preliminary Specification**

NE/SE5060

### **BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS

| SYMBOL           | PARAMETER                                                              | RATING                  | UNIT    |  |

|------------------|------------------------------------------------------------------------|-------------------------|---------|--|

|                  | Voltage between V <sub>CC</sub> and V <sub>EE</sub>                    | 36                      | v       |  |

| ViN              | Analog input voltage                                                   | ± 15                    | V       |  |

| V <sub>S/H</sub> | Logic input voltage                                                    | ± 15                    | V       |  |

| V <sub>LC</sub>  | Logic reference voltage                                                | ± 15                    | V       |  |

| Isc              | Output short-circuit duration                                          | Indefinite              |         |  |

|                  | Hold capacitor short-circuit duration                                  | 60                      | s       |  |

| PD               | Maximum power dissipation<br>$T_A = 25^{\circ}C \text{ (still-air)}^1$ | 1190                    | mW      |  |

| TA               | Operating temperature range NE5060<br>SE5060S <sup>2</sup>             | 0 to +70<br>-55 to +125 | °C<br>℃ |  |

| TSTG             | Storage temperature range                                              | -65 to +150             | °C      |  |

#### NOTES:

1. Derate above 25°C at 9.5mW/°C.

2. Operation above 110°C ambient requires that a heat sink be provided so as not to exceed the recommended maximum junction temperature of 150°C.

$\theta_{\rm JA} = 110^{\circ}{\rm C/W}$

$\theta_{\rm JC} = 30^{\circ}{\rm C/W}$

$T_J = V_{CC} \times I_{CC} \times 0.8 \times \theta_{JA}$ = 15 (15 + 14) × 0.8 × 110°C/W

= 38.2°C

# NE/SE5060

### DC ELECTRICAL CHARACTERISTICS Test conditions, unless otherwise noted:

$\begin{array}{lll} V_{CC}=15V; \; V_{EE}=-15V; \; -10V \leqslant V_{IN}\leqslant 10V; \; V_{LC}=0V; \; V_{S/H}<0.8V \; (for \; sample \; mode); \; V_{S/H}>2.0V \; (for \; hold \; mode); \; C_{H}=Internal; \; device \; in \; sample \; mode; \\ 0^{\circ}C\leqslant T_{A}\leqslant +70^{\circ}C \; (for \; NE5060; \; -55^{\circ}C \; \leqslant T_{A}\leqslant +125^{\circ}C \; for \; SE5060. \end{array}$

| SYMBOL           | PARAMETER                                  |                                                                            | NE5060      |                    |       | SE5060      |                    |       | -              |

|------------------|--------------------------------------------|----------------------------------------------------------------------------|-------------|--------------------|-------|-------------|--------------------|-------|----------------|

|                  |                                            | TEST CONDITIONS                                                            | Min         | Тур                | Max   | Min         | Тур                | Max   | UNIT           |

| Vzs              | Zero-scale error                           | $V_{IN} = 0V; T_A = 25^{\circ}C$<br>$T_{MIN} \text{ to } T_{MAX}$          |             | 0.5<br>1.0         | 2.0   |             | 0.5<br>3.0         | 4.0   | mV<br>mV       |

| BIAS             | Input bias current                         | V <sub>IN</sub> = 0V                                                       |             | 70                 | 150   |             | 70                 | 250   | nA             |

| R <sub>IN</sub>  | Input resistance                           |                                                                            | 150         | 250                |       | 100         | 250                |       | MΩ             |

| Av               | Voltage gain                               | $V_{IN} = \pm 10V$<br>$T_A = 25^{\circ}C$<br>$T_{MIN} \text{ to } T_{MAX}$ |             | 0.99975<br>0.99965 |       |             | 0.99975<br>0.99955 |       | v/v<br>v/v     |

| EL               | Linearity error                            | $V_{IN} = \pm 10V, R_L = 5k\Omega$                                         |             | 0.0035             | 0.007 |             | 0.0035             | 0.008 | %              |

| VINR             | Input voltage range                        |                                                                            | ± 10.5      | ±11                |       | ± 10.5      | ±11                |       | V              |

| R <sub>OUT</sub> | Output resistance                          |                                                                            |             | 0.15               | 0.5   |             | 0.15               | 0.5   | Ω              |

| ILOAD            | Output load current (@ $R_0 < 0.5\Omega$ ) | $V_{IN} = \pm 10V; T_A = 25^{\circ}C$<br>$T_{MIN}$ to $T_{MAX}$            | ± 10<br>± 8 | ± 15<br>± 11       |       | ± 10<br>± 7 | ± 15<br>± 11       |       | mA<br>mA       |

| VIH              | Logic "1" voltage                          |                                                                            | 2.0         |                    |       | 2.0         |                    |       | v              |

| VIL              | Logic "0" voltage                          |                                                                            |             |                    | 0.8   |             |                    | 0.8   | v              |

| Iн               | Logic input current high                   | V <sub>S/H</sub> = 5V                                                      |             |                    | 0.1   |             |                    | 0.1   | μA             |

| I <sub>IL</sub>  | Logic input current low                    | V <sub>S/H</sub> = 0V                                                      |             |                    | ~15   |             |                    | - 15  | μA             |

| EN RMS           | Output noise                               | DC to 260kHz                                                               |             | 250                |       | 1           | 250                |       | μV             |

| V <sub>CC</sub>  | Positive supply voltage1                   |                                                                            | 13.5        | 15                 | 16.5  | 13.5        | 15                 | 16.5  | V              |

| VEE              | Negative supply <sup>1</sup>               |                                                                            | -13.5       | -15                | -16.5 | -13.5       | -15                | -16.5 | v              |

| ICC              | Positive supply current                    |                                                                            |             | 11.5               | 15    |             | 11.5               | 15    | mA             |

| <sup>i</sup> EE  | Negative supply current                    |                                                                            | 1           | -11.5              | ~14   |             | -11.5              | -14   | mA             |

| PSRR+            | Positive supply rejection ratio            | $V_{CC} = 15V \pm 5\%$ $V_{IN} = 0V$ $V_{IN} = \pm 10V$                    | 85<br>80    | 100<br>90          |       | 85<br>80    | 100<br>90          |       | dB<br>dB<br>dB |

| PSRR-            | Negative supply rejection ratio            | $V_{EE} = -15V \pm 5\%$ $V_{IN} = 0V$ $V_{IN} = \pm 10V$                   | 65<br>57    | 72<br>63           |       | 65<br>57    | 72<br>63           |       | dB<br>dB       |

NOTE:

1. Recommend operating supply voltage range for  $V_{IN} = \pm 10V$ ; DC specification production tested only at  $\pm 15V$ .

# NE/SE5060

## AC ELECTRICAL CHARACTERISTICS Test conditions, unless otherwise specified:

$\begin{array}{l} V_{CC}=15V; \ V_{EE}=-15V; \ V_{IN}=0V; \ V_{LC}=0V; \ R_{L}=2k\Omega; \ C_{L}=50pF; \ C_{H}=internal; \\ V_{S/H}=0.4V \ (for \ sample \ mode); \ V_{S/H}=3.5V \ (for \ hold \ mode); \ T_{A}=+25^{\circ}C. \end{array}$

| SYMBOL              | PARAMETER                                           | TEST CONDITIONS                                         | LIMITS |                 |           |                         |

|---------------------|-----------------------------------------------------|---------------------------------------------------------|--------|-----------------|-----------|-------------------------|

|                     |                                                     |                                                         | Min    | Тур             | Max       | UNIT                    |

| SR                  | Slew rate <sup>1</sup>                              |                                                         | 16     | 20              |           | V/µs                    |

|                     | Overshoot <sup>1</sup>                              |                                                         |        | 6               |           | %                       |

| BW                  | Full power bandwidth                                | V <sub>IN</sub> ∞ 20V <sub>P.P</sub>                    |        | 260             |           | kHz                     |

| t <sub>AQ</sub>     | Acquisition time, 1, 2                              |                                                         |        | 850             | 1250      | ns                      |

| tAPD                | Aperture delay                                      |                                                         |        | 30              |           | ns                      |

| t <sub>AP</sub>     | Aperture time                                       |                                                         |        | 25              |           | ns                      |

| tAPU                | Aperture uncertainty                                |                                                         |        | 1               |           | ns                      |

| V <sub>HT</sub>     | Sample - Hold transient (peak to peak) <sup>3</sup> |                                                         | -      | 2               | 15        | m۷                      |

| t <sub>HM</sub>     | Hold mode settling <sup>2, 3</sup>                  |                                                         |        | 35              | 125       | ns                      |

| Qt                  | Charge transfer <sup>3</sup>                        |                                                         |        | 0.1             | 0.25      | рС                      |

|                     | Hold step <sup>3, 4</sup>                           |                                                         |        | 1.0             | 2.5       | mV                      |

| dV <sub>H</sub> ∕dt | Drop rate                                           | $T_A = +25^{\circ}C$<br>0°C to +70°C<br>-55°C to +125°C |        | 0.2<br>2<br>150 | 5<br>200  | μV/μs<br>μV/μs<br>μV/μs |

| ID                  | Drop current                                        | $T_A = +25^{\circ}C$<br>0°C to +70°C<br>-55°C to +125°C |        | 2<br>100<br>10  | 500<br>20 | pA<br>pA<br>nA          |

|                     | Hold mode feedthrough                               | V <sub>IN</sub> = 10V <sub>P-P</sub> ; 100kHz           |        | 2               |           | ٣V                      |

NOTES:

1.  $V_{IN} = \pm 10V$  step.

2. To within 1.0mV of its final value (0.01%).

3.  $V_{S/H}$  (HIGH) = 3.5V;  $t_R = 50$ ns (VIL to VIH). 4. Can be adjusted to zero.

# NE/SE5060

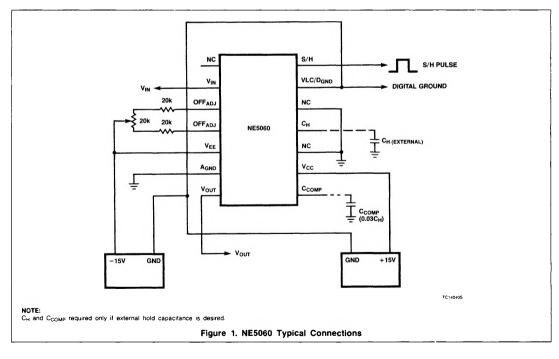

### APPLYING THE NE/SE5060

The NE/SE5060 is a high-performance sample-and-hold amplifier. In the track mode the device behaves as a non-inverting unity gain amplifier. In the hold mode the device holds the value of the output voltage that was present at the instant the sample-to-hold signal goes high.

#### **Hold Capacitor**

The NE/SE5060 includes an on-chip hold capacitor and achieves fast acquisition, low hold step, and droop rate which are adequate for most high-speed applications. However, if a smaller hold step and lower droop rate are desired, then an external hold capacitor ( $C_H$ ) may be added from Pin 11 to ground (Pin 6). The external hold capacitor should have high insulation resistance and low dielectric absorption to minimize droop errors.

If an external hold capacitor is used, then additional compensation capacitance of value  $0.03C_{\rm H}$  should be connected between Pin 8 and ground. Exact value and type are not critical. The additional hold capacitor will reduce the slew rate and increase acquisition time.

#### **Offset Adjustment**

The NE/SE5060 hold step error can be adjusted to zero using the offset adjustment pins as shown in the 'Typical Connections'. The error should be adjusted with the device in the hold mode, so that both the initial offset error and the hold-step error are nulled to zero. If desired, the center-tap of the offset adjustment potentiometer may be connected to V<sub>CC</sub> through a 1MΩ resistor in series with the center-tap of the potentiometer.

#### Layout and Other Considerations

A printed circuit board with ground plane is recommended for best performance. Bypass capacitors  $(0.01\mu F \text{ to } 0.1\mu F \text{ ceramic})$  should be provided for each power supply terminal to Pin 6 as close to the device as possible.

The ideal ground connections are as follows:

- a wide trace between Pin 6 and Pin 13

- Pin 6 to each power supply ground

- a separate trace from Pin 6 to the signal ground

- Pin 13 to digital ground.

The hold capacitor (Pin 11) is sensitive to stray coupling. Any connection made to this pin should be kept short and guarded by a ground plane since nearby signal lines or power supply voltages will introduce errors in the hold mode.

In unity gain applications requiring no external hold capacitor, the NE/SE5060 can directly replace the HA2420, HA2425, and HA5320. In applications requiring an additional hold capacitor, it should be remembered that the capacitor should be connected from Pin 11 to ground.

#### Sample/Hold Input

Optimum performance is achieved with a clean (no ringing) sample-to-hold pulse with a rise time between 20ns and 50ns.

NE/SE5060 is compatible with all logic families. For TTL and DTL interface, simply ground Pin 13. The internal threshold voltage is set to 1.4V above the voltage at Pin 13. For CMOS and HTL interface, the appropriate voltage may be applied to Pin 13. For proper operation the voltage applied at Pin 13 must be at least 4V below the positive supply and 3V above the negative supply.