# 4-BIT BINARY COUNTER | \$5493

N7493

\$5493-A,F,W • N7493-A,F

# DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

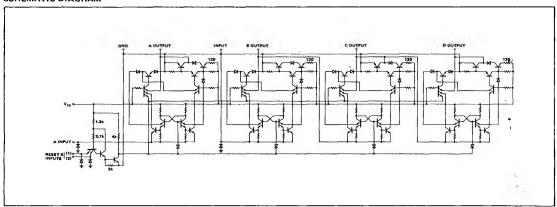

The S5493/N7493 is a high-speed, monolithic 4-bit binary counter consisting of four master-slave flip-flops which are internally interconnected to provide a divide-by-two counter and a divide-byeight counter. A gated direct reset line is provided which inhibits the count inputs and simultaneously returns the four flip-flop outputs to a logical O. As the output from flip-flop A is not internally connected to the succeeding flip-flops the counter may be operated in two independent modes:

- 1. When used as a 4-bit ripple-through counter output A must be externally connected to input B. The input count pulses are applied to input A. Simultaneous divisions of 2, 4, 8, and 16 are performed at the A, B, C, and D outputs as shown in the truth table.

- 2. When used as a 3-bit ripple-through counter, the input count pulses are applied to input B. Simultaneous frequency divisions of 2, 4, and 8 are available at the B, C, and D outputs. Independent use of flip-flop A is available if the reset function coincides with reset of the 3-bit ripple-through counter.

The S5493/N7493 is completely compatible with Series 54 and Series 74 logic families. Average power dissipation is 32mW per flip-flop (128mW total).

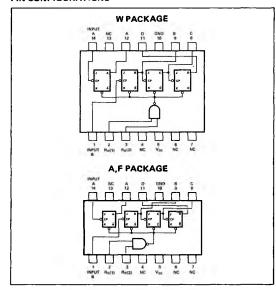

#### PIN CONFIGURATIONS

#### TRUTH TABLE (See Notes 1 and 2)

| LOGIC |   |        |   |    |  |  |  |

|-------|---|--------|---|----|--|--|--|

|       |   | OUTPUT |   |    |  |  |  |

| COUNT | D | С      | В | Α. |  |  |  |

| 0     | 0 | 0      | 0 | 0  |  |  |  |

| 1     | 0 | 0      | 0 | 1  |  |  |  |

| 2     | 0 | 0      | 1 | 0  |  |  |  |

| 3     | 0 | 0      | 1 | 1  |  |  |  |

| 4     | 0 | 1      | 0 | 0  |  |  |  |

| 5     | 0 | 1      | 0 | 1  |  |  |  |

| 6     | 0 | 1      | 1 | 0  |  |  |  |

| 7     | 0 | 1      | 1 | 1  |  |  |  |

| 8     | 1 | 0      | 0 | 0  |  |  |  |

| [     | OUTPUT |   |   |   |  |  |  |

|-------|--------|---|---|---|--|--|--|

| COUNT | D      | С | В | Α |  |  |  |

| 9     | 1      | 0 | 0 | 1 |  |  |  |

| 10    | 1      | 0 | 1 | 0 |  |  |  |

| 11    | 1      | 0 | 1 | 1 |  |  |  |

| 12    | 1      | 1 | 0 | 0 |  |  |  |

| 13    | 1      | 1 | 0 | 1 |  |  |  |

| 14    | 1      | 1 | 1 | 0 |  |  |  |

| 15    | 1      | 1 | 1 | 1 |  |  |  |

#### NOTES:

- 1. Output A connected to input B.

- 2. To reset all outputs to logical 0, both R<sub>0(1)</sub> and R<sub>0(2)</sub> inputs must be at logical 1.

#### SCHEMATIC DIAGRAM

## RECOMMENDED OPERATING CONDITIONS

|                                                          | MIN  | NOM | MAX  | UNIT |

|----------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> : S5493 Circuits          | 4.5  | 5   | 5.5  | V    |

| N7493 Circuits                                           | 4.75 | 5   | 5.25 | V    |

| Operating Free-Air Temperature Range, Ta: S5493 Circuits | -55  | 25  | 125  | °c   |

| N7493 Circuits                                           | 0    | 25  | 70   | °c   |

| Normalized Fan-Out from each Output, N                   |      |     | 10   |      |

| Width of Input Count Pulse, tp(in)                       | 50   |     | 1    | ns   |

| Width of Reset Pulse, tp(reset)                          | 50   |     |      | ns   |

## ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

|                    | PARAMETER                                                                      | T                                                | EST CONDITIONS*                                  |                | MIN        | TYP**    | MAX            | דואט     |

|--------------------|--------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------------|------------|----------|----------------|----------|

| V <sub>in(1)</sub> | Input voltage required<br>to ensure logical 1 at<br>any input terminal         | V <sub>CC</sub> = MIN                            |                                                  |                | 2          |          |                | ٧        |

| V <sub>in(0)</sub> | Input voltage required to ensure logical 0 at any input terminal               | V <sub>CC</sub> = MIN                            |                                                  |                |            |          | 0.8            | "        |

| $V_{out(1)}$       | Logical 1 output voltage                                                       | V <sub>CC</sub> - MIN,                           | I <sub>load</sub> = -400μA                       |                | 2.4        |          |                | \ V      |

| $V_{out(0)}$       | Logical 0 output voltage                                                       | VCC = MIN,                                       | I <sub>sink</sub> = 16mA                         |                |            |          | 0.4            | V        |

| lin(1)             | Logical 1 level input current at R <sub>O(1)</sub> or R <sub>O(2)</sub> inputs | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                |            |          | <b>40</b><br>1 | μA<br>m/ |

| lin(1)             | Logical 1 level input<br>current at A or B inputs                              | V <sub>CC</sub> = MAX,<br>V <sub>CC</sub> = MAX, | V <sub>in</sub> = 2.4V<br>V <sub>in</sub> = 5.5V |                | 0          |          | 80<br>1        | μA<br>m. |

| lin(0)             | Logical 0 level input current at $R_{O(1)}$ or $R_{O(2)}$ inputs               | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |                |            |          | -1.6           | m        |

| lin(0)             | Logical 0 level input<br>current at A or B inputs                              | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 0.4V                           |                |            |          | -3.2           | m/       |

| los                | Short circuit output current <sup>†</sup>                                      | V <sub>CC</sub> = MAX,                           | V <sub>out</sub> = 0                             | S5493<br>N7493 | -20<br>-18 |          | -57<br>-57     | m/       |

| <sup>1</sup> cc    | Supply current                                                                 | V <sub>CC</sub> = MAX,                           | V <sub>in</sub> = 4.5V                           | S5493<br>N7493 |            | 32<br>32 | 46<br>53       | m.<br>m. |

# SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_A$ = 25°C, N = 10

| PARAMETER                                    |                                                                                       | TEST CONDITIONS        |                       |    | MIN | TYP | MAX | UNIT |

|----------------------------------------------|---------------------------------------------------------------------------------------|------------------------|-----------------------|----|-----|-----|-----|------|

| fmax Maximum frequency of input count pulses | C <sub>L</sub> = 15pF,                                                                | R <sub>L</sub> = 400Ω  |                       | 10 | 18  |     | MHz |      |

| <sup>t</sup> pd1                             | Propagation delay time<br>to logical 1 level from<br>input count pulse to<br>output D | CL = 15pF,             | R <sub>L</sub> = 400Ω | }  |     | 75  | 135 | ns   |

| <sup>t</sup> pd0                             | Propagation delay time<br>to logical 0 level from<br>input count pulse to<br>output D | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | <  |     | 76  | 135 | ns   |

<sup>·</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable device type.

• All typical values are at  $V_{CC}^-$  5V,  $T_A = 25^{\circ}$ C.

† Not more than one output should be shorted at a time.