#### TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# T6L60

#### Gate Driver for TFT LCD Panels

The T6L60 is a 150/154-channel output gate driver for TFT LCD panels. This device accepts external input of the panel drive voltage, allowing you to change the low-level output voltage. Thus, this device can be used for various TFT LCD panel drive systems.

#### Features

- LCD drive output pins : Switchable between 150 and 154 pins

- LCD drive voltage  $\therefore \max V_{EE} + 40 V$

- Data transfer method : Bidirectional shift register

- Operating temperature: -20 to 75°C

- Package : Tape carrier package (TCP)

|                                                                                                                             |         | Unit: mm |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|---------|----------|--|--|--|--|

| <b>T</b> 01.00                                                                                                              | User ar | ea pitch |  |  |  |  |

| T6L60                                                                                                                       | IN      | OUT      |  |  |  |  |

| (SAN, 3NS)                                                                                                                  | 0.80000 | 0.14979  |  |  |  |  |

| (SAN, 3NS)0.800000.14979Please contact Toshiba or a distributor for<br>the latest TCP specification and product<br>line-up. |         |          |  |  |  |  |

TCP (Tape Carrier Package)

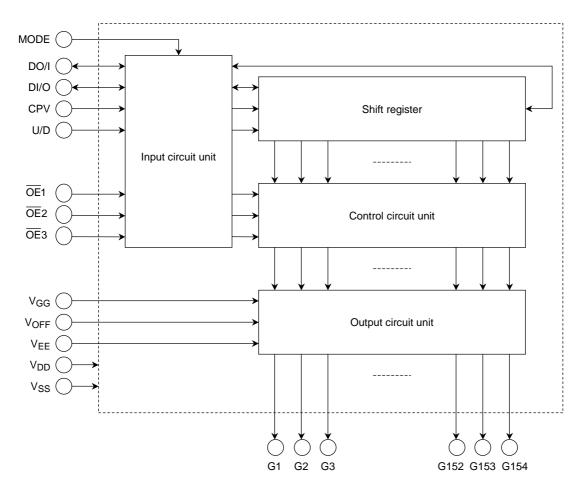

#### **Block Diagram**

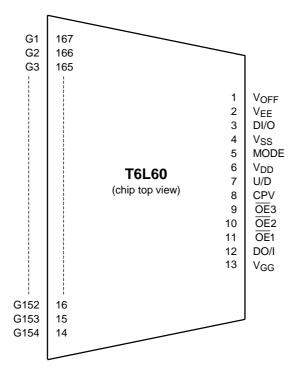

#### **Pin Assignment**

The above diagram shows the device's pin configuration only and does not necessarily correspond to the pad layout on the chip. Please contact Toshiba or our distributors for the latest TCP specification.

#### **Pin Function**

| Pin Name                             | I/O |                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |                                                   |          |  |  |  |

|--------------------------------------|-----|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------|----------|--|--|--|

|                                      |     | These p                                      | Vertical shift data I/O pins<br>These pins are used to input and output shift data. These pins are switched between input and<br>output by setting the U/D pin as shown below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                          |                                                   |          |  |  |  |

|                                      |     |                                              | U/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DI/O                                                     | DO/I                                              |          |  |  |  |

| DI/O                                 |     |                                              | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Input                                                    | Output                                            |          |  |  |  |

| DO/I                                 | I/O |                                              | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Output                                                   | Input                                             |          |  |  |  |

|                                      |     | The data                                     | is used to feed data into<br>a is latched into the shift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | o the shift registers at th<br>registers at the rising e | e first stage of the LCD o<br>dge of CPV.         | driver.  |  |  |  |

|                                      |     | When set fo<br>When tw<br>stage. T           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | cascaded, this pin outpu                                 | ts the data to be fed into<br>alling edge of CPV. | the next |  |  |  |

| U/D                                  | I   | This pin<br>The shif<br>Wh<br>G1<br>Wh<br>G1 | This pin specifies the direction in which data is transferred through the shift registers.<br>The shift register data is shifted synchronously with each rising edge of CPV as follows:<br>When U/D is high, data is shifted in the direction<br>$G1 \rightarrow G2 \rightarrow G3 \rightarrow G4 \rightarrow \dots \rightarrow G154$<br>When U/D is low, the direction is reversed to give<br>$G154 \rightarrow G153 \rightarrow G152 \rightarrow G151 \rightarrow \dots \rightarrow G1$<br>The voltage applied to this pin must be a DC-level voltage that is either high (V <sub>DD</sub> ) or low (V <sub>SS</sub><br>or V <sub>EE</sub> ) |                                                          |                                                   |          |  |  |  |

| CPV                                  | I   | This is the s                                | /ertical shift clock<br>This is the shift clock for the shift registers. Data is shifted through the shift registers<br>synchronously with the rising edge of CPV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                          |                                                   |          |  |  |  |

| $\overline{OE}1$ to $\overline{OE}3$ | I   | These s<br>OE doo<br>The                     | Putput enable pins<br>These signals control the data appearing at the LCD panel drive pins (G1 through G154).<br>OE doesn't synchronize with the CPU.<br>The V <sub>OFF</sub> voltage is output when OE1 to OE 3 are high; normal shift data is output<br>when OE 1 to OE 3 are low.                                                                                                                                                                                                                                                                                                                                                           |                                                          |                                                   |          |  |  |  |

| MODE                                 | I   | This sigi<br>Wh<br>use                       | Dutput channels select pin<br>This signal selects either 150-pin mode or 154-pin mode for the LCD panel driver.<br>When MODE = high, 150-pin mode is selected, in which case G76 through G79 are not<br>used. (V <sub>OFF</sub> level)<br>When MODE = low, 154-pin mode is selected.                                                                                                                                                                                                                                                                                                                                                           |                                                          |                                                   |          |  |  |  |

| G1 to G154                           | о   | These pins                                   | CD panel drive pins<br>These pins $output$ the shift register data or the voltage applied to $V_{GG}$ or $V_{OFF}$ depending on the<br>control signals OE1 to OE 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |                                                   |          |  |  |  |

| V <sub>GG</sub>                      |     | Power supp                                   | ly for LCD drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |                                                   |          |  |  |  |

| VOFF                                 |     |                                              | Analog reference voltage<br>These pins accept as their input the OFF level at the LCD panel drive pins (G1 through G154).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |                                                   |          |  |  |  |

| V <sub>EE</sub>                      | —   | Power supp                                   | ly for LCD drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |                                                   |          |  |  |  |

| V <sub>DD</sub>                      |     | Power supp                                   | ly for the internal logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |                                                   |          |  |  |  |

| V <sub>SS</sub>                      | —   | Power supp                                   | ly for the internal logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |                                                   |          |  |  |  |

#### **Device Operation**

#### (1) Shift data transfer method

| Mode Pin U/D Pin | Shift Data |       | Data Transfer Method |                                                                                                                                                                     |

|------------------|------------|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode Fill        | 0/D Fill   | Input | Output               |                                                                                                                                                                     |

| н                | Н          | DI/O  | DO/I                 | $\text{G1} \rightarrow \text{G2} \rightarrow \text{G3} \rightarrow \cdots \rightarrow \text{G75} \rightarrow \text{G80} \rightarrow \cdots \rightarrow \text{G154}$ |

| (150-out)        | L          | DO/I  | DI/O                 | $G154 \rightarrow G153 \rightarrow G152 \rightarrow \cdots \rightarrow G80 \rightarrow G75 \rightarrow \cdots \rightarrow G1$                                       |

| L                | Н          | DI/O  | DO/I                 | $G1 \rightarrow G2 \rightarrow G3 \rightarrow G4 \rightarrow \cdots \rightarrow G154$                                                                               |

| (154-out)        | L          | DO/I  | DI/O                 | $G154 \to G153 \to G152 \to G151 \to \cdots \to G1$                                                                                                                 |

The input data (DI/O or DO/I) is latched into the internal register synchronously with the rising edge of the shift clock CPV. At the same time that the data is shifted to the next register at the next rise of CPV, new vertical shift data is latched into.

In the output operation, the data in the last shift register (G154 or G1) is output synchronously with the falling edge of CPV. (The output high voltage is the  $V_{DD}$  level; the output low voltage is the  $V_{SS}$  level.)

Note: The outputs of G76 to G79 are  $V_{\mbox{OFF}}$  level in 150 output mode.

#### (2) LCD panel drive outputs

The LCD panel drive outputs are controlled by  $\overline{\text{OE}1}$  to  $\overline{\text{OE}3}$  as shown below.

The following combinations of mode pins and output enable pins don't depend on the polarity of U/D pins; hence, LCD panel drive outputs for LCD panel drive pins controlled by  $\overline{OE}$  are the same when the U/D pins is High or Low.

| Mode Pin  | Output Enable Pin       | LCD Panel Drive Outputs<br>LCD Panel Drive Pins Controller by | Output                 |  |

|-----------|-------------------------|---------------------------------------------------------------|------------------------|--|

|           | $\overline{OE}1 = "H"$  | G1, G4, G7, …G73, G80 … G149, G152                            |                        |  |

|           | $\overline{OE}2 = "H"$  | G2, G5, G8, …G74, G81 … G150, G153                            | V <sub>OFF</sub> level |  |

| н         | $\overline{OE}3 = "H"$  | G3, G6, G9, …G75, G82 … G151, G154                            |                        |  |

| (150-out) | $\overline{OE}1 = L"$   | G1, G4, G7, …G73, G80 … G149, G152                            |                        |  |

|           | $\overline{OE}2 = ``L"$ | G2, G5, G8, …G74, G81 … G150, G153                            | Normal data output     |  |

|           | $\overline{OE}3 = "L"$  | G3, G6, G9, …G75, G82 … G151, G154                            |                        |  |

|           | $\overline{OE}1 = "H"$  | G1, G4, G7,G148, G151, G154                                   |                        |  |

|           | $\overline{OE}2 = "H"$  | G2, G5, G8, …G149, G152                                       | V <sub>OFF</sub> level |  |

| L         | $\overline{OE}3 = "H"$  | G3, G6, G9, …G150, G153                                       |                        |  |

| (154-out) | $\overline{OE}1 = "L"$  | G1, G4, G7,G148, G151, G154                                   |                        |  |

|           | $\overline{OE}2 = ``L"$ | G2, G5, G8, …G149, G152                                       | Normal data output     |  |

|           | $\overline{OE}3 = ``L"$ | G3, G6, G9,G150, G153                                         |                        |  |

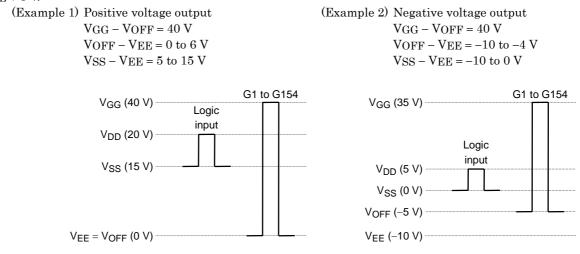

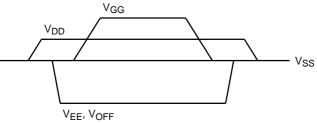

#### (3) Voltage setting

TOSHIBA

The VOFF level, which sets the LCD panel drive's output low level, can take on any value between VEE to VEE + 6 V.

Note: The logic input here means input pins DI/O, DO/I, CPV, MODE and  $\overline{OE1}$  to  $\overline{OE3}$ . The amplitude between V<sub>SS</sub> and V<sub>DD</sub> is applied to above pins. Make sure that the voltage applied to the U/D pin is a high (= V<sub>DD</sub>) or low (= V<sub>SS</sub> or V<sub>EE</sub>) DC-level voltage.

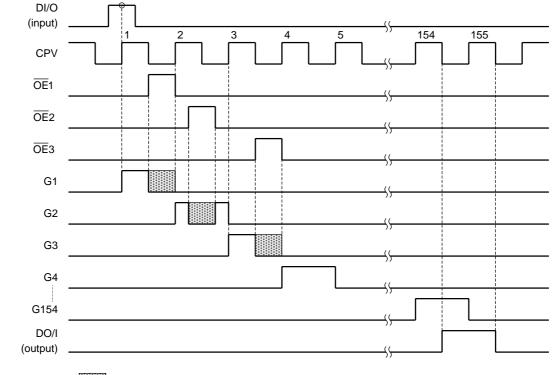

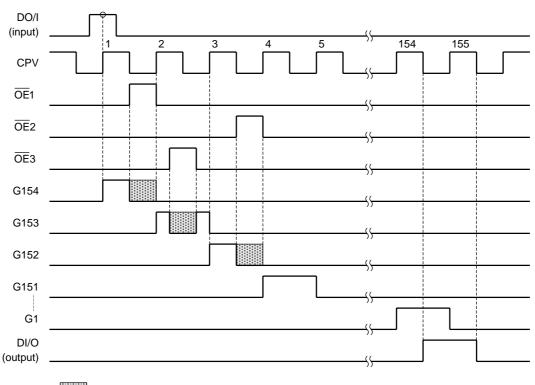

#### **Timing Diagram 1**

#### 154-output-pin (MODE = low), UP mode (U/D = high)

<sup>:</sup> This part is output which is controlled (fixed to V\_OFF) by  $\overline{\mbox{OE}}$  pin.

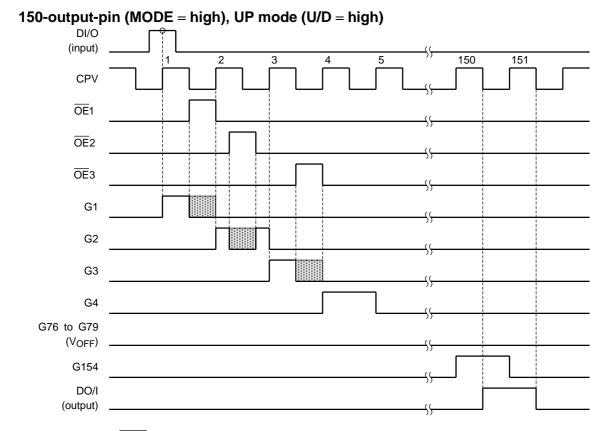

#### Timing Diagram 2

#### 154-output-pin (MODE = low), DOWN mode (U/D = low)

: This part is output which is controlled (fixed to V<sub>OFF</sub>) by  $\overline{\text{OE}}$  pin.

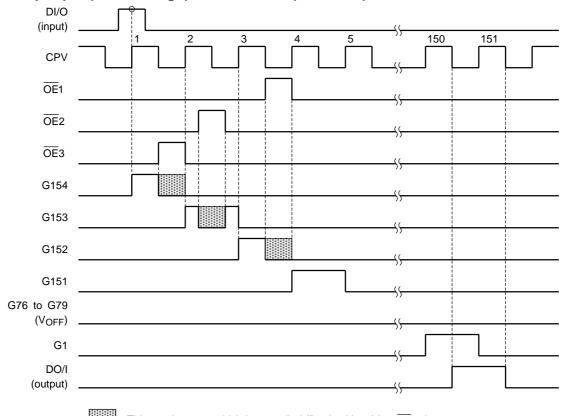

#### **Timing Diagram 3**

: This part is output which is controlled (fixed to V<sub>OFF</sub>) by  $\overline{\text{OE}}$  pin.

#### **Timing Diagram 4**

#### 150-output-pin (MODE = high), DOWN mode (U/D = low)

: This part is output which is controlled (fixed to V\_OFF) by  $\overline{\mbox{OE}}$  pin.

#### Absolute Maximum Ratings ( $V_{SS} = 0 V$ )

| Characteristics     | Symbol             | Rating                                            | Unit |

|---------------------|--------------------|---------------------------------------------------|------|

| Supply voltage (1)  | V <sub>DD</sub>    | -0.3 to 22.0                                      |      |

| Supply voltage (2)  | V <sub>SS</sub>    | -0.3 to 16.5                                      |      |

| Supply voltage (3)  | $V_{DD} - V_{SS}$  | -0.3 to 7.0                                       | V    |

| Supply voltage (4)  | VOFF               | -0.3 to 7.0                                       | v    |

| Supply voltage (5)  | V <sub>GG</sub>    | -0.3 to 45.0                                      |      |

| Supply voltage (6)  | $V_{GG} - V_{OFF}$ | -0.3 to 45.0                                      |      |

| Input voltage       | V <sub>IN</sub>    | V <sub>SS</sub> – 0.3 to<br>V <sub>DD</sub> + 0.3 | V    |

| Storage temperature | T <sub>stg</sub>   | -55 to 125                                        | °C   |

#### Recommended Operating Conditions ( $V_{SS} = 0 V$ )

| Characteristics         | Symbol            | Rating                    | Unit   |

|-------------------------|-------------------|---------------------------|--------|

| Supply voltage (1)      | V <sub>SS</sub>   | 5 to 15                   |        |

| Supply voltage (2)      | V <sub>DD</sub>   | VSS + 3.0 to<br>VSS + 5.5 | V      |

| Supply voltage (3)      | VOFF              | 0 to 6                    |        |

| Supply voltage (4)      | $V_{GG} - V_{SS}$ | 17 to 25                  |        |

| Operating temperature   | T <sub>opr</sub>  | -20 to 75                 | °C     |

| Operating frequency     | fCPV              | DC to 100                 | kHz    |

| Output load capacitance | CL                | 300 (max)                 | pF/pin |

#### **Electrical Characteristics**

# $\begin{array}{l} \text{DC Characteristics} \Bigg( \text{V}_{GG} - \text{V}_{SS} = 17 \text{ to } 25 \text{ V}, \text{V}_{DD} = 3.0 \text{ to } 5.5 \text{ V}, \text{V}_{SS} = 0 \text{ V}, \\ \text{Ta} = -20 \text{ to } 75^{\circ}\text{C}, \text{V}_{EE} = -15 \text{ to } -5 \text{ V}, \text{V}_{OFF} = \text{V}_{EE} \text{ to } \text{V}_{EE} + 6 \text{ V} \end{array} \Bigg)$

| Charact                 | eristics   | Symbol          | Test<br>circuit | Test Condition                               | Min                                                                           | Max                                                                           | Unit | Relevant<br>Pin |

|-------------------------|------------|-----------------|-----------------|----------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|-----------------|

| Input voltage           | Low level  | VIL             |                 |                                              | V <sub>SS</sub>                                                               | $\begin{array}{c} 0.1 \times \\ (V_{DD} - \\ V_{SS}) + \\ V_{SS} \end{array}$ | V    | (Note 1)        |

|                         | High level | VIH             |                 |                                              | $\begin{array}{c} 0.9 \times \\ (V_{DD} - \\ V_{SS}) + \\ V_{SS} \end{array}$ | V <sub>DD</sub>                                                               | V    |                 |

| Output voltage          | Low level  | V <sub>OL</sub> |                 | $I_{OL} = 40 \ \mu A$                        | V <sub>SS</sub>                                                               | V <sub>SS</sub> +<br>0.4                                                      | V    | DI/O,           |

|                         | High level | V <sub>OH</sub> |                 | I <sub>OH</sub> = -40 μA                     | V <sub>DD</sub> -<br>0.4                                                      | V <sub>DD</sub>                                                               | v    | DO/Í            |

| Output<br>resistance    | Low level  | R <sub>OL</sub> |                 | $V_{OUT} = V_{EE} + 0.5 \text{ V} $ (Note 1) |                                                                               | 1500                                                                          | Ω    | G1 to           |

|                         | High level | R <sub>OH</sub> |                 | $V_{OUT} = V_{GG} - 0.5 \text{ V} $ (Note 1) | _                                                                             | 1500                                                                          | 52   | G154            |

| Input leakage cu        | rrent      | I <sub>IN</sub> |                 |                                              | -1                                                                            | 1                                                                             | μA   | (Note 2)        |

| Current consump         | otion (1)  | I <sub>DD</sub> |                 |                                              |                                                                               | 1500                                                                          |      |                 |

| Current consumption (2) |            | I <sub>SS</sub> | ] —             | (Note 3)                                     | -200                                                                          |                                                                               | μA   |                 |

| Current consump         | otion (3)  | I <sub>GG</sub> |                 |                                              |                                                                               | 150                                                                           |      |                 |

Note 1:  $V_{GG} - V_{EE} = 25$  to 35 V

Note 2: Input pins · · · DI/O, DO/I, CPV, OE1 to OE3 , MODE

Note 3: Current consumption in 1/600-duty LCD. Input  $V_{IH} = V_{DD}$ ,  $V_{IL} = V_{SS}$ ,  $f_{CPV} = 100 \text{ kHz}$ Start pulse period = 104.2 Hz,  $\overline{OE1}$  to  $\overline{OE3} = V_{SS}$ , no load

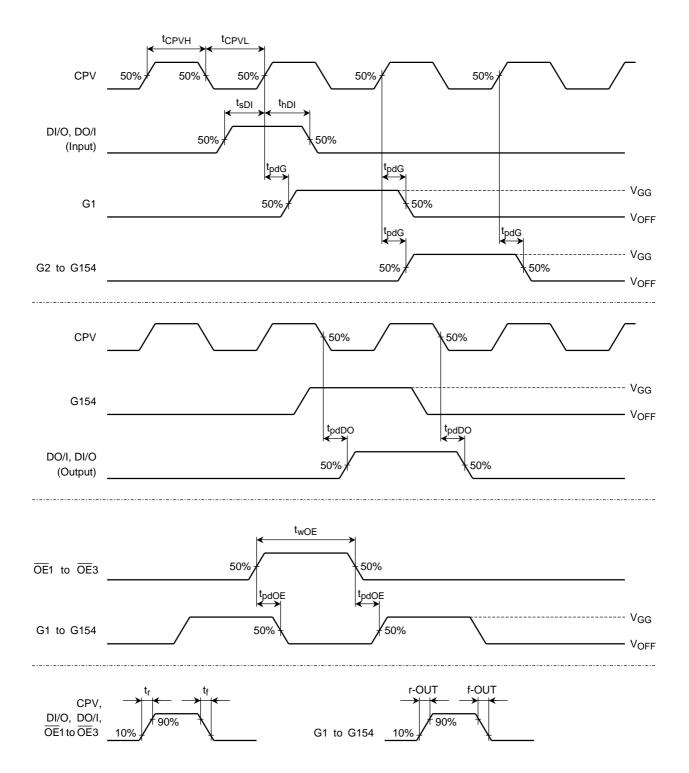

## AC Characteristics $\begin{pmatrix} V_{GG} - V_{SS} = 17 \text{ to } 25 \text{ V}, V_{DD} = 3.0 \text{ to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, \\ Ta = -20 \text{ to } 75^{\circ}\text{C}, V_{EE} = -15 \text{ to } -5 \text{ V}, V_{OFF} = V_{EE} \text{ to } V_{EE} + 6 \text{ V} \end{pmatrix}$

| Characteristics       | Symbol             | Test<br>circuit | Test Condition                                                        | Min | Max  | Unit |

|-----------------------|--------------------|-----------------|-----------------------------------------------------------------------|-----|------|------|

| Clock period          | t <sub>CPV</sub>   | _               | —                                                                     | _   | 100  | kHz  |

| CPV pulse width (H)   | t <sub>CPVH</sub>  | _               | —                                                                     | 5   | _    | μS   |

| CPV pulse width (L)   | tCPVL              | _               | _                                                                     | 5   | _    | μS   |

| Data set-up time      | t <sub>sDI</sub>   | _               | _                                                                     | 700 | _    | ns   |

| Data hold time        | t <sub>hDI</sub>   |                 | —                                                                     | 700 |      | ns   |

| OE enable time        | t <sub>wOE</sub>   | _               | —                                                                     | 1   |      | μS   |

| Output delay time (1) | t <sub>pdDO</sub>  | _               | C <sub>L</sub> = 30 pF                                                |     | 1000 | ns   |

| Output delay time (2) | t <sub>pd</sub> G  | _               | C <sub>L</sub> = 300 pF                                               | _   | 800  | ns   |

| Output delay time (3) | t <sub>pd</sub> OE |                 | C <sub>L</sub> = 300 pF                                               |     | 800  | ns   |

| Input rising time     | tr                 | —               | C <sub>L</sub> = 300 pF                                               |     | 30   | ns   |

| Input falling time    | t <sub>f</sub>     | —               | C <sub>L</sub> = 300 pF                                               |     | 30   | ns   |

| Output rising time    | r-OUT              | —               | C <sub>L</sub> = 300 pF                                               |     | 500  | ns   |

| Output falling time   | f-OUT              | —               | $C_L = 300 \text{ pF}, \text{ V}_{OFF} = \text{V}_{EE} = 0 \text{ V}$ |     | 500  | ns   |

#### **Power Supply Sequence**

Turn power on in the order VSS  $\rightarrow$  VDD  $\rightarrow$  Input signal  $\rightarrow$  VEE  $\rightarrow$  VOFF  $\rightarrow$  VGG. Turn power off in th reverse order.

#### **RESTRICTIONS ON PRODUCT USE**

000707EBE

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and

conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- Polyimide base film is hard and thin. Be careful not to injure yourself on the film or to scratch any other parts with the film. Try to design and manufacture products so that there is no chance of users touching the film after assembly, or if they do, that there is no chance of them injuring themselves. When cutting out the film, try to ensure that the film shavings do not cause accidents. After use, treat the leftover film and reel spacers as industrial waste.

- Light striking a semiconductor device generates electromotive force due to photoelectric effects. In some cases this can cause the device to malfunction. This is especially true for devices in which the surface (back), or side of the chip is exposed. When designing circuits, make sure that devices are protected against incident light from external sources. Exposure to light both during regular operation and during inspection must be taken into account.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.