# TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T7779

# CRT / LCD Controller LSI

The T7779 is a controller LSI for a raster–scan–type CRT display and large–scale dot matrix LCD. It can be used in applications ranging from small–scale character display systems to large–scale graphic display systems.

# Features

- Refresh memory address  $\therefore$  MA0 to MA15 (2<sup>16</sup>)

- Line scanning address

- Frame buffer capacity

- : Max 64 KBytes (character) Max 2 MBytes (graphic)

$: LA0 \text{ to } LA4 (2^5)$

- Number of characters per line : 1 to 255

- Number of character rows : 1 to 255

- Scrolling, Paging

- Built-in light pen-detecting function

- Horizontal dots per character according to font : 5, 6, 7, 8

- Vertical dots per character according to font : 1 to 32

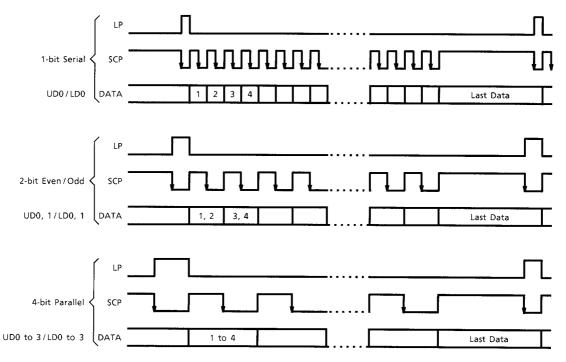

- Data output : 1-bit output, 2-bit (odd/even) output, 4-bit output

- Various attribute functions

: Underline Cursor ON/OFF Underline Cursor Blink Character ON/OFF Character Normal/Inverse Character Blink Blink Frequency Change

- External synchronization (Non-Interlace mode only)

- HMCS6800-family-compatible bus interface

- Single 5-V power supply

- High speed operation : 18 MHz

- Low power consumption

- CMOS, Si-Gate structure

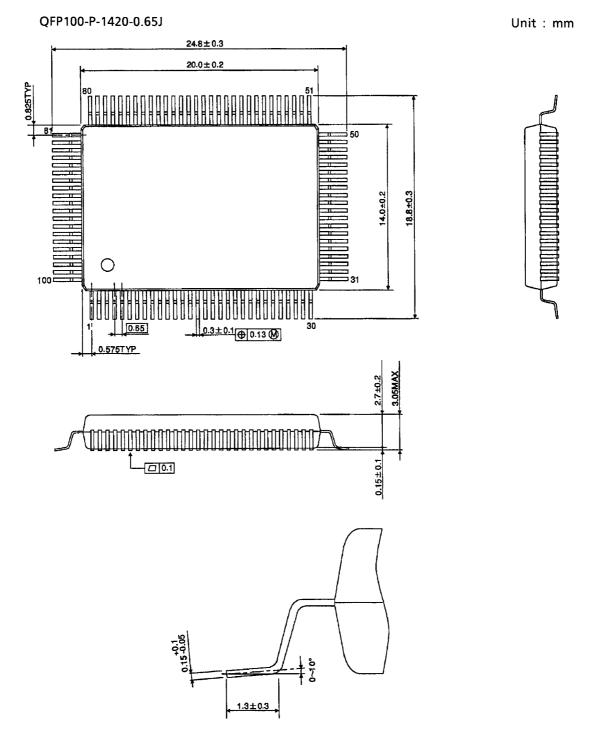

- 100-pin flat plastic package

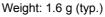

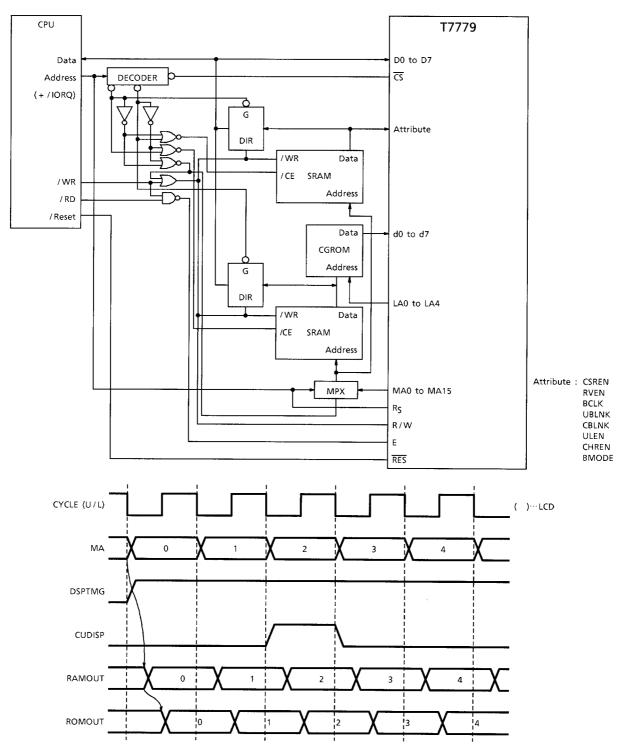

# **Block Diagram**

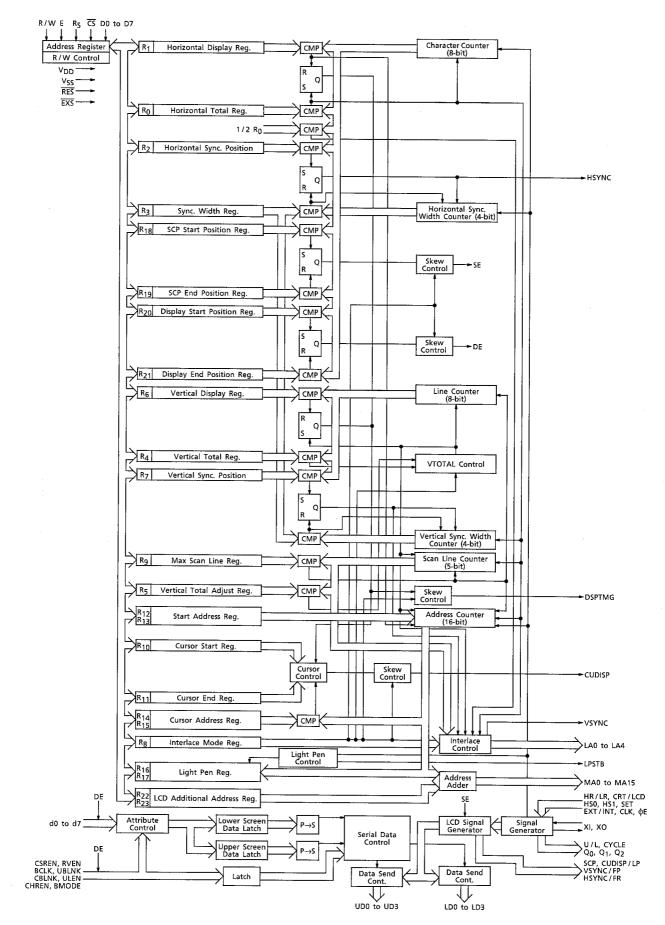

### **Pin Assignment**

# **Pin Functions**

| Pin Name    | I/O    | Functio                                                                                                                               | ons             |               |                     |                      |  |  |  |  |

|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|---------------------|----------------------|--|--|--|--|

| MA0 to MA15 | Output | (Memory Address)<br>Memory refresh address                                                                                            |                 |               |                     |                      |  |  |  |  |

| LA0 to LA4  | Output | (Line Address)<br>Line scanning address for character generator                                                                       |                 |               |                     |                      |  |  |  |  |

| D0 to D7    | I/O    | (Data)<br>Data I / O terminal for built-in registers                                                                                  |                 |               |                     |                      |  |  |  |  |

| d0 to d7    | Input  | (Data)<br>Parallel data input for LCD                                                                                                 |                 |               |                     |                      |  |  |  |  |

| ADF         | Input  | (Address Float)<br>For LA / MA outputs in High Impedance mode.                                                                        | High impedan    | ce when s     | set to 0            |                      |  |  |  |  |

| CSREN       | Input  | (Cursor Enable)<br>Underline cursor enabling signal<br>Display of cursor is enabled when set to 1 (d0 t                               | o d7 are inhibi | ted)          |                     |                      |  |  |  |  |

| RVEN        | Input  | (Reverse Enable)<br>Reverse attribute signal. Display of d0 to d7 is inverted when set to 1 (except for the<br>cursor)                |                 |               |                     |                      |  |  |  |  |

| BCLK        | Input  | (Blink Clock)<br>Clock input for blink. 0 = ON, 1 = OFF                                                                               |                 |               |                     |                      |  |  |  |  |

| UBLNK       | Input  | (Underline Blink)<br>Underline blink attribute signal. Blink is enabled                                                               | l when set to 1 |               |                     |                      |  |  |  |  |

| CBLNK       | Input  | (Character Blink)<br>Character blink attribute signal. Blink is enabled                                                               | d when set to 1 |               |                     |                      |  |  |  |  |

| ULEN        | Input  | (Underline Enable)<br>Underline attribute signal. Underline is displaye                                                               | d when set to   | 1             |                     |                      |  |  |  |  |

| CHREN       | Input  | (Character Enable)<br>Data input enabling signal. Display is enabled v                                                                | vhen set to 1   |               |                     |                      |  |  |  |  |

|             |        | (Blink Mode)                                                                                                                          | BMODE           | 0             | 1                   | 1                    |  |  |  |  |

| BMODE       | Input  | To change an external / internal blink clock<br>f <sub>BCLK</sub> : Clock frequency supplied to the BCLK                              | BCLK            | —             | 0                   | 1                    |  |  |  |  |

|             |        | f <sub>FR</sub> : Frame frequency                                                                                                     | Blink Freq.     | <b>f</b> BCLK | f <sub>FR</sub> / 8 | f <sub>FR</sub> / 16 |  |  |  |  |

| SET         | Input  | (Set)<br>To set built-in registers. Set when SET = 1 and CRT / LCD = 1                                                                |                 |               |                     |                      |  |  |  |  |

| HR / LR     | Input  | (High Resolution / Low Resolution)<br>High Resolution / Low Resolution mode select. High Resolution mode is selected when<br>set to 1 |                 |               |                     |                      |  |  |  |  |

| CRT / LCD   | Input  | (Cathode Ray Tube / Liquid Crystal Display)<br>CRT / LCD mode select. LCD mode is selected                                            | when set to 1   |               |                     |                      |  |  |  |  |

| Pin Name    | I/O    | Functi                                                                                       | ons         |                |                  |  |  |  |

|-------------|--------|----------------------------------------------------------------------------------------------|-------------|----------------|------------------|--|--|--|

| CS          | Input  | (Chip Select)                                                                                | CS          | R <sub>S</sub> | Register name    |  |  |  |

| 03          | input  | Chip select signal input                                                                     | 1           | _              | Invalid          |  |  |  |

| Rs          | Input  | (Register Select)                                                                            | 0           | 0              | Address register |  |  |  |

|             | mput   | Register select signal input                                                                 | 0           | 1              | Control register |  |  |  |

| E           | Input  | (Enable)<br>Enable signal input. Usually connected to syst                                   | em φ2 cloo  | ck.            |                  |  |  |  |

| R / W       | Input  | (Read / Write)<br>R / W signal input. Read when set to 1                                     |             |                |                  |  |  |  |

| RES         | Input  | (Reset)<br>Reset signal input. Reset when set to 0                                           |             |                |                  |  |  |  |

| LPSTB       | Input  | (Light Pen Strobe)<br>Light pen strobe signal input                                          |             |                |                  |  |  |  |

| DSPTMG      | Output | (Display Timing)<br>Display timing signal                                                    |             |                |                  |  |  |  |

| CUDISP      | Output | (Cursor Display)<br>Cursor display signal                                                    |             |                |                  |  |  |  |

| CUDISP / LP | Output | (Cursor Display / Latch Pulse)<br>Cursor display / latch pulse                               |             |                |                  |  |  |  |

| HSYNC       | Output | (Horizontal SYNC)<br>Horizontal synchronization                                              |             |                |                  |  |  |  |

| HSYNC / FR  | Output | (Horizontal SYNC / Frame)<br>Horizontal sync / frame                                         |             |                |                  |  |  |  |

| VSYNC       | Output | (Vertical SYNC)<br>Vertical synchronization                                                  |             |                |                  |  |  |  |

| VSYNC / FP  | Output | (Vertical SYNC / Frame Pulse)<br>Vertical sync / frame pulse                                 |             |                |                  |  |  |  |

| SCP         | Output | (Shift Clock Pulse)<br>Shift clock pulse for column driver                                   |             |                |                  |  |  |  |

| MCS         | Output | (Multi Controller Sync)<br>Multi controller synchronization                                  |             |                |                  |  |  |  |

| U/L         | Output | (Upper / Lower)<br>Upper / lower screen signal. Upper screen who                             | en set to 0 |                |                  |  |  |  |

| CYCLE       | Output | (Cycle Steal)<br>Cycle steal signal                                                          |             |                |                  |  |  |  |

| CE          | Output | (Chip Enable)<br>Chip enable signal                                                          |             |                |                  |  |  |  |

| DSC1        | Input  | (Data Sending Control 1)<br>Serial data format select                                        |             |                |                  |  |  |  |

| LD3 / DSC0  | 0/1    | (Lower Data 3 / Data Sending Control 0)<br>Serial data for column driver / serial data forma | at select   |                |                  |  |  |  |

| Pin Name             | 1/0    | Functions                                                       |                                                                                         |   |   |   |   |  |  |

|----------------------|--------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------|---|---|---|---|--|--|

| LD0 to LD2           | Output | (Lower Data 0 to 2)<br>Serial data for column driver            |                                                                                         |   |   |   |   |  |  |

| UD0 to UD3           | Output | (Upper Data 0 to 3)<br>Serial data for column driver            |                                                                                         |   |   |   |   |  |  |

| EXS                  | Input  | (External Sync)<br>External synchronization                     |                                                                                         |   |   |   |   |  |  |

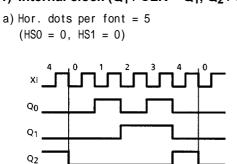

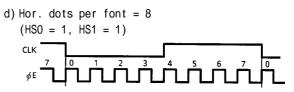

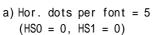

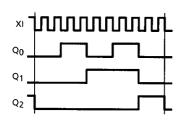

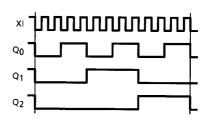

|                      |        | (Horizontal Select)                                             | HS0                                                                                     | 0 | 1 | 0 | 1 |  |  |

| HS0, HS1             | Input  | To determine the number of                                      | HS1                                                                                     | 0 | 0 | 1 | 1 |  |  |

|                      |        | horizontal dots per font                                        | Horizontal dot                                                                          | 5 | 6 | 7 | 8 |  |  |

| Q <sub>0</sub>       | Output | Built-in dot counter output                                     |                                                                                         |   |   |   |   |  |  |

| Q <sub>1</sub> / CLK | 0/1    | Built-in dot counter output / word c                            | lock input                                                                              |   |   |   |   |  |  |

| Q <sub>2</sub> / φΕ  | 0/1    | Built-in dot counter output / dot clo                           | ck input                                                                                |   |   |   |   |  |  |

| EXT / INT            | Input  | (External / Internal)<br>External / internal clock select. Inte | (External / Internal)<br>External / internal clock select. Internal clock when set to 1 |   |   |   |   |  |  |

| XI, XO               | _      | Connect to crystal oscillator                                   |                                                                                         |   |   |   |   |  |  |

| TEST1                | Input  | (Test)<br>Usually connected to V <sub>DD</sub>                  |                                                                                         |   |   |   |   |  |  |

| V <sub>DD</sub>      | _      | Power supply (5 V)                                              |                                                                                         |   |   |   |   |  |  |

| V <sub>SS</sub>      | _      | Power supply (0 V)                                              |                                                                                         |   |   |   |   |  |  |

Note 1: DSC1 = 0: LD3 / DSC0 = DSC0 (input)

- (a) DSC0 = 0 (1-bit mode)UD0: for dots in the upper areaLD0: for dots in the lower area

- (b) DSC0 = 1 (2-bit mode)

UD0: for even dots in the upper area

UD1: for odd dots in the upper area

- LD0: for even dots in the lower area

- LD1: for odd dots in the lower area

- Note 2: DSC1 = 1 (4-bit mode): LD3 / DSC0 = LD3 (output) UD0 to UD3: for dots in the upper area

- LD0 to LD3: for dots in the lower area

# **Description of Pins**

# • HR/LR

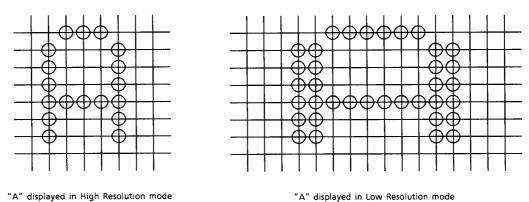

The HR / LR input is used to select either High Resolution mode or Low Resolution mode, in the LCD mode. The difference between the High Resolution mode and the Low Resolution mode is shown in the following diagram.

# • EXS

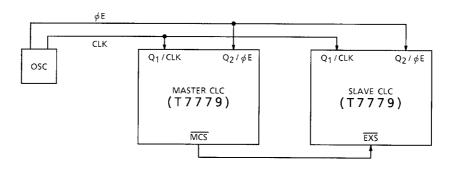

In Non–Interlace mode only, the  $\overline{\text{EXS}}$  input is used to synchronize the slave–CLC to the master–CLC.

#### • SET

The SET input is used to set the internal registers. In LCD mode, a high level on the SET input forces the internal registers into the following state:

|                 |                         | 2 ≤ N | r ≤ 31 | Nr = | 0 or 1 |

|-----------------|-------------------------|-------|--------|------|--------|

| Register No.    | Register Name           | LR    | HR     | LR   | HR     |

| R <sub>0</sub>  | Horizontal Total        | 47    | 87     | 47   | 87     |

| R <sub>1</sub>  | Horizontal Displayed    | *     | *      | *    | *      |

| R <sub>2</sub>  | H. Sync Position        | *     | *      | *    | *      |

| R <sub>3</sub>  | Sync Width              | *     | *      | *    | *      |

| R <sub>4</sub>  | Vertical Total          | 12    | 12     | 51   | 51     |

| R <sub>5</sub>  | V. Total Adjust         | 0     | 0      | 0    | 0      |

| R <sub>6</sub>  | Vertical Displayed      | 255   | 255    | 255  | 255    |

| R <sub>7</sub>  | V. Sync Position        | 255   | 255    | 255  | 255    |

| R <sub>8</sub>  | Interlace Mode and Skew | 0     | 0      | 0    | 0      |

| R <sub>9</sub>  | Max. Scan Line Address  | *     | *      | *    | *      |

| R <sub>10</sub> | Cursor Start            | *     | *      | *    | *      |

| R <sub>11</sub> | Cursor End              | *     | *      | *    | *      |

| R <sub>12</sub> | Start Address (H)       | *     | *      | *    | *      |

| R <sub>13</sub> | Start Address (L)       | *     | *      | *    | *      |

| R <sub>14</sub> | Cursor Address (H)      | *     | *      | *    | *      |

| R <sub>15</sub> | Cursor Address (L)      | *     | *      | *    | *      |

| R <sub>16</sub> | Light Pen (H)           | *     | *      | *    | *      |

| R <sub>17</sub> | Light Pen (L)           | *     | *      | *    | *      |

| R <sub>18</sub> | SCP Start Position      | 128   | 128    | 128  | 128    |

| R <sub>19</sub> | SCP End Position        | Nhd   | Nhd    | Nhd  | Nhd    |

| R <sub>20</sub> | Display Start Position  | 0     | 0      | 0    | 0      |

| R <sub>21</sub> | Display End Position    | Nhd   | Nhd    | Nhd  | Nhd    |

| R <sub>22</sub> | Additional Address (H)  | 2     | 4      | 8    | 8      |

| R <sub>23</sub> | Additional Address (L)  | 8     | 16     | 32   | 32     |

LR: Low Resolution mode

HR: High Resolution mode

\*: Does not change

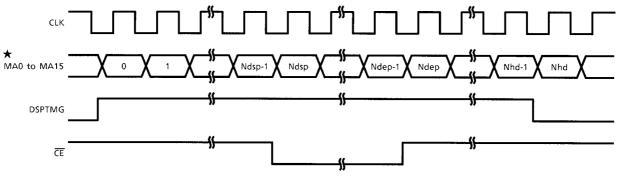

### • CE

The  $\overline{CE}$  output is a low-active signal which indicates the presence of a valid data address (d0 to d7, attribute) to the external logic

$\star$  The initial MA is determined by R<sub>12</sub>/R<sub>13</sub> (Start Address Register), which is zero in this timing example.

## **Built-in Registers**

Internal operation of the T7779 is determined by the value of the built–in registers. When you want to write to these registers, first you must write the control register address into the address register ( $R_S = 0$ ). Then you can write (or read) the value into (or from) the control register ( $R_S = 1$ ).

| CS | $R_S$ | Register         | Read | Write |

|----|-------|------------------|------|-------|

| 1  | _     | Invalid          | _    | _     |

| 0  | 0     | Address Register | ×    | 0     |

| 0  | 1     | Control Register | _    | _     |

| De sister No    | De sistes Norse           | 0)////       |                      |                |                | Data           | a Bit |   |   |   |

|-----------------|---------------------------|--------------|----------------------|----------------|----------------|----------------|-------|---|---|---|

| Register No.    | Register Name             | SYM.         | 7                    | 6              | 5              | 4              | 3     | 2 | 1 | 0 |

| R <sub>0</sub>  | Horizontal Total*         | Nht          |                      |                |                |                |       |   |   |   |

| R <sub>1</sub>  | Horizontal Displayed      | Nhd          |                      |                |                |                |       |   |   |   |

| R <sub>2</sub>  | Horizontal Sync Position* | Nhsp         |                      |                |                |                |       |   |   |   |

| R <sub>3</sub>  | Sync Width                | N∨sw<br>Nhsw | VW3 to VW0 HW3 to HW |                |                |                | o HW0 |   |   |   |

| R <sub>4</sub>  | Vertical Total*           | Nvt          |                      |                |                |                |       |   |   |   |

| R <sub>5</sub>  | Vertical Total Adjust     | Nadj         |                      | _              | _              |                |       |   |   |   |

| R <sub>6</sub>  | Vertical Displayed        | Nvd          |                      |                |                |                |       |   |   |   |

| R <sub>7</sub>  | Vertical Sync Position*   | Nvsp         |                      |                |                |                |       |   |   |   |

| R <sub>8</sub>  | Interlace Mode and Skew   |              | C <sub>1</sub>       | C <sub>0</sub> | D <sub>1</sub> | D <sub>0</sub> | -     | _ | V | S |

| R <sub>9</sub>  | Max Scan Line Address     | Nr           | —                    |                |                |                | •     |   | • |   |

| R <sub>10</sub> | Cursor Start              | Ncsr         | CUL                  | В              | Р              |                |       |   |   |   |

| R <sub>11</sub> | Cursor End                | Ncer         |                      | _              |                |                |       |   |   |   |

| De sister Ne    | De sister Norse        | 0)/04 | Data Bit |   |   |   |   |   |   |   |

|-----------------|------------------------|-------|----------|---|---|---|---|---|---|---|

| Register No.    | Register Name          | SYM.  | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| R <sub>12</sub> | Start Address (H)      |       |          |   |   |   |   |   |   |   |

| R <sub>13</sub> | Start Address (L)      |       |          |   |   |   |   |   |   |   |

| R <sub>14</sub> | Cursor Address (H)     |       |          |   |   |   |   |   |   |   |

| R <sub>15</sub> | Cursor Address (L)     |       |          |   |   |   |   |   |   |   |

| R <sub>16</sub> | Light Pen (H)          |       |          |   |   |   |   |   |   |   |

| R <sub>17</sub> | Light Pen (L)          |       |          | _ |   |   |   |   |   |   |

| R <sub>18</sub> | SCP Start Position     | Nssp  | SC       |   |   |   |   |   |   |   |

| R <sub>19</sub> | SCP End Position       | Nsep  |          |   |   |   |   |   |   |   |

| R <sub>20</sub> | Display Start Position | Ndsp  |          |   |   |   |   |   |   |   |

| R <sub>21</sub> | Display End Position   | Ndep  |          |   |   |   |   |   |   |   |

| R <sub>22</sub> | Additional Address (H) |       |          |   |   |   |   |   |   |   |

| R <sub>23</sub> | Additional Address (L) |       |          |   |   |   |   |   |   |   |

Note 1: Write Value of register marked by "\*"

(Write value) = (fixed value) -1

Note 2: Write Value of R9

• Non-Interlace mode ······ (Write Value Nr) = (Appointing value) - 1

Interlace Sync mode ..... (Write Value Nr) = (Appointing value) - 1

• Interlace Sync and Video mode (Write Value Nr) = (Appointing value) – 2

Note 3: For Interlace mode, the horizontal total register ( $R_0$ ) must be odd.

Note 4: Bits 0 to 3 of  $R_3$  determine the width of the horizontal sync. pulse.

Bits 4 to 7 of  $R_3$  determine the width of the vertical sync. pulse.

| Vw3 | Vw2 | Vw1 | Vw0 | Pulse Width |

|-----|-----|-----|-----|-------------|

| 0   | 0   | 0   | 0   | 16H         |

| 0   | 0   | 0   | 1   | 1           |

| 0   | 0   | 1   | 0   | 2           |

| 0   | 0   | 1   | 1   | 3           |

| 0   | 1   | 0   | 0   | 4           |

| 0   | 1   | 0   | 1   | 5           |

| 0   | 1   | 1   | 0   | 6           |

| 0   | 1   | 1   | 1   | 7           |

| 1   | 0   | 0   | 0   | 8           |

| 1   | 0   | 0   | 1   | 9           |

| 1   | 0   | 1   | 0   | 10          |

| 1   | 0   | 1   | 1   | 11          |

| 1   | 1   | 0   | 0   | 12          |

| 1   | 1   | 0   | 1   | 13          |

| 1   | 1   | 1   | 0   | 14          |

| 1   | 1   | 1   | 1   | 15          |

| Hw3 | Hw2 | Hw1 | Hw0 | Pulse Width |

|-----|-----|-----|-----|-------------|

| 0   | 0   | 0   | 0   | Don't care  |

| 0   | 0   | 0   | 1   | 1HC         |

| 0   | 0   | 1   | 0   | 2           |

| 0   | 0   | 1   | 1   | 3           |

| 0   | 1   | 0   | 0   | 4           |

| 0   | 1   | 0   | 1   | 5           |

| 0   | 1   | 1   | 0   | 6           |

| 0   | 1   | 1   | 1   | 7           |

| 1   | 0   | 0   | 0   | 8           |

| 1   | 0   | 0   | 1   | 9           |

| 1   | 0   | 1   | 0   | 10          |

| 1   | 0   | 1   | 1   | 11          |

| 1   | 1   | 0   | 0   | 12          |

| 1   | 1   | 0   | 1   | 13          |

| 1   | 1   | 1   | 0   | 14          |

| 1   | 1   | 1   | 1   | 15          |

H: Scan-line time

HC: Character time

Note 5: Bits 0 and 1 of  $R_8$  control the Interlace mode. Bits 4 and 5 of  $R_8$  control the DSPTMG skew. Bits 6 and 7 of  $R_8$  control the CUDISP skew.

| V | S | Raster-Scan Mode    |                     | D <sub>1</sub> | D <sub>0</sub> | Dsptmg Skew           | C <sub>1</sub> | C <sub>0</sub> | Cudisp Skew           |  |

|---|---|---------------------|---------------------|----------------|----------------|-----------------------|----------------|----------------|-----------------------|--|

| 0 | 0 | Non-Interlace Mode  | on-Interlace Mode 0 |                | 0              | No Character          | 0              | 0              | No Character          |  |

| 0 | 1 |                     |                     | 0              | Ũ              | Skew                  | •              | U              | Skew                  |  |

| 1 | 0 | Interlace Sync Mode |                     | 0              | 1              | One Character         | 0              | 1              | One Character         |  |

|   |   | Interlace Sync and  |                     | -              |                | Skew                  | -              |                | Skew                  |  |

| 1 | 1 | Video Mode          |                     | 1              | 0              | Two Character<br>Skew | 1              | 0              | Two Character<br>Skew |  |

|   |   |                     |                     | 1              | 1              | Not Available         | 1              | 1              | Not Available         |  |

Note 6: Bit 5 of R<sub>10</sub> is used for blink period control, bit 6 is used to select blink or non-blink, and Bit 7 is used to select the cursor display screen for the LCD.

| В | Ρ | Cursor Display Mode   |

|---|---|-----------------------|

| 0 | 0 | Non-Blink             |

| 0 | 1 | Cursor Non-Display    |

| 1 | 0 | Blink 1/16 Field Rate |

| 1 | 1 | Blink 1/32 Field Rate |

| CUL | Cursor Display Screen |

|-----|-----------------------|

| 0   | Upper Screen          |

| 1   | Lower Screen          |

Note 7: Bit 7 of  $R_{18}$  determines the number of the LCD screen.

| S <sub>C</sub> | Number of LCD Screen |

|----------------|----------------------|

| 0              | 1                    |

| 1              | 2                    |

#### • Address register

| Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3    | DB2   | DB1   | DB0 |

|----|-------|-----|-----|-----|-----|--------|-------|-------|-----|

| 0  | Write |     |     |     |     | REGIST | ER AD | DRESS |     |

This 5-bit write-only register contains the address of one of the other 24 registers. When you want to write or read one of the registers ( $R_0$  to  $R_{23}$ ), first you must write the address of the register in this register.

#### • Control register

Note:  $\nabla$  = CRT mode,  $\blacksquare$  = LCD mode

#### (1) Horizontal total register (R<sub>0</sub>)

| Rs | R/W   | DB7   | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-------|-------|-----|-----|-----|-----|-----|-----|-----|

| 1  | Write | Nht-1 |     |     |     |     |     |     |     |

$\bigtriangledown$  This 8-bit write-only register determines the horizontal sync. frequency. The value entered in this register should be one less than the total number of characters on one line.

▼ This 8-bit write-only register determines the non-displayed character times (retrace). If there is no retrace period, this LSI does not operate correctly. The retrace period is the difference between Nht + 1 and Nhd (= Nht + 1 - Nhd). Usually this value should be set to Nhd + 1. In 1 Character Skew mode, set the value to Nhd + 2. In 2 Character Skew mode, set the value to Nhd + 3.

#### (2) Horizontal displayed register (R1)

| Rs | R / W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | Write |     |     |     | Nł  | nd  |     |     |     |

$\nabla$  V This 8-bit write-only register determines the number of characters displayed per line. The contents of  $R_1$  must be less than the contents of  $R_0$  (Nhd < Nht).

#### (3) Horizontal sync. position register (R<sub>2</sub>)

| ſ | Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1  | Write |     |     |     | Nhs | p-1 |     |     |     |

$\bigtriangledown$  This 8-bit write-only register determines the horizontal sync. position. The value held in this register is one less than the computed number of characters.

▼ The horizontal sync. pulse is not necessary. However, you can use it if you wish.

### (4) Sync width register (R<sub>3</sub>)

| Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3  | DB2 | DB1 | DB0 |  |

|----|-------|-----|-----|-----|-----|------|-----|-----|-----|--|

| 1  | Write |     | Νv  | sw  |     | Nhsw |     |     |     |  |

$\nabla$  V This 8-bit write-only register determines the width of the vertical and horizontal sync. pulses.

When Nvsw = 1 to 15, pulse width = 1 to 15H (H: time to scan 1 line)

When Nvsw = 0, pulse width = 16 H

When Nhsw = 1 to 15, pulse width = 1 to 15HC (HC: time to scan 1 character) When Nhsw = 0, don't care.

### (5) Vertical total register (R<sub>4</sub>)

| Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | Write |     |     |     | Nv  | t-1 |     |     |     |

$\bigtriangledown$  This 8-bit write-only register determines the vertical sync. frequency. The value entered in this register is one less than the number of lines of characters.

▼ This 8-bit write-only register determines the number of rows displayed on the screen. The value held in the register is one less than the number of lines of characters.

### (6) Vertical total adjust register (R<sub>5</sub>)

| Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2  | DB1 | DB0 |

|----|-------|-----|-----|-----|-----|-----|------|-----|-----|

| 1  | Write |     |     |     |     |     | Nadj |     |     |

$\bigtriangledown$  This 5–bit write–only register adjusts the total number of scan lines per frame.

▼ Usually set to 0.

#### (7) Vertical displayed register (R<sub>6</sub>)

| Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | Write |     |     |     | N١  | /d  |     |     |     |

$\bigtriangledown$  This 8-bit write-only register determines the number of character rows displayed on the screen. The contents of R6 is less than the contents of R4 (Nvd < Nvt).

▼ The contents of  $R_6$  must be more than the contents of  $R_4$  (Nvd > Nvt). Usually set to FF (Hex).

### (8) Vertical sync. position register (R7)

| Γ | Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 1  | Write |     |     |     | Nvs | p-1 |     |     |     |

$\nabla$  This 8-bit write-only register determines the vertical sync. position. The value entered in this register is one less than the computed number of character lines.

▼ The vertical sync. pulse is not necessary. However, you can use it if you wish.

#### (9) Interlace mode and skew register ( $R_8$ )

| Rs | R/W   | DB7            | DB6            | DB5            | DB4            | DB3 | DB2 | DB1 | DB0 |

|----|-------|----------------|----------------|----------------|----------------|-----|-----|-----|-----|

| 1  | Write | Ċ <sub>1</sub> | C <sub>0</sub> | D <sub>1</sub> | D <sub>0</sub> |     |     | V   | S   |

| V | s | INTERLACE MODE                | D <sub>1</sub> | Do | DSPTMG            | C1 | c <sub>0</sub> | CUDISP            |

|---|---|-------------------------------|----------------|----|-------------------|----|----------------|-------------------|

| 0 | 0 | Non-Interlace Mode            | 0              | 0  | No Character Skew | 0  | 0              | No Character Skew |

| 0 | 1 |                               | 0              | 1  | 1-Character Skew  | 0  | 1              | 1-Character Skew  |

| 1 | 0 | Interlace Sync Mode           | 1              | 0  | 2-Character Skew  | 1  | 0              | 2-Character Skew  |

| 1 | 1 | Interlace Sync and Video Mode | 1              | 1  | Not Available     | 1  | 1              | Not Available     |

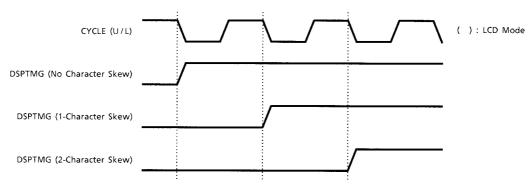

$\bigtriangledown$  Interlace modes are selected using the two low order bits of this 6-bit write-only register. DSPTMG skew is controlled by bits 4 and 5 of R<sub>8</sub>. CUDISP skew is controlled by bits 6 and 7 of R<sub>8</sub>.

$\blacktriangledown$  Non–Interlace mode only is available. The skew function is the same as for CRT mode.

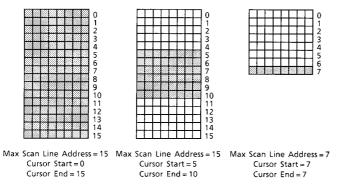

#### (10) Max scan line address register (R<sub>9</sub>)

| Rs | R/W     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2  | DB1 | DB0 |

|----|---------|-----|-----|-----|-----|-----|------|-----|-----|

| 1  | (Write) |     |     |     |     |     | Nr-1 |     |     |

▽ This 5-bit write-only register determines the number of scan lines per character row. In Non-Interlace or Interlace Sync mode, the value programmed in the register is one less than the number of scan lines. In Interlace Sync and Video mode, the value is two less than the number of scan lines.

▼ This 5-bit write-only register determines the number of horizontal dots per character row. The value is one less than the number of horizontal dots.

### (11) Cursor start register (R10)

| RS | R/W   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2  | DB1 | DB0 |

|----|-------|-----|-----|-----|-----|-----|------|-----|-----|

| 1  | Write | CUL | В   | Р   |     |     | Ncsr |     |     |

- $\nabla$  This register determines the start scan line of the cursor and the cursor display mode. Bits 0 to 4 of R10 determine the start scan line of the cursor. Bits 5 and 6 (P, B) of R10 determine the cursor display mode.

- ▼ In LCD 2-screen mode, bit 7 of R<sub>10</sub> determines the cursor display screen. If you want to program the cursor position anywhere in the lower screen, bit 7 of R<sub>10</sub> must be set to 1.

### (12) Cursor end register ( $R_{11}$ )

| Rs | R/W   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2  | DB1 | DB0 |

|----|-------|-----|-----|-----|-----|-----|------|-----|-----|

| 1  | Write |     |     |     |     |     | Ncer |     |     |

$\bigtriangledown \blacksquare$  This 5–bit write–only register determines the last scan line of cursor.

| В | Р | CURSOR DISPLAY MODE   |

|---|---|-----------------------|

| 0 | 0 | Non-Blink             |

| 0 | 1 | Non-Display           |

| 1 | 0 | Blink 1/16 Field Rate |

| 1 | 1 | Blink 1/32 Field Rate |

(13) Start address register (R<sub>12</sub>, R<sub>13</sub>)

| Rs | R / W | DB7 | DB6                               | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|----|-------|-----|-----------------------------------|-----|-----|-----|-----|-----|-----|--|

| 1  | R/W   |     | START ADDRESS (H)-R <sub>12</sub> |     |     |     |     |     |     |  |

| 1  | R/W   |     | START ADDRESS (L)-R <sub>13</sub> |     |     |     |     |     |     |  |

▽▼ This 16-bit read / write register pair determines the memory address corresponding to the first line on the screen. Hardware scrolling by line or page may be accomplished by modifying the contents of this register.

#### (14) Cursor address register (R<sub>14</sub>, R<sub>15</sub>)

| RS | R/W | DB7 | DB6                                | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|----|-----|-----|------------------------------------|-----|-----|-----|-----|-----|-----|--|

| 1  | R/W |     | CURSOR ADDRESS (H)-R <sub>14</sub> |     |     |     |     |     |     |  |

| 1  | R/W |     | CURSOR ADDRESS (L)-R <sub>15</sub> |     |     |     |     |     |     |  |

$\bigtriangledown$  This 16–bit read / write register pair determines the cursor display address.

▼ The built-in address counter generates only upper screen addresses. If you want to program the cursor position anywhere in the lower screen, this register pair must be programmed with the upper screen address corresponding to the lower screen address.

#### (15) Light pen register (R<sub>16</sub>, R<sub>17</sub>)

| RS | R / W | DB7 | DB6                                   | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |  |

|----|-------|-----|---------------------------------------|-----|-----|-----|-----|-----|-----|--|--|

| 1  | Read  |     | LIGHT PEN ADDRESS (H)-R <sub>16</sub> |     |     |     |     |     |     |  |  |

| 1  | Read  |     | LIGHT PEN ADDRESS (L)-R <sub>17</sub> |     |     |     |     |     |     |  |  |

$\bigtriangledown$  This 16-bit read–only register pair captures the refresh address on the positive edge of LPSTB.

#### (16) SCP start position register (R<sub>18</sub>)

| Rs | R/W | DB7 | DB6 | DB5 | DB4 | DB3  | DB2 | DB1 | DB0 |                                             |

|----|-----|-----|-----|-----|-----|------|-----|-----|-----|---------------------------------------------|

| 1  | R/W | SC  |     |     |     | Nssp |     |     |     | $S_C = 0 : 1$ screen, $S_C = 1 : 2$ screens |

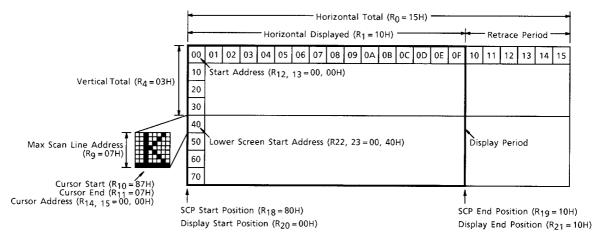

▼ This 8-bit read / write register determines the SCP (Shift Clock Pulse) start position. The value held in bits 0 to 6 of this register is one less than the computed number of characters. This value is set to 0. Bit 7 of R<sub>18</sub> determines the number of LCD screens.

#### (17) SCP end position register (R<sub>19</sub>)

| Rs | R/W | DB7  | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|------|-----|-----|-----|-----|-----|-----|-----|

| 1  | R/W | Nsep |     |     |     |     |     |     |     |

▼ This 8-bit read / write register determines the SCP end position. The value held in the register is one less than the computed number of characters. This register is usually set to the same value as R<sub>1</sub>.

#### (18) Display start position register (R<sub>20</sub>)

| Rs | R/W | DB7 | DB6  | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|------|-----|-----|-----|-----|-----|-----|

| 1. | R/W |     | Ndsp |     |     |     |     |     |     |

∇ ▼ This 8-bit read / write register determines the display start position. The value held in the register is one less than the computed number of characters. The register is usually set to 0.

#### (19) Display end position register (R<sub>21</sub>)

| Rs | R/W | DB7 | DB6  | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|----|-----|-----|------|-----|-----|-----|-----|-----|-----|--|

| 1  | R/W |     | Ndep |     |     |     |     |     |     |  |

$\nabla \mathbf{V}$  This 8-bit read / write register determines the display end position. The value held in the register is one less than the computed number of characters. This register is usually set to the same value as  $R_1$ .

#### (20) Additional address register (R<sub>22</sub>, R<sub>23</sub>)

| Rs | R/W | DB7 | DB6                                    | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |  |

|----|-----|-----|----------------------------------------|-----|-----|-----|-----|-----|-----|--|--|

| 1  | R/W |     | ADDITIONAL ADDRESS (H)-R22             |     |     |     |     |     |     |  |  |

| 1  | R/W |     | ADDITIONAL ADDRESS (L)-R <sub>23</sub> |     |     |     |     |     |     |  |  |

▼ The built-in address counter generates only upper screen addresses. The T7779 adds the contents of this 16-bit register pair to the address counter value to form the lower screen address.

### **Function Description**

#### • Register functions

#### (1) An example of register values

An example of register values in LCD 2-Screen mode is shown below

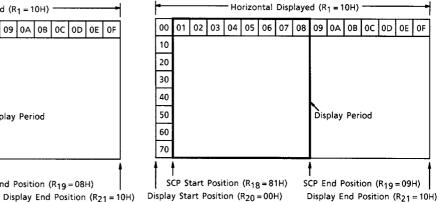

#### (2) Horizontal scroll function (LCD mode)

Hardware horizontal character scrolling may be accomplished by modifying the contents of the SCP start position register (R<sub>18</sub>) and SCP end position register (R<sub>19</sub>).

|   | ┝ <b>ҹ</b> ──     |      |       |       | - Но | rizo              | ntal | Disp | laye | d (R | 1 = 1 | 0H)  |     |       |                 |       |     | ŀ   | •    |       |      |

|---|-------------------|------|-------|-------|------|-------------------|------|------|------|------|-------|------|-----|-------|-----------------|-------|-----|-----|------|-------|------|

|   | 00                | 01   | 02    | 03    | 04   | 05                | 06   | 07   | 08   | 09   | 0A    | 0B   | 0C  | 0D    | 0E              | 0F    |     | [   | 00   | 01    | 02   |

|   | 10                |      |       |       |      |                   |      |      |      |      |       |      |     |       |                 |       |     |     | 10   |       |      |

|   | 20                |      |       |       |      |                   |      |      |      |      |       |      |     |       |                 |       |     |     | 20   |       |      |

|   | 30                |      |       |       |      |                   |      |      |      |      |       |      |     |       |                 |       |     |     | 30   |       |      |

|   | 40                |      |       |       |      |                   |      |      |      |      |       |      |     |       |                 |       |     |     | 40   |       |      |

|   | 50                |      |       |       |      |                   |      |      | Dis  | play | Peri  | od   |     |       |                 |       |     | [   | 50   |       |      |

|   | 60                |      |       |       |      |                   |      |      |      |      |       |      |     |       |                 |       |     | [   | 60   |       |      |

|   | 70                |      |       |       |      |                   |      |      |      |      |       |      |     |       |                 |       |     |     | 70   |       |      |

|   | ł                 |      |       |       |      |                   |      |      |      |      |       |      |     |       |                 |       |     | ł   |      |       |      |

| S | CP S <sup>.</sup> | tart | Posi  | tion  | (R18 | 3 = 80            | 0H)  | S    | Ср е | nd P | ositi | on ( | R19 | = 08  | H)              |       |     |     | S    | CP S  | tart |

| D | ispla             | y St | art F | Posit | ion  | (R <sub>2</sub> 0 | = 00 | H)   |      | Disp | olay  | End  | Pos | ition | (R <sub>2</sub> | 1 = 1 | 0H) | Dis | spla | / Sta | art  |

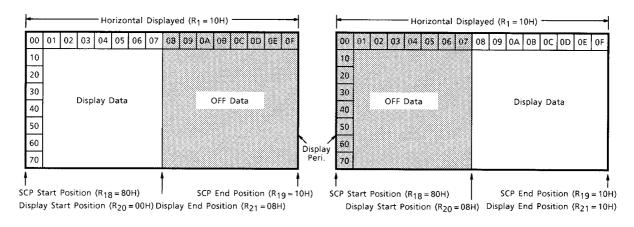

#### (3) Mask function

Hardware character masking may be accomplished by modifying the contents of the display start position register ( $R_{20}$ ) and display end position register ( $R_{21}$ ). This function is useful for the multicontroller system.

#### (4) Vertical scroll function

Hardware vertical scrolling by line or by page may be accomplished by modifying the contents of the start address register  $(R_{12, 13})$  without modifying the contents of refresh memory.

| Horizontal Displayed (R1 = 10H)                  | 1       | <b> </b> |         |       | — н   | orizo             | ontal | Dis   | playe | ed (F | R <sub>1</sub> = 1 | 0H) |    |    |    |    |

|--------------------------------------------------|---------|----------|---------|-------|-------|-------------------|-------|-------|-------|-------|--------------------|-----|----|----|----|----|

| 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F  | ]       | 00       | 01 02   | 03    | 04    | 05                | 06    | 07    | 08    | 09    | 0A                 | 0B  | 0C | 0D | 0E | 0F |

| 10 Start Address (R <sub>12, 13</sub> = 00, 00H) |         | 10       |         |       |       |                   |       |       |       |       |                    |     |    |    |    |    |

| 20                                               |         | 20       | Start # | ٩ddre | ess ( | R <sub>12</sub> , | 13=   | = 00, | 10H   | )     |                    |     |    |    |    |    |

| 30                                               | Display | 30       |         |       |       |                   |       |       |       |       |                    |     |    |    |    |    |

| 40                                               | Peri.   | 40       |         |       |       |                   |       |       |       |       |                    |     |    |    |    |    |

| 50                                               |         | 50       |         |       |       |                   |       |       |       |       |                    |     |    |    |    |    |

| 60                                               |         | 60       |         |       |       |                   |       |       |       |       |                    |     |    |    |    |    |

| 70                                               |         | 70       |         |       |       |                   |       |       |       |       |                    |     |    |    |    |    |

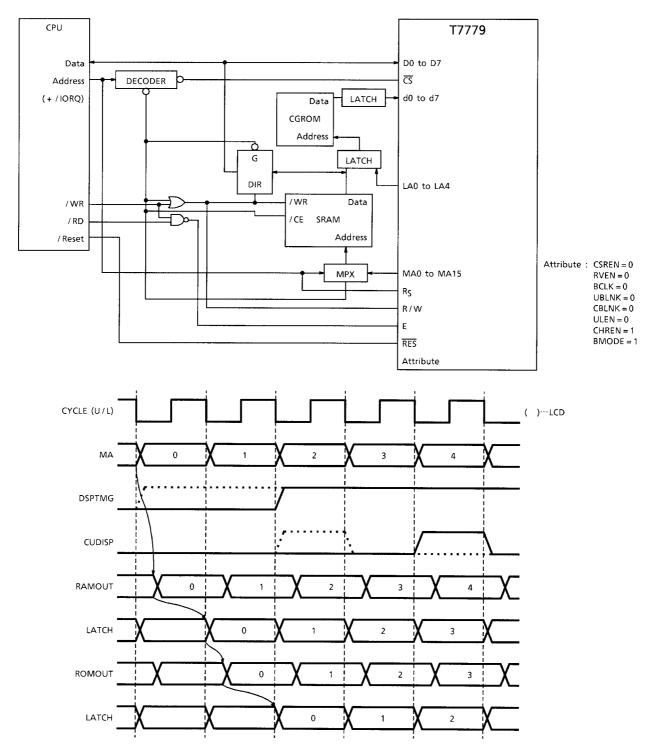

#### (5) Skew function

If the memory access cycle and the data latch are not synchronized to each other, this function must be used.

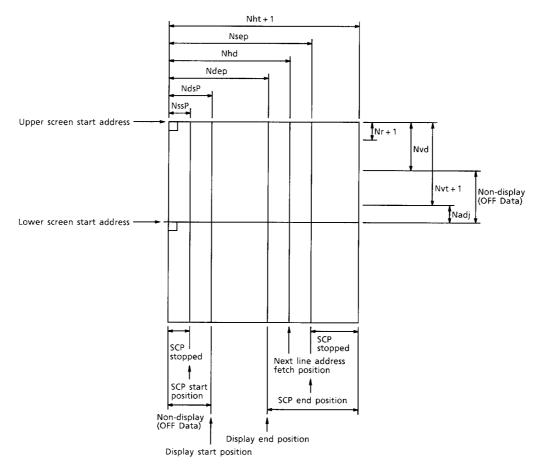

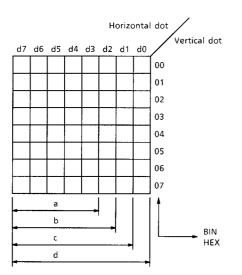

#### Screen Format

• Relationship between memory address (LA0 to LA4) and memory data (d0 to d7) The addresses of vertical dots are in hex. format.

| а | : | Valid | data | when | these | are | 5 | hor | rizonta | dots | (HS0 = 0 | , HS1 | = 0) |

|---|---|-------|------|------|-------|-----|---|-----|---------|------|----------|-------|------|

|   |   |       |      |      |       |     |   |     |         |      |          |       |      |

- b : Valid data when these are 6 horizontal dots (HS0 = 1, HS1 = 0)

- $c\,$  : Valid data when these are 7 horizontal dots (HS0 = 0, HS1 = 1) d : Valid data when these are 8 horizontal dots (HS0 = 1, HS1 = 1)

EX.) When address is 07H

| LA4 | LA3 | LA2 | LA1 | LA0 |  |  |  |  |  |  |

|-----|-----|-----|-----|-----|--|--|--|--|--|--|

| 0   | 0   | 1   | 1   | 1   |  |  |  |  |  |  |

| 0   | 7   |     |     |     |  |  |  |  |  |  |

• Relationship between the display screen and memory addresses (MA0 to MA15, LA0 to LA4)

| $\setminus$ ( | HAR-       |      |        |               |              |       |           |              |

|---------------|------------|------|--------|---------------|--------------|-------|-----------|--------------|

| \             | ACTER      |      | Displa | ay period     |              | Retra | ce period |              |

| LINE          | LA         | - 1  | 2      |               | 80           | 81    |           |              |

|               | 000        | 0000 | 0001   | $\rightarrow$ | 004F         | 0050  |           | <b>] T</b>   |

|               | 001        | 0000 | 0001   | $\rightarrow$ | 004F         | 0050  |           |              |

|               | 010        |      |        |               |              |       |           |              |

| 1             | 011        |      |        |               |              |       |           | -            |

|               | 100        |      |        |               |              |       |           | 4            |

|               | 101<br>110 | ,    |        |               |              |       |           | -            |

|               | 111        | 0000 | 0001   | $\rightarrow$ | 004F         | 0050  |           | -            |

|               | 000        | 0050 | 0051   | $\rightarrow$ | 0041<br>009F | 0030  |           | 4 1          |

|               |            |      |        |               |              | 00/10 |           | 4            |

| 2             |            |      |        |               |              |       |           | Upper screen |

| 2             |            |      |        |               |              |       |           |              |

|               |            |      |        |               |              |       |           |              |

|               | 111        | 0050 | 0051   | $\rightarrow$ | 009F         | 00A0  |           |              |

| ↓             |            |      | ↓ ↓    |               |              |       |           |              |

|               | 000        | 03C0 | 03C1   | →             | 040F         | 0410  |           |              |

|               |            |      |        |               |              |       |           |              |

| 13            |            |      |        |               |              |       |           |              |

|               |            |      |        |               |              |       |           |              |

|               | 111        | 03C0 | 03C1   | $\rightarrow$ | 040F         | 0410  |           | -            |

| <del></del>   | 000        | 0410 | 0411   | >             | 0401<br>045F | 0410  |           | ┨╾╂          |

|               |            |      |        |               |              | 0.00  |           |              |

|               |            |      |        |               |              |       |           |              |

| 14            |            |      |        |               |              |       |           |              |

|               |            |      |        |               |              |       |           |              |

|               | 111        | 0410 | 0411   | $\rightarrow$ | 045F         | 0460  |           | ]            |

|               |            | ↓    | ↓      |               |              |       |           | Lower screen |

|               | 000        | 0780 | 0781   | →<br>         | 07CF         | 07D0  |           |              |

|               |            |      |        |               |              |       |           |              |

| 25            |            |      |        |               |              |       |           |              |

|               |            |      |        |               |              |       |           |              |

|               | 111        | 0780 | 0781   | $\rightarrow$ | 07CF         | 07D0  |           |              |

Note: State address: 0000H LCD lower screen additional address: 0410H Nr (maximum raster address): 07H 80 characters × 13 lines × 2 screens

## • Operating Modes

The T7779 has two operating modes; CRT mode and LCD mode. LCD mode is further subdivided into 1-Screen mode, 2-Screen mode, High Resolution mode and Low Resolution mode.

#### (1) CRT mode

When CRT / LCD = 0, the T7779 operates in CRT mode. The T7779 consists of a CRT controller and LCD interface circuit. In CRT mode, the T7779 uses the CRT controller circuit only. When the T7779 is operating in CRT mode, you can use the parallel-to-serial circuit that is included in the LCD interface circuit. However, when you have to operate the P / S circuit at more than 18 MHz, you cannot use the built-in P / S circuit.

#### (2) LCD mode

When CRT / LCD = 1, the T7779 operates in LCD mode. When the T7779 is operating in LCD mode, the CRT controller circuit generates only upper screen addresses.

#### a) 2- Screen mode

When the T7779 is operating in LCD mode, the cycle time of the built-in address counter is twice that when the T7779 is operating in CRT mode. In 2–Screen mode ( $R_{18}$ -bit 7 = 1), the T7779 generates the lower screen address by adding the built-in address counter value and the contents of  $R_{22}$ ,  $R_{23}$ . When U / L = L, the upper screen address is sent out from the MA0 to MA15 pins. When U / L = H, the lower screen address is sent out from the MA0 to MA15 pins. When U / L = H, the lower screen address is sent out from the MA0 to MA15 pins. In this case, however, the LA0 to LA4 outputs do not change. So it is impossible to set a row that extends from the upper screen to the lower screen. The cycle time of the U / L-signal is twice as long as that of the CYCLE-signal. The CYCLE-signal is L in the first half of the U / L-signal, and H in the second half of the U / L-signal. If the CPU accesses the display memory when CYCLE = L, you can rewrite the display memory without disturbing the display.

#### b) 1- Screen mode

When the T7779 is operating in LCD mode, the cycle time of the built–in address counter is twice that when the T7779 is operating in CRT mode. In 1–Screen mode ( $R_{18}$ –bit 7 = 0), the upper screen address is sent out from MA0 to MA15 pins during the cycle time of the U / L–signal. The CYCLE–signal is sent out using the same timing as in 2–Screen mode.

c) High Resolution mode

High Resolution mode is usually set (HR / LR = 1).

#### d) Low Resolution mode

In Low Resolution mode (HR / LR = 0), each horizontal dot is displayed twice. When the total of horizontal dots = 640 and the number of horizontal dots per character = 8, 80-characters are displayed in High Resolution mode and 40-characters are displayed in Low Resolution mode. When you change the High Resolution / Low Resolution mode setting, you must change not only the HR / LR pin but also the contents of the built-in registers to match 40-character display.

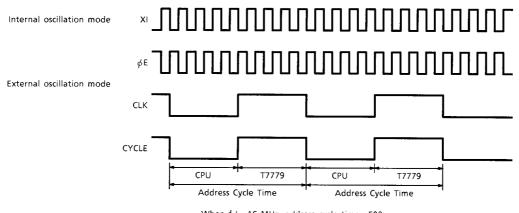

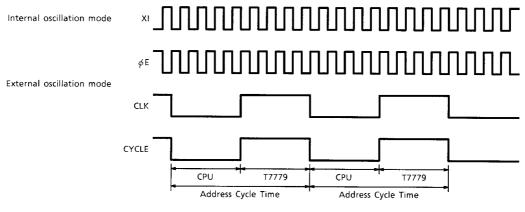

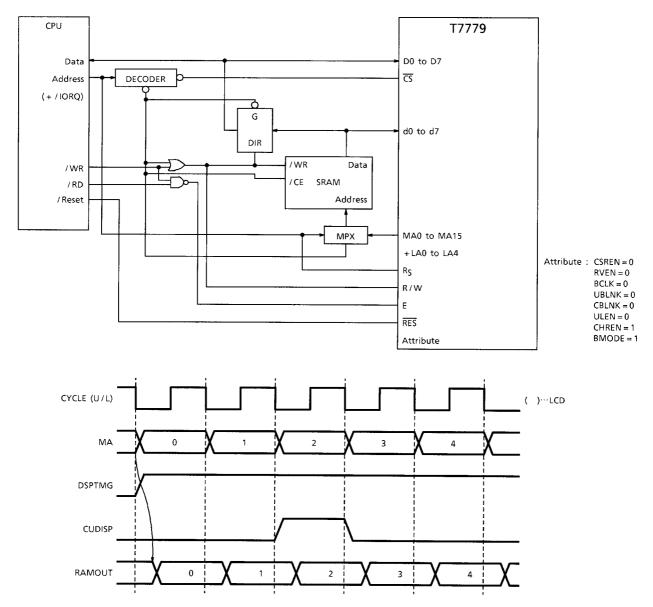

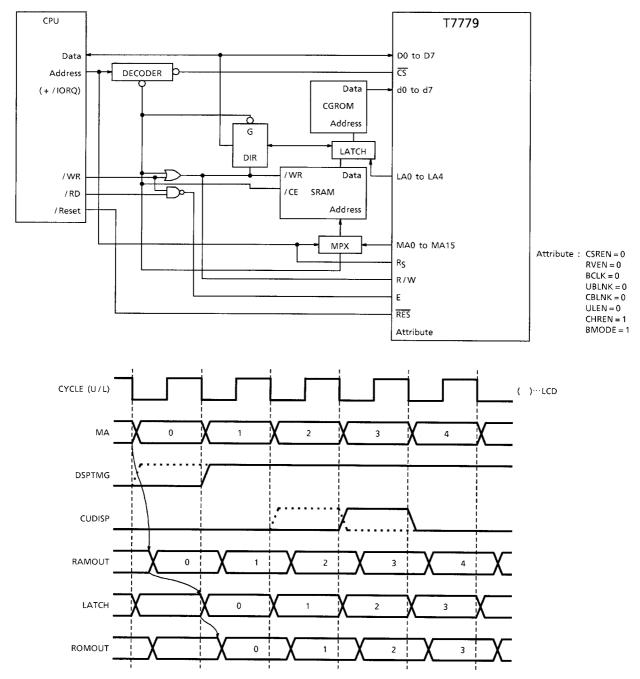

#### Memory Interface

If the CPU accesses the memory while the T7779 is accessing the memory, the display will be disturbed. There are two methods for rewriting the display memory without disturbing the display. One is to rewrite the display memory during the retrace period (DSPTMG = L). The other is to rewrite the display memory while CYCLE = L. A detailed explanation of the second case is shown below.

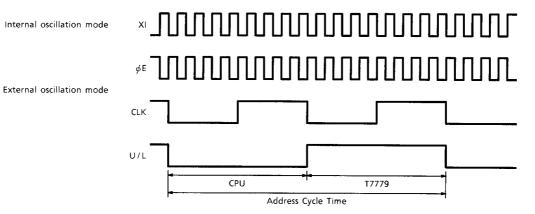

#### (1) Interface for CRT mode

The interface circuit must be constructed so that the CPU can access the memory when CYCLE = L.

When  $f\phi$  = 16 MHz, address cycle time = 500 ns

#### (2) Interface for LCD 2-Screen mode

The interface circuit must be constructed so that the CPU can access the memory when CYCLE = L.

When f  $\phi$  = 16 MHz, address cycle time = 500 ns

#### (3) Interface for LCD 1–Screen mode

The interface circuit must be constructed so that the CPU can access the memory when U /  $\rm L$  = L.

When  $f\phi = 16$  MHz, address cycle time = 1000 ns

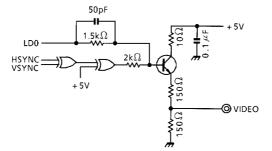

Monitor Interface

# (1) CRT (NTSC)

The resistance-mixing circuit generates a monochrome composite signal.

### (2) LCD

You can connect the T7779 (directly or through a CMOS buffer) to various types of LCD module that are on the market, and make various settings, such as 1 or 2 screens, the number of data bus lines, the number of horizontal dots and the duty.

The relation between data transmission, the shift clock and latch pulse is as shown below. The shift clock frequency becomes low as the number of data lines increases. Hence it is useful for the low power system.

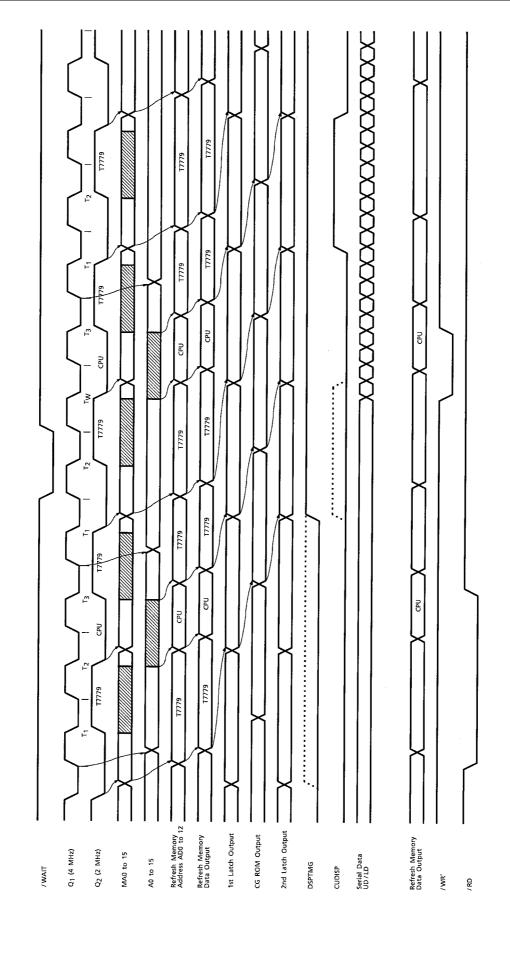

#### • Timing Chart (I) (HR / LR = 1: High Resolution mode)

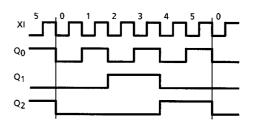

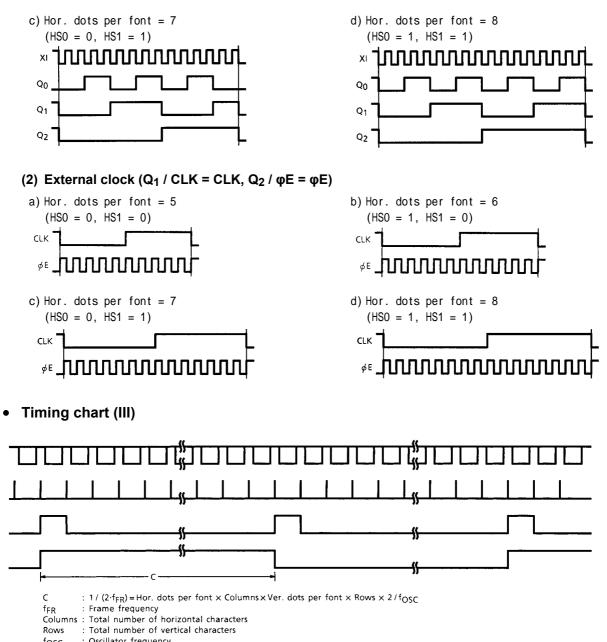

#### (1) Internal clock ( $Q_1$ / CLK = $Q_1$ , $Q_2$ / $\phi E = Q_2$ )

b) Hor. dots per font = 6 (HSO = 1, HS1 = 0)

- c) Hor. dots per font = 7 (HSO = 0, HS1 = 1)  $x_1 = \frac{5}{2} + \frac{9}{2} + \frac{1}{2} + \frac{2}{3} + \frac{3}{4} + \frac{5}{5} + \frac{9}{4} + \frac{5}{4} + \frac{1}{4} + \frac{1$

- d) Hor. dots per font = 8 (HSO = 1, HS1 = 1)

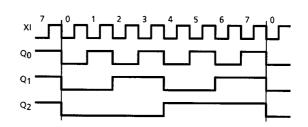

- (2) External clock (Q<sub>1</sub> / CLK = CLK, Q<sub>2</sub> / $\phi$ E =  $\phi$ E)

- a) Hor. dots per font = 5 (HSO = 0, HS1 = 0)  $CLK = \frac{4}{\phi E} = \frac{1}{2} \frac{1}{2} \frac{3}{4} \frac{4}{0} \frac{1}{4} \frac{1}{2} \frac{3}{4} \frac{4}{1} \frac{1}{4} \frac{1}{$

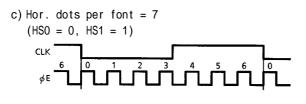

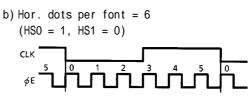

### • Timing Chart (II) (HR / LR=0: Low Resolution mode)

#### (1) Internal clock (Q<sub>1</sub> / CLK=Q<sub>1</sub>, Q<sub>2</sub> / $\phi$ E = Q<sub>2</sub>)

b) Hor. dots per font = 6 (HSO = 1, HS1 = 0)

- fosc : Oscillator frequency

- $f_{OSC} = f \phi = 2 \cdot SCP$  (1-bit mode)

- = 4-SCP (2-bit mode) = 8.SCP (4-bit mode)

T7779

### Absolute Maximum Ratings (Ta = 25°C)

| Item                  | Symbol                 | Rating                       | Unit |

|-----------------------|------------------------|------------------------------|------|

| Supply Voltage        | V <sub>DD</sub> (Note) | -0.3 to 7.0                  | V    |

| Input Voltage         | V <sub>IN</sub> (Note) | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Operating Temperature | T <sub>opr</sub>       | -20 to 75                    | °C   |

| Storage Temperature   | T <sub>stg</sub>       | -55 to 125                   | °C   |

Note: Referenced to V<sub>SS</sub> = 0 V

#### Electrical Characteristics DC Characteristics Test Conditions (Unless otherwise noted, $V_{SS} = 0V$ , $V_{DD} = 5.0 V \pm 10\%$ , Ta = -20 to 75°C)

| Iter        | n                  | Symbol          | Test<br>Circuit | Test Condition                             | Min                      | Тур. | Max             | Unit     |          |

|-------------|--------------------|-----------------|-----------------|--------------------------------------------|--------------------------|------|-----------------|----------|----------|

| Operating V | oltage             | V <sub>DD</sub> | —               | —                                          | 4.5                      | 5.0  | 5.5             | V        | —        |

| Input       | H <sub>Level</sub> | VIH             | _               | _                                          | V <sub>DD</sub><br>- 0.8 | _    | V <sub>DD</sub> | V        | (Note 1) |

| Voltage     | L <sub>Level</sub> | V <sub>IL</sub> | -               | —                                          | 0                        | _    | 0.8             | V        | (Note 1) |

| Input       | H <sub>Level</sub> | V <sub>IH</sub> | _               | _                                          | 2.2                      | _    | V <sub>DD</sub> | V        | (Note 2) |

| Voltage     | L <sub>Level</sub> | V <sub>IL</sub> | _               | —                                          | - 0 - 0.8                | 0.8  | V               | (Note 2) |          |

| Output      | H <sub>Level</sub> | V <sub>OH</sub> | _               | —                                          | V <sub>DD</sub><br>- 0.3 | _    | V <sub>DD</sub> | V        | —        |

| Voltage     | L <sub>Level</sub> | V <sub>OL</sub> | _               | —                                          | 0                        |      | 0.3             | V        | —        |

| Output      | H <sub>Level</sub> | R <sub>OH</sub> | _               | V <sub>OUT</sub> = V <sub>DD</sub> – 0.5 V | _                        | _    | 400             | Ω        | -        |

| Resistance  | L <sub>Level</sub> | R <sub>OL</sub> | _               | V <sub>OUT</sub> = 0.5 V                   | _                        | _    | 400             | Ω        | -        |

| Operating E | roquonov           | fφ              | _               | —                                          | _                        | —    | 18              | MHz      | (Note 3) |

| Operating F | requency           | fCLK            | _               | —                                          | _                        | —    | 4.0             | MHz      | (Note 4) |

| Current Con | sumption           | I <sub>DD</sub> | _               | V <sub>DD</sub> = 5.0 V                    | _                        | 4.0  | 6.0             | mA       | (Note 5) |

Note 1: Applied to EXT / INT, HS0, HS1, LD3 / DSC0, DSC1, TEST1

Note 2: Applied to inputs other than those marked Note 1:

Note 3: Applied to  $Q_2 / \phi E$

Note 4: Applied to Q<sub>1</sub> / CLK

Note 5: LCD, High Resolution, 2–bit transfer, 8 dots / font  $640 \times 104 \times 2$  screens, f $\phi$  = 9 MHz

# **AC Characteristics**

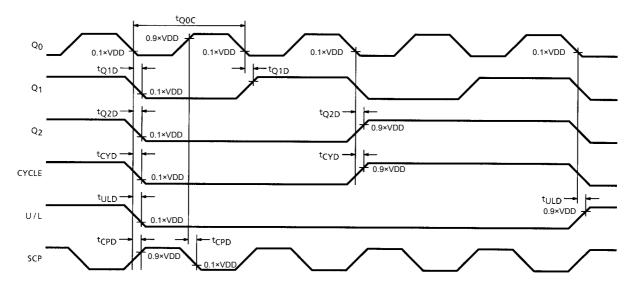

• CRT / LCD = 1 (LCD mode), EXT / INT = 1 (Internal clock)

### Test Conditions (Unless Otherwise Noted, $V_{SS} = 0 V$ , $V_{DD} = 5.0 V \pm 10\%$ , Ta = -20 to 75°C)

| Item                      | Symbol           | Test Conditions | Min | Max | Unit |

|---------------------------|------------------|-----------------|-----|-----|------|

| Q <sub>0</sub> Cycle Time | tQOC             | —               | 111 | —   | ns   |

| Q <sub>1</sub> Delay Time | t <sub>Q1D</sub> | —               | _   | 20  | ns   |

| Q <sub>2</sub> Delay Time | t <sub>Q2D</sub> | —               | -   | 20  | ns   |

| CYCLE Delay Time          | tCYD             | —               | -   | 20  | ns   |

| U / L Delay Time          | t <sub>ULD</sub> | _               | -   | 20  | ns   |

| SCP Delay Time            | t <sub>CPD</sub> | _               | _   | 10  | ns   |

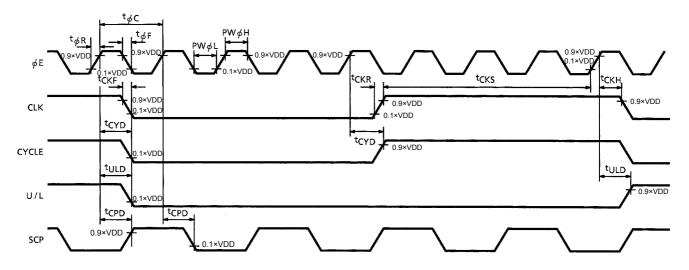

### • CRT / LCD = 1 (LCD mode), EXT / INT = 0 (External clock)

### Test Conditions (Unless Otherwise Noted, $V_{SS} = 0 V$ , $V_{DD} = 5.0 V \pm 10\%$ , Ta = -20 to 75°C)

| Item                   | Symbol                              | Test Conditions | Min  | Max | Unit |

|------------------------|-------------------------------------|-----------------|------|-----|------|

| φE Cycle Time          | tφ <sub>C</sub>                     | —               | 55.5 | _   | ns   |

| φE 1 Pulse Width       | Ρ₩φΗ                                | —               | 7.75 | _   | ns   |

| φE 0 Pulse Width       | PWφL                                | —               | 7.75 | _   | ns   |

| φE Rise and Fall Time  | tφ <sub>R</sub> , tφ <sub>F</sub>   | _               | _    | 20  | ns   |

| CLK Rise and Fall Time | t <sub>CKR</sub> , t <sub>CKF</sub> | —               | _    | 20  | ns   |

| CLK Set-up Time        | tcks                                | —               | 80   | _   | ns   |

| CLK Hold Time          | tскн                                | —               | 10   | _   | ns   |

| CYCLE Delay Time       | tCYD                                | —               | _    | 80  | ns   |

| U / L Delay Time       | tULD                                | —               | _    | 80  | ns   |

| SCP Delay Time         | t <sub>CPD</sub>                    | —               | _    | 80  | ns   |

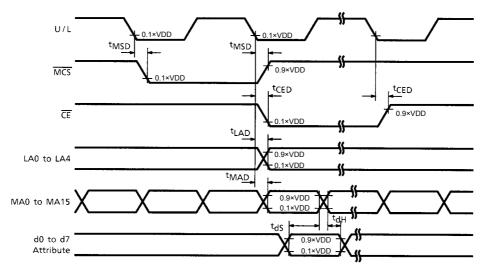

### • CRT / LCD = 1 (LCD mode)

### Test Conditions (Unless Otherwise Noted, $V_{SS} = 0 V$ , $V_{DD} = 5.0 V \pm 10\%$ , Ta = -20 to 75°C)

| Item             | Symbol           | Test Conditions          | Min | Max | Unit |

|------------------|------------------|--------------------------|-----|-----|------|

| MCS Delay Time   | t <sub>MSD</sub> | —                        |     | 80  | ns   |

| CE Delay Time    | tCED             | —                        | _   | 100 | ns   |

| LA Delay Time    | tLAD             | —                        | _   | 70  | ns   |

| MA Delay Time    | t <sub>MAD</sub> | —                        | _   | 50  | ns   |

| Data Set-up Time | t <sub>dS</sub>  | f <sub>OSC</sub> = 10MHz | 200 | _   | ns   |

| Data Hold Time   | t <sub>dH</sub>  | f <sub>OSC</sub> = 10MHz | 0   | _   | ns   |

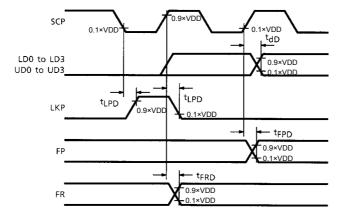

• CRT / LCD = 1 (LCD mode)

# Test Conditions (Unless Otherwise Noted, $V_{SS}$ = 0 V, $V_{DD}$ = 5.0 V ± 10%, Ta = -20 to 75°C)

| Item            | Symbol           | Test Conditions | Min | Max | Unit |

|-----------------|------------------|-----------------|-----|-----|------|

| Data Delay Time | t <sub>dD</sub>  | —               | _   | 20  | ns   |

| LP Delay Time   | t <sub>LPD</sub> | —               | _   | 20  | ns   |

| FP Delay Time   | t <sub>FPD</sub> | _               | _   | 20  | ns   |

| FR Delay Time   | t <sub>FRD</sub> | _               |     | 20  | ns   |

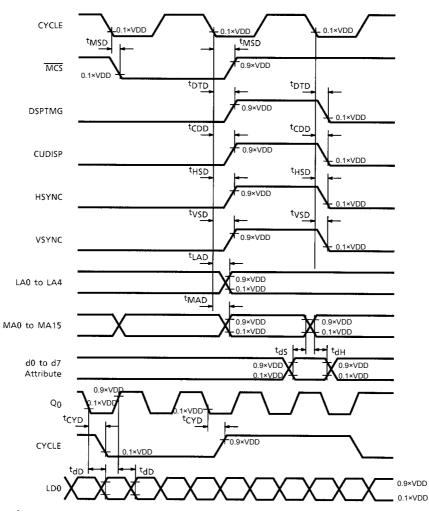

• CRT / LCD = 0 (CRT mode), EXT / INT = 1 (Internal clock)

Test Conditions (Unless Otherwise Noted,  $V_{SS}$  = 0 V,  $V_{DD}$  = 5.0 V ± 10%, Ta = -20 to 75°C)

| Item              | Symbol           | Test Conditions          | Min | Max | Unit |

|-------------------|------------------|--------------------------|-----|-----|------|

| MCS Delay Time    | t <sub>MSD</sub> | —                        | _   | 80  | ns   |

| DSPTMG Delay Time | t <sub>DTD</sub> | —                        | _   | 100 | ns   |

| CUDISP Delay Time | tCDD             | —                        | _   | 100 | ns   |

| HSYNC Delay Time  | t <sub>HSD</sub> | —                        | _   | 80  | ns   |

| VSYNC Delay Time  | t <sub>VSD</sub> | —                        | -   | 100 | ns   |

| LA Delay Time     | t <sub>LAD</sub> | —                        | _   | 80  | ns   |

| MA Delay Time     | t <sub>MAD</sub> | —                        | -   | 100 | ns   |

| Data Set-up Time  | t <sub>dS</sub>  | f <sub>OSC</sub> = 10MHz | 200 | _   | ns   |

| Data Hold Time    | t <sub>dH</sub>  | f <sub>OSC</sub> = 10MHz | 0   | _   | ns   |

| CYCLE Delay Time  | tCYD             | —                        | _   | 20  | ns   |

| Data Delay Time   | t <sub>dD</sub>  | —                        | _   | 110 | ns   |

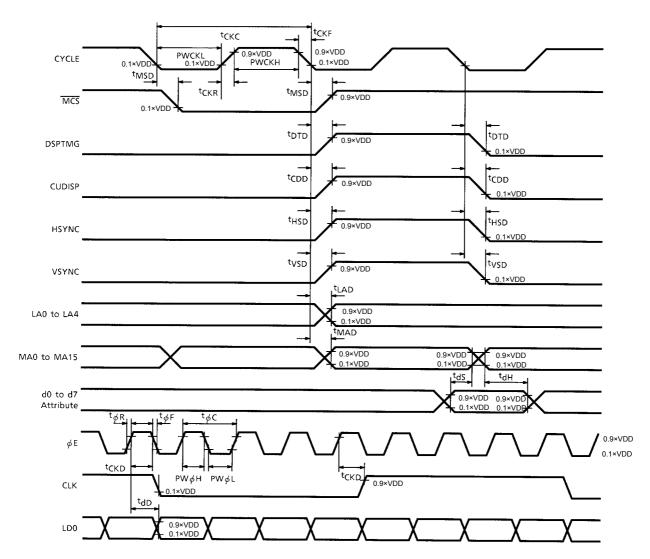

• CRT / LCD = 0 (CRT mode), EXT / INT = 0 (External clock)

# Test Conditions (Unless Otherwise Noted, $V_{SS}$ = 0 V, $V_{DD}$ = 5.0 V ± 10%, Ta = -20 to 75°C)

| Item                   | Symbol                              | Test Conditions           | Min  | Max | Unit |

|------------------------|-------------------------------------|---------------------------|------|-----|------|

| CLK Cycle Time         | t <sub>CKC</sub>                    | _                         | 222  | _   | ns   |

| CLK 1 Pulse Width      | PWCKH                               | _                         | 91   |     | ns   |

| CLK 0 Pulse Width      | PWCKL                               | _                         | 91   |     | ns   |

| CLK Rise and Fall Time | t <sub>CKR</sub> , t <sub>CKF</sub> | _                         | _    | 20  | ns   |

| MCS Delay Time         | t <sub>MSD</sub>                    | _                         | _    | 120 | ns   |

| DSPTMG Delay Time      | t <sub>DTD</sub>                    | _                         | _    | 140 | ns   |

| CUDISP Delay Time      | t <sub>CDD</sub>                    | _                         | _    | 140 | ns   |

| HSYNC Delay Time       | t <sub>HSD</sub>                    | _                         | _    | 120 | ns   |

| VSYNC Delay Time       | t <sub>VSD</sub>                    | _                         | _    | 130 | ns   |

| LA Delay Time          | t <sub>LAD</sub>                    | _                         | _    | 110 | ns   |

| MA Delay Time          | t <sub>MAD</sub>                    | _                         | -    | 140 | ns   |

| Data Set-up Time       | t <sub>dS</sub>                     | f <sub>OSC</sub> = 10 MHz | 200  | _   | ns   |

| Data Hold Time         | t <sub>dH</sub>                     | f <sub>OSC</sub> = 10 MHz | 0    | _   | ns   |

| φE Cycle Time          | tφ <sub>C</sub>                     | _                         | 55.5 |     | ns   |

| φE 1 Pulse Width       | Ρ₩φΗ                                | _                         | 7.75 |     | ns   |

| φE 0 Pulse Width       | PWφL                                | —                         | 7.75 | _   | ns   |

| φE Rise and Fall Time  | tφ <sub>R</sub> , tφ <sub>F</sub>   | —                         | _    | 20  | ns   |

| CLK Delay Time         | t <sub>CKD</sub>                    | —                         | 10   |     | ns   |

| Data Delay Time        | t <sub>dD</sub>                     | —                         | _    | 160 | ns   |

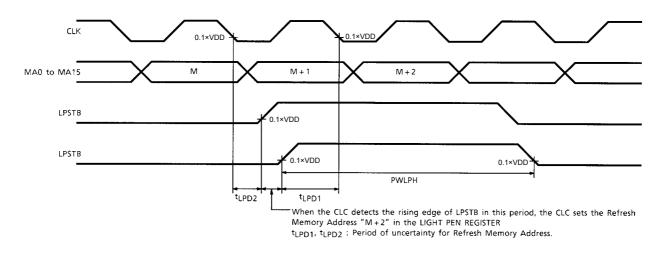

#### • LPSTB timing

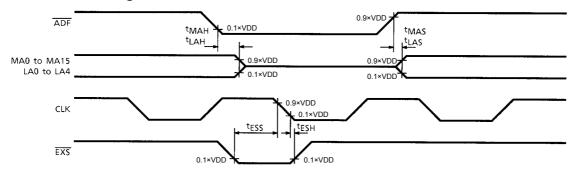

•  $\overline{\text{ADF}}$ ,  $\overline{\text{EXS}}$  timing

#### Test Conditions (Unless Otherwise Noted, $V_{SS} = 0 V$ , $V_{DD} = 5.0 V \pm 10\%$ , Ta = -20 to 75°C)

| Item                      | Symbol            | Test Conditions | Min | Му | Unit |

|---------------------------|-------------------|-----------------|-----|----|------|

| LPSTB Minimum Pulse Width | PWLPH             | —               | 60  | _  | ns   |

| LPSTB Disable Time        | t <sub>LPD1</sub> | —               |     | 20 | ns   |

|                           | t <sub>LPD2</sub> | —               |     | 20 | ns   |

| MA Hold Time              | t <sub>MAH</sub>  | -               |     | 50 | ns   |

| LA Hold Time              | t <sub>LAH</sub>  | —               | _   | 50 | ns   |

| MA Set-up Time            | t <sub>MAS</sub>  | —               | _   | 60 | ns   |

| LA Set-up Time            | tLAS              | —               | _   | 60 | ns   |

| EXS Set-up time           | t <sub>ESS</sub>  | _               | 20  | _  | ns   |

| EXS Hold Time             | t <sub>ESH</sub>  | —               | 40  | —  | ns   |

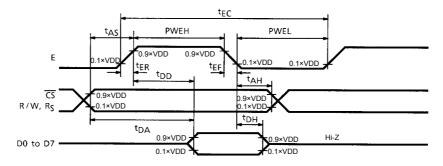

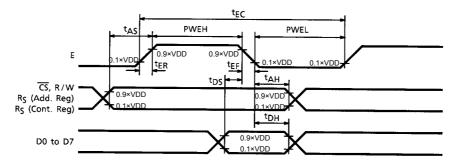

#### • BUS timing

#### (1) Read sequence

#### (2) Write sequence

#### Test Conditions (Unless Otherwise Noted, $V_{SS} = 0 V$ , $V_{DD} = 5.0 V \pm 10\%$ , Ta = -20 to 75°C)

#### CPU read timing

| Item                 | Symbol                            | Test Conditions | Min | Max | Unit |

|----------------------|-----------------------------------|-----------------|-----|-----|------|

| E Cycle Time         | t <sub>EC</sub>                   | —               | 500 | _   | ns   |

| E 1 Pulse Width      | PWEH                              | —               | 220 | -   | ns   |

| E 0 Pulse Width      | PWEL                              | —               | 210 | -   | ns   |

| E Rise and Fall Time | t <sub>ER</sub> , t <sub>EF</sub> | —               | _   | 25  | ns   |

| Address Set-up Time  | t <sub>AS</sub>                   | —               | 70  | -   | ns   |

| Data Delay Time      | t <sub>DD</sub>                   | CL=50pF         | -   | 180 | ns   |

| Data Hold Time       | t <sub>DH</sub>                   | —               | 10  | -   | ns   |

| Address Hold Time    | t <sub>AH</sub>                   | _               | 10  | _   | ns   |

| Data Access Time     | t <sub>DA</sub>                   | —               | _   | 250 | ns   |

#### **CPU** write timing

| Item                 | Symbol                            | Test Conditions | Min | Max | Unit |

|----------------------|-----------------------------------|-----------------|-----|-----|------|

| E Cycle Time         | t <sub>EC</sub>                   | —               | 500 | _   | ns   |

| E 1 Pulse Width      | PWEH                              | —               | 220 | _   | ns   |

| E 0 Pulse Width      | PWEL                              | —               | 210 | _   | ns   |

| E Rise and Fall Time | t <sub>ER</sub> , t <sub>EF</sub> | —               | _   | 25  | ns   |

| Address Set-up Time  | t <sub>AS</sub>                   | —               | 70  | _   | ns   |

| Data Set-up Time     | t <sub>DS</sub>                   | —               | 60  | _   | ns   |

| Data Hold Time       | t <sub>DH</sub>                   | —               | 10  | _   | ns   |

| Address Hold Time    | t <sub>AH</sub>                   | —               | 10  | _   | ns   |

# <u>TOSHIBA</u>

T7779

### **System Construction**

• CG ROM + attribute RAM

#### • Bit map RAM

## • CG ROM (1-character skew)

### • CG ROM (2-character skew)

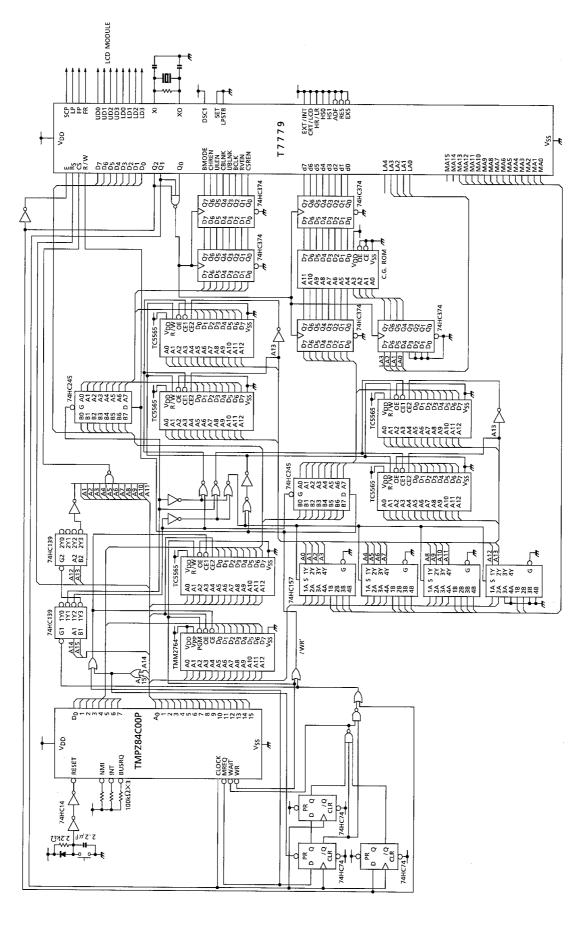

## Application Circuit ··· 640 × 400 (1 / 200 duty) LCD

An application circuit for an LCD is shown overleaf.

| Item                            | Specification                               |  |  |  |

|---------------------------------|---------------------------------------------|--|--|--|

| Character Font                  | 8 × 8 dots                                  |  |  |  |

| Displayed Chars                 | 80 columns × 50 rows = 4000 characters      |  |  |  |

| Refresh Memory<br>Access Method | Synchronous<br>CYCLE CPU T7779 CPU T7779    |  |  |  |

| Address Map                     | 0000 ROM (8K)                               |  |  |  |

|                                 | (CPU Program)<br>2000 RAM (8K)              |  |  |  |

|                                 | 4000 (CPU Work)                             |  |  |  |

|                                 | Attribute<br>RAM (16K)                      |  |  |  |

|                                 | 8000<br>Display<br>RAM (16K)                |  |  |  |

|                                 | C000 Open                                   |  |  |  |

|                                 | FFFE Control Register<br>FFFF Data Register |  |  |  |

| Skew                            | 1 character                                 |  |  |  |

|                 | LCD Specification           |

|-----------------|-----------------------------|

| Dot Size        | 640 × 400                   |

| Duty            | 1/200                       |

| Frame Frequency | 60 Hz                       |

| Dot Frequency   | 16 MHz                      |

| Character Font  | 8 × 8                       |

| Displayed Chars | 80 × 50                     |

| Cursor Mode     | Scan Line 0 to 7, Non-Blink |

|                 | T7779 Initial Data        |              |                 |

|-----------------|---------------------------|--------------|-----------------|

| Reg.<br>No.     | Register Name             | SYM.         | Value<br>(HEX.) |

| R <sub>0</sub>  | Horizontal Total          | Nht          | 52H             |

| R <sub>1</sub>  | Horizontal Displayed      | Nhd          | 50H             |

| R <sub>2</sub>  | Horizontal Sync. Position | Nhsp         | 50H             |

| R <sub>3</sub>  | Sync. Width               | Nvsw<br>Nhsw | 11H             |

| R <sub>4</sub>  | Vertical Total            | Nvt          | 18H             |

| R <sub>5</sub>  | Vertical Total Adjust     | Nadj         | 00H             |

| R <sub>6</sub>  | Vertical Displayed        | Nvd          | FFH             |

| R <sub>7</sub>  | Vertical Sync. Position   | Nvsp         | FFH             |

| R <sub>8</sub>  | Interlace Mode and Skew   | _            | 50H             |

| R <sub>9</sub>  | Max Scan Line Address     | Nr           | 07H             |

| R <sub>10</sub> | Cursor Start              | Ncsr         | 00H             |

| R <sub>11</sub> | Cursor End                | Ncer         | 07H             |

| R <sub>12</sub> | Start Address (H)         | _            | 00H             |

| R <sub>13</sub> | Start Address (L)         | _            | 00H             |

| R <sub>14</sub> | Cursor Address (H)        | _            | 00H             |

| R <sub>15</sub> | Cursor Address (L)        | _            | 00H             |

| R <sub>16</sub> | Light Pen (H)             | _            | _               |

| R <sub>17</sub> | Light Pen (L)             | _            | _               |

| R <sub>18</sub> | SCP Start Position        | Nssp         | 80H             |

| R <sub>19</sub> | SCP End Position          | Nsep         | 50H             |

| R <sub>20</sub> | Display Start Position    | Ndsp         | 00H             |

| R <sub>21</sub> | Display End Position      | Ndep         | 50H             |

| R <sub>22</sub> | Additional Address (H)    | —            | 07H             |

| R <sub>23</sub> | Additional Address (L)    | _            | D0H             |

Timing Chart

| ;<br>;<br>; | T7779 DEMO SET PROGRAM VER1.00<br>SOURCE PROGRAM for TMPZ84C00P<br>15-FEB1991 |           |                               |  |  |

|-------------|-------------------------------------------------------------------------------|-----------|-------------------------------|--|--|

| ;           | REGISTER NUMBER DEFINITION                                                    |           |                               |  |  |

| CMD         | EOU                                                                           | OFFFEH    | COMMAND REG.                  |  |  |

| DAT         | EOU                                                                           | OFFFEH    | ;DATA REG.                    |  |  |

|             | ~<br>EQU                                                                      |           | ;ATTRIBUTE RAM ADDRESS        |  |  |

| DPRAM<br>;  | EQU                                                                           | 8000H     | ;DISPLAY RAM ADDRESS          |  |  |

| ;<br>;      | MAIN PH                                                                       | ROGRAM    |                               |  |  |

|             | ORG                                                                           | 0000H     |                               |  |  |

| START:      | LD                                                                            | SP, 3FFFH | ;INIT STACPOINT               |  |  |

|             | LD                                                                            | HL, CMD   | ;HL < - COMMAND REG. ADDRESS  |  |  |

|             | LD                                                                            | D, 00H    |                               |  |  |