**TOSHIBA**

#### TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T7932

#### COLUMN DRIVER LSI FOR A DOT MATRIX GRAPHIC LCD

The T7932 is a column (segment) driver for a small—or medium—scale dot matrix graphic LCD. The T7932 realizes a low power LCD system using the CMOS Si—Gate process. The T7932 stores 4—bit / 8—bit display data transferred from a microprocessor. The built—in display RAM image corresponds to the LCD screen and the data is converted to an LCD drive signal. The T7932 can be combined with a T7933 to construct an LCD system. An MPU can drive the T7932 directly.

#### Weight: 1.5 g (typ.)

#### **Features**

• Dot matrix graphic LCD column driver with display RAM.

Interface : with 80-series MPU and 68-series MPU (4-bit / 8-bit)

Selectable column output pin arrangement

(Optional mode : odd / even separate mode)

• Display RAM capacity:  $50 \times 8 \times 4 = 1600$  bits

• LCD drive output: 50

• Duty: Can be controlled by external input signal.

Various functions

Display Data Read / Write, Display ON / OFF, Set Address, Set Display Start Page, Read Status, Set Up / Down mode

• Low power consumption

Logic power supply ∶ 5 V ± 10%

• 80-pin flat plastic package

damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is subject to change without notice.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general

can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the

buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and

to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or

damage to property.

<sup>•</sup> The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

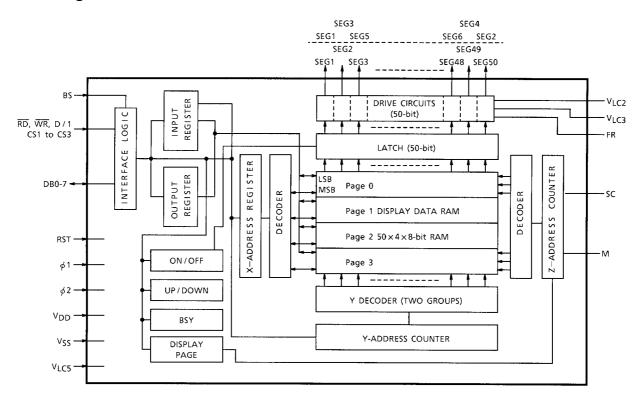

# **Block Diagram**

T7932

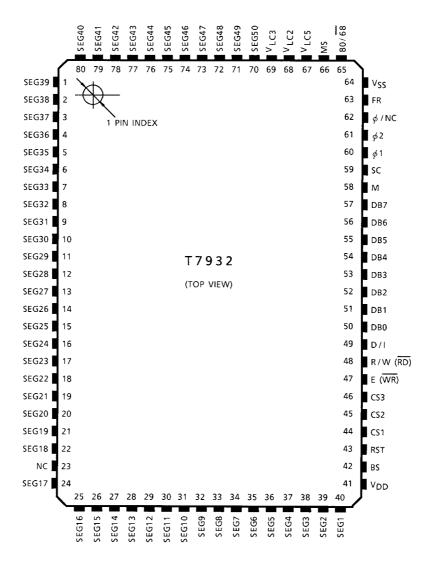

# **Pin Assignment**

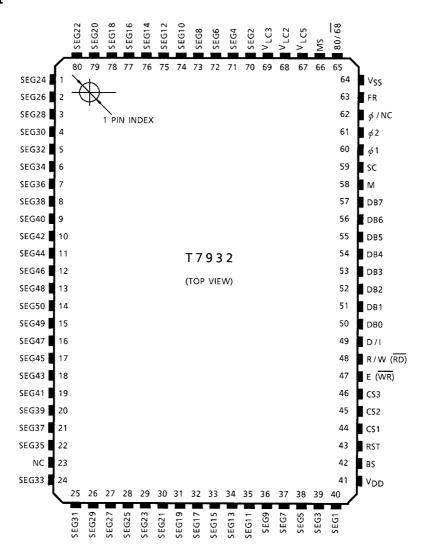

# **Pin Assignment**

(MS = L)

# **Pin Functions**

| Pin Name         | 1/0    |                                                             | Functions                                             |                         |                                 |                        |                         |                                                         |                                        |  |  |  |

|------------------|--------|-------------------------------------------------------------|-------------------------------------------------------|-------------------------|---------------------------------|------------------------|-------------------------|---------------------------------------------------------|----------------------------------------|--|--|--|

| SEG1 to<br>SEG50 | Output | LCD drive signal                                            | outputs                                               |                         |                                 |                        |                         |                                                         | V <sub>DD</sub> to<br>V <sub>LC5</sub> |  |  |  |

|                  |        | Chip select                                                 | CS1                                                   | CS2                     | CS3                             |                        |                         | State                                                   |                                        |  |  |  |

|                  |        |                                                             | L                                                     | L                       | L                               | disable                |                         |                                                         |                                        |  |  |  |

|                  |        |                                                             | L                                                     | L                       | Н                               | disable                |                         |                                                         |                                        |  |  |  |

|                  |        |                                                             | L H L disable                                         |                         |                                 |                        |                         |                                                         |                                        |  |  |  |

| CS1 to CS3       | Input  |                                                             | L H H READ / WRITE enable                             |                         |                                 |                        |                         |                                                         |                                        |  |  |  |

|                  |        |                                                             | Н                                                     | L                       | L                               | WRITE                  | enable o                | nly                                                     | V <sub>SS</sub>                        |  |  |  |

|                  |        |                                                             | Н                                                     | L                       | Н                               | WRITE                  | enable o                | nly                                                     |                                        |  |  |  |

|                  |        |                                                             | Н                                                     | Н                       | L                               | WRITE                  | enable o                | nly                                                     |                                        |  |  |  |

|                  |        |                                                             | Н                                                     | Н                       | Н                               | READ /                 | WRITE 6                 | enable                                                  |                                        |  |  |  |

| E(WR)            | Input  | • R / W = H re (2) WR (80-se • Write opera                  | ead data<br>ries MPU<br>tion: Data<br>of .            | edge of Data of DB0 WR  | of E.<br>f DB0 to<br>) to DB7 I | DB7 outp               | ut to MPl<br>e input re | egister at the rising edge                              | V <sub>DD</sub> to<br>V <sub>SS</sub>  |  |  |  |

| R/W(RD)          | Input  | (2) RD (80−ser<br>• RD = L: Data                            | he input<br>ies MPU<br>a output                       | register<br>)<br>to MPU | can acce                        | ept data w<br>2, CS3 = | hen CS2<br>H.           | S3 = H.<br>, CS3 = H or CS1 = H.<br>CS3 = H or CS1 = H. | V <sub>DD</sub> to<br>V <sub>SS</sub>  |  |  |  |

| D/I              | Input  | Select data / instr<br>D / I = H : Data<br>D / I = L : Data | a DB0 to                                              |                         |                                 |                        |                         |                                                         | V <sub>DD</sub> to<br>V <sub>SS</sub>  |  |  |  |

|                  |        | Data bus: bi-dire                                           | ctional th                                            | ree-sta                 | te bus.                         |                        |                         |                                                         | _                                      |  |  |  |

|                  |        | E(WR)                                                       | E ( WR ) R / W ( RD ) CS1 CS2 CS3 State of DB0 to DB7 |                         |                                 |                        |                         |                                                         |                                        |  |  |  |

|                  |        | Н                                                           | Ξ                                                     |                         | *                               | Н                      | Н                       | Output                                                  |                                        |  |  |  |

| DB0 to DB7       | 1/0    | *                                                           | L                                                     |                         | Н                               | *                      | *                       | Input                                                   | V <sub>DD</sub> to                     |  |  |  |

|                  |        | *                                                           | L                                                     |                         | *                               | Н                      | Н                       | High impedance                                          | V <sub>SS</sub>                        |  |  |  |

|                  |        |                                                             |                                                       | Other                   | s                               |                        |                         | High impedance                                          | <u> </u>                               |  |  |  |

|                  |        |                                                             | : Care<br>eries MP                                    | U                       |                                 |                        |                         |                                                         |                                        |  |  |  |

# **Pin Functions**

| Pin Name         | 1/0   | Functions                                                                                                                               | Level                                 |

|------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| FR               | Input | Frame signal                                                                                                                            | $V_{DD}$ to $V_{SS}$                  |

| sc               | Input | Shift Clock Pulse T7932 output column signal corresponds to display data synchronized to the rising edge of SC.                         | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| М                | Input | Display synchronous signal M sets the 5-bit display line counter and synchronizes a row signal to the frame timing when M becomes high. | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| φ1, φ2           | Input | 2-phase clock signal for internal operation                                                                                             | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| 80 / 68          | Input | Select CPU type  80 / 68 = H: 80-series MPU  80 / 68 = L: 68-series MPU                                                                 | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| φ / NC           | Input | 80 / $\overline{68}$ = H: input terminal for φ or CLK signal.<br>80 / $\overline{68}$ = L: not connected                                | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| RST              | Input | Reset signal RST = L sets display OFF, and sets mode to Y-address counter. Maintains this state until changed by another command.       | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| BS               | Input | Bus Select BS = H: 8-bit interface (DB0 to DB7) BS = L: 4-bit interface (DB4 to DB7) first send upper 4 bits, then lower 4 bits.        | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| MS               | Input | Select pin assignment MS = H: Optional mode (odd / even output) MS = L: Normal output * See PIN ASSIGNMENT                              | V <sub>DD</sub> to<br>V <sub>SS</sub> |

| V <sub>LC2</sub> | Input | Power supply for LCD drive                                                                                                              |                                       |

| V <sub>LC3</sub> | Input | Power supply for LCD drive                                                                                                              |                                       |

| V <sub>LC5</sub> | Input | Power supply for LCD drive                                                                                                              | _                                     |

| $V_{DD}$         | Input | Logic power supply (5.0 V)                                                                                                              |                                       |

| $V_{SS}$         | Input | Logic power supply (0 V)                                                                                                                |                                       |

### **Function of Each Block**

#### Interface

The T7932 can interface to a 4-bit or 8-bit MPU.

(1) 4-bit mode (BS = H)

The T7932 can transfer 8-bit data (4 bits  $\times$  2) when BS = H. The T7932 uses the upper 4 bits (DB4 to DB7) for data transfer. The upper 4 bits are transferred first, then the lower 4 bits.

(2) 8-bit mode (BS = L)

When BS is held at L, the T7932 uses DB0 to DB7 to data transfer.

#### Input register

8-bit data from the MPU is latched to this register. The D / I signal distinguishes between instruction data and display data.

### Output register

8-bit data is read from the display RAM, latched to the output register, and the address is automatically incremented or decremented by 1. The MPU cannot read correct data on the first data reading, but reads the correct data on the second read operation.

#### X-address register

This register stores a page address for display RAM reading or writing.

#### Y-address counter

The Y-address counter has a 50-bit Up / Down counter. The T7932 increases or decreases the address with the display data read / write operation. The Up / Down mode and start address are determined by the instruction. RST = L sets Up mode for this counter.

#### • Z-address counter

The counter points to the row of display data which will be displayed next. The senior two bits hold the page numbers, and the lower three bits hold the number of the row within the page. Data output is synchronized to SC, the row driver signal, and this counter is incremented by 1 on the falling edge of SC.

#### Y-decoder

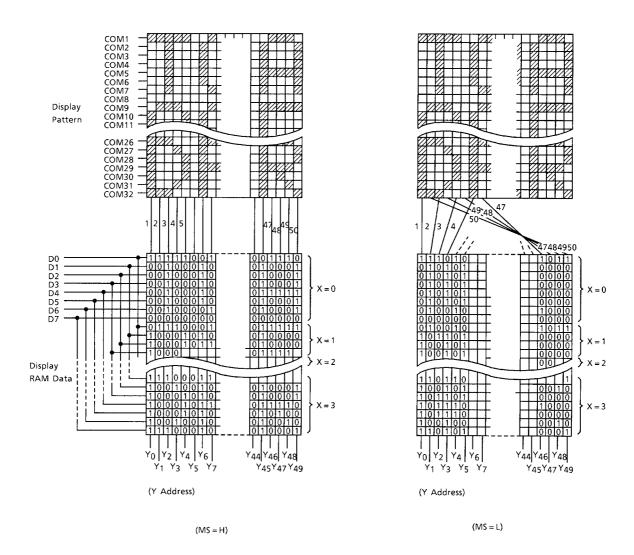

The Y-decoder changes the order of the input or output data according to the MS signal. This is to allow for the alternative pin assignment that is available for the LSI. When MS = H, the regular pin assignment is used in which pins SEG1 to SEG50 are adjacent to one another. When MS = L, the even and odd-numbered pins are divided into separate blocks.

See the sections DISPLAY DATA RAM and PIN ASSIGNMENT.

TOSHIBA T7932

### • Display ON / OFF flip-flop

This flip—flop is set to the display ON / OFF state by the instruction. In the OFF state, outputs from the display RAM are set to 0 (display is all OFF). In the ON state, the T7932 outputs the display data held in the display RAM. This command never changes the display data in the display RAM.

# • Display page register

This register stores 2 bits of data which point to the display start page. The "M" signal sets the contents of this register to the value in the upper 2 bits of the Z-address counter.

### • Up / Down flip-flop

This flip-flop determines the count mode of the Y-address counter. In Up mode, the Y-address counter is increased by 1. If the Y-address = 49, the address becomes 0 after the operation. In Down mode, the Y-address counter is decreased by 1.

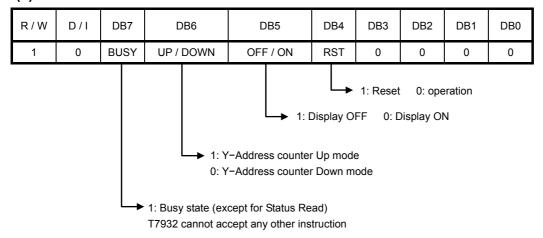

### Busy flag

During the execution of an instruction, the T7932 sets the Busy flag (except for when it executes the Status Read instruction). The MPU can poll the Busy flag when the MPU performs a Read Status operation. While the T7932's Busy flag is set, the T7932 cannot accept any instructions other than Status Read. Hence the MPU must perform a Read Status before sending the next instruction.

\* Busy state time (T) is always shown as follows:

```

1 / F \le T \le 2 / F [s]

```

F:  $\phi$  1,  $\phi$  2 frequency (T7933 oscillation frequency × 1 / 2)

#### Latch

The T7932 latches the data from the display RAM at the rising edge of SC.

#### LCD drive circuit

The T7932 has 50 column drivers. The display data in the latch circuit and the FR signal select one of four levels of LCD drive voltage.

# **Display Control Instructions**

### (1) Set X, Y-address

| R/W | D/I | DB7 | DB6 | DB5 | DB4              | DB3 | DB2 | DB1 | DB0 |        |  |  |

|-----|-----|-----|-----|-----|------------------|-----|-----|-----|-----|--------|--|--|

| 0   | 0   | 0   | 0   |     |                  |     |     |     |     | Page 0 |  |  |

| 0   | 0   | 0   | 1   |     | 0 to 49 (binary) |     |     |     |     |        |  |  |

| 0   | 0   | 1   | 0   |     | (Address)        |     |     |     |     |        |  |  |

| 0   | 0   | 1   | 1   |     |                  |     |     |     |     | Page 3 |  |  |

Y-Address 0, 2, ... ,3, 1 (MS = L) 0, 1, ... 48, 49 (MS = H)

| 00 | Page 0 |

|----|--------|

| 01 | Page 1 |

| 10 | Page 2 |

| 11 | Page 3 |

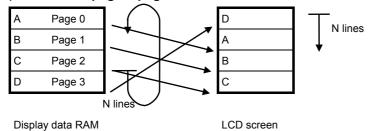

Display Data RAM

# (2) Set Up / Down

| R/W | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |           |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------|

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 1   | 1   | Up mode   |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 1   | 0   | Down mode |

This instruction selects the Up / Down mode for the Y-Address counter.

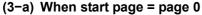

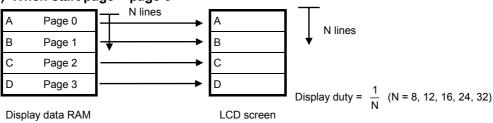

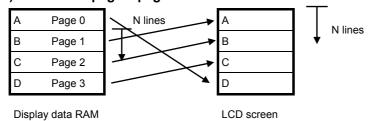

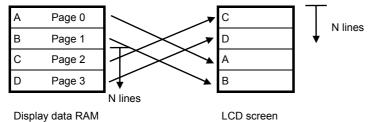

# (3) Display Start Page

| R/W | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |                            |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------|

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 0   | Start Page 0: See Fig. 3-a |

| 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | Start Page 1: See Fig. 3-b |

| 0   | 0   | 1   | 0   | 1   | 1   | 1   | 1   | 1   | 0   | Start Page 2: See Fig. 3-c |

| 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | Start Page 3: See Fig. 3-d |

This instruction specifies the RAM page whose data will be displayed at the top of the LCD screen. Data is displayed starting form the first line of the indicated page up to the end line at the duty factor specified by the T7933.

The relation between RAM page and display position is as follows:

### (3-b) When start page = page 1

### (3-c) When start page = page 2

### (3-d) When start page = page 3

# (4) Display ON / OFF

| R/W | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |             |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------------|

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 1   | Display ON  |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0   | Display OFF |

This instruction controls the display ON / OFF setting. This instruction does not change the contents of the display RAM.

# (5) Read / Write Display Data

| R/W | D/I | DB7 | DB6            | DB5 | DB4     | DB3     | DB2 | DB1 | DB0 |                    |

|-----|-----|-----|----------------|-----|---------|---------|-----|-----|-----|--------------------|

| 1   | 1   |     |                |     | (Dienla | v Data) |     |     |     | Read: MPU ← T7932  |

| 0   | 1   |     | (Display Data) |     |         |         |     |     |     | Write: MPU → T7932 |

This instruction sends data to or receives data from the display RAM address which is pointed to. However, the MPU cannot read the correct data on the first reading. (Refer to Output Register in the Section FUNCTION OF EACH BLOCK.)

### (6) Status Read

# **Example of Timing**

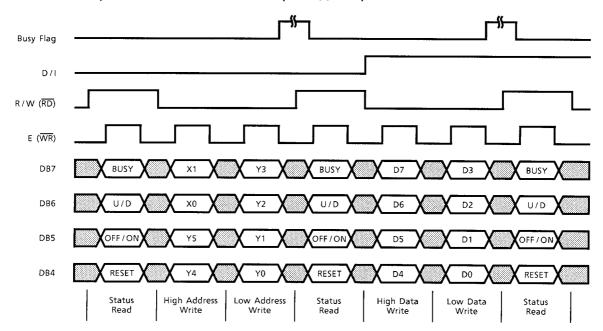

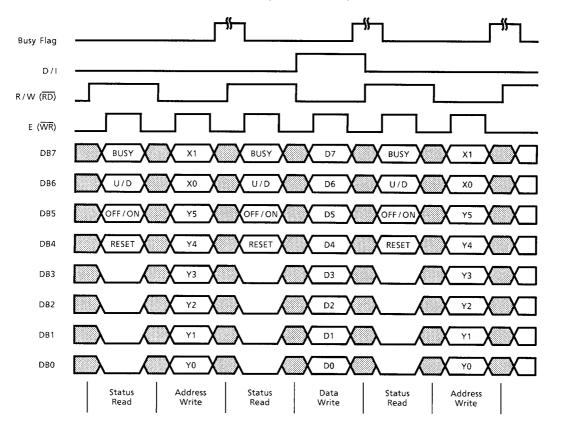

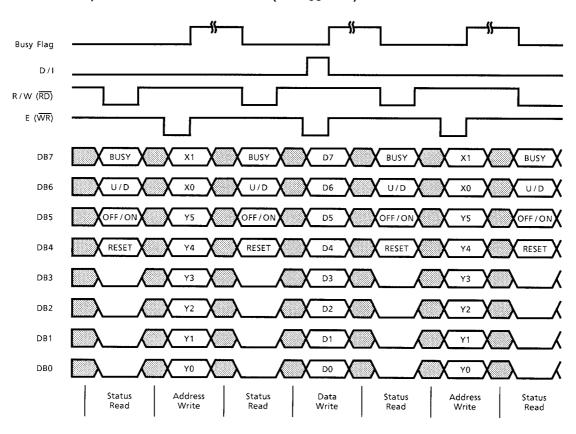

• 4-bit mode, 68-series MPU interface (80 /  $\overline{68}$  = L)

The Busy flag is set on the falling edge of the second E signal.

In this mode, it is not necessary to check the Busy flag between sending the upper data nybble and sending the lower data nybble.

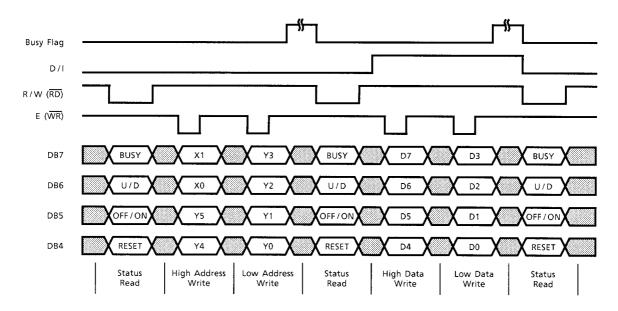

• 4-bit mode, 80-series MPU interface (80 /  $\overline{68}$  = H)

• 8-bit mode, 68-series MPU interface (80 /  $\overline{68}$  = L)

• 8-bit mode, 80-series MPU interface (80 /  $\overline{68}$  = H)

# **Display Data RAM**

# **Alternative Pin Assignment Mode**

This mode allows selection of the pin assignment.

In order to facilitate wiring, two alternative pin assignment layouts are available.

If MS = H, the standard assignment is selected. If MS = L, the odd and even output pins are divided into separate blocks

See the PIN ASSIGNMENT sections.

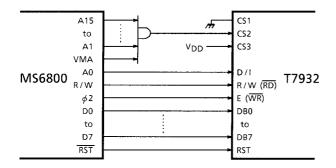

#### **Interface to MPU**

In each case, the address assigned to the T7932 is shown as follows.

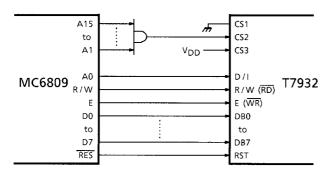

### • Example of connection to MC6800

- □ Read / Write the display data \$FFFF

- □ Write the display instruction \$FFFE

- □ Read the status \$FFFE

# • Example of connection to MC6809

- □ Read / Write the display data \$FFFF

- □ Write the display instruction \$FFFE

- □ Read the status \$FFFE

MC6800 and MC6809 is a registered trademark of Motorola Semiconductor Products Inc.

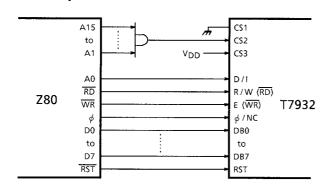

### • Example of connection to Z80

- □ Read / Write the display data \$FFFF

- □ Write the display instruction \$FFFE

- □ Read the status \$FFFE

Z80 is a registered trademark of Zilog Inc.

# Absolute Maximum Ratings (Ta = 25°C)

| Item                  | Symbol                                                                   | Rating                                          | Unit |

|-----------------------|--------------------------------------------------------------------------|-------------------------------------------------|------|

| Supply Voltage (1)    | V <sub>DD</sub> (Note 1)                                                 | -0.3 to 7.0                                     | V    |

| Supply Voltage (2)    | V <sub>LC2</sub> , V <sub>LC3</sub> ,<br>V <sub>LC5</sub><br>(Note 1, 2) | V <sub>DD</sub> - 13.5 to V <sub>DD</sub> + 0.3 | ٧    |

| Input Voltage         | V <sub>IN</sub> (Note 1)                                                 | -0.3 to V <sub>DD</sub> + 0.3                   | V    |

| Operating Temperature | T <sub>opr</sub>                                                         | −20 to 75                                       | °C   |

| Storage Temperature   | T <sub>stg</sub>                                                         | -55 to 125                                      | °C   |

Note 1: Referenced to  $V_{SS} = 0 \text{ V}$

Note 2: Ensure that the following condition is always maintained.  $V_{DD} \ge V_{LC2} \ge V_{LC3} \ge V_{LC5}$

# Electrical Characteristics DC Characteristics Test Conditions

(Unless otherwise noted,  $V_{SS}$  = 0 V,  $V_{DD}$  = 5.0 V  $\pm$  10%,  $V_{LC5}$  = 0 V, Ta = -20 to 75°C)

| Ite               | em          | Symbol          | Test<br>Circuit | Test Condition                    | Min                      | Тур. | Max                      | Unit     | Pin Name                               |

|-------------------|-------------|-----------------|-----------------|-----------------------------------|--------------------------|------|--------------------------|----------|----------------------------------------|

| Operating '       | Voltage (1) | $V_{DD}$        | _               | _                                 | 4.5                      | 5.0  | 5.5                      | V        | $V_{DD}$                               |

| Operating '       | Voltage (2) | $V_{LC5}$       | _               | _                                 | V <sub>DD</sub><br>- 11  | -    | V <sub>DD</sub><br>- 3.0 | ٧        | V <sub>LC5</sub>                       |

| Input<br>Voltage  | H Level     | V <sub>IH</sub> | _               | _                                 | V <sub>DD</sub><br>- 1.0 | _    | V <sub>DD</sub>          | V        | M, FR, S <u>C,</u><br>BS, 80 / 68 ,    |

| voltage           | L Level     | $V_{IL}$        | _               | _                                 | 0                        | _    | 1.0                      | V        | MS, φ1, φ2                             |

| lanut             | H Level     | V <sub>IH</sub> | _               |                                   | 2.2                      | _    | $V_{DD}$                 | ٧        | CS1 to CS3,                            |

| Input<br>Voltage  | L Level     | $V_{IL}$        | _               | -                                 | 0                        | -    | 0.8                      | <b>V</b> | E, R / W,<br>D / I, DB0 to<br>DB7, RST |

| Output<br>Voltage | H Level     | V <sub>OH</sub> | _               | -                                 | V <sub>DD</sub><br>- 0.4 | 1    | V <sub>DD</sub>          | ٧        | DB0 to DB7                             |

| voltage           | L Level     | V <sub>OL</sub> | _               | 1                                 | 0                        | 1    | 0.4                      | ٧        |                                        |

|                   | H Level     | V <sub>OH</sub> | _               | _                                 | V <sub>DD</sub><br>- 0.3 | _    | V <sub>DD</sub>          | ٧        |                                        |

| Output            | M Level     | Vari            |                 | V <sub>LC2</sub> = V <sub>2</sub> | V <sub>2</sub><br>- 0.3  | _    | V <sub>2</sub><br>+ 0.3  | ٧        | SEG1 to                                |

| Voltage           | IVI LEVEI   | V <sub>OM</sub> |                 | V <sub>LC3</sub> = V <sub>3</sub> | V <sub>3</sub><br>- 0.3  |      | V <sub>3</sub><br>+ 0.3  | ٧        | SEG50                                  |

|                   | L Level     | V <sub>OL</sub> |                 | _                                 | V <sub>5</sub>           |      | V <sub>5</sub><br>+ 0.3  | ٧        |                                        |

| Iter                            | n         | Symbol           | Test<br>Circuit | Test Condition                                                                                                                                                                                                                  | Min | Тур. | Max | Unit | Pin Name        |

|---------------------------------|-----------|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|-----------------|

| Output                          | H Level   | R <sub>OH</sub>  | _               | V <sub>OUT</sub> = V <sub>DD</sub> - 0.5 V                                                                                                                                                                                      | _   | _    | 1.5 | kΩ   | DB0 to DB7      |

| Resistance                      | L Level   | R <sub>OL</sub>  | _               | V <sub>OUT</sub> = 0.5 V                                                                                                                                                                                                        | _   | _    | 0.2 | kΩ   | 000 (0 007      |

|                                 | H Level   | R <sub>OH</sub>  | _               | V <sub>OUT</sub> = V <sub>DD</sub> - 0.5 V                                                                                                                                                                                      | _   | _    | 5.0 | kΩ   |                 |

| Output                          | M Level   | Rom              | _               | V <sub>LC2</sub> = V <sub>2</sub> ,<br>V <sub>OUT</sub> = V <sub>2</sub> ± 0.5 V                                                                                                                                                | _   | _    | 5.0 | kΩ   | SEG1 to         |

| Resistance                      | IVI LEVEI | NOM              | _               | $V_{LC3} = V_3,$<br>$V_{OUT} = V_3 \pm 0.5 \text{ V}$                                                                                                                                                                           | _   | _    | 5.0 | kΩ   | SEG50           |

|                                 | L Level   | R <sub>OL</sub>  | _               | $V_{LC5} = V_5,$<br>$V_{OUT} = V_5 \pm 0.5 \text{ V}$                                                                                                                                                                           | _   | _    | 5.0 | kΩ   |                 |

| Operating fr                    | equency   | f <sub>osc</sub> | _               | Ta = −10 to 70°C                                                                                                                                                                                                                | 25  | _    | 300 | kHz  | φ1, φ2          |

| Current Consumption (Note 1)    |           | Iss              | _               | $\begin{split} &V_{DD} = 5.0 \text{ V} \\ &V_{LC5} = 0 \text{ V} \\ &V_{LC3} = V_3 \\ &V_{LC2} = V_2 \\ &f_{FR} = 35 \text{ Hz} \\ &f_{cp} = 215 \text{ kHz} \\ &\text{SEG1 to SEG50: no load} \\ &\text{(Note 3)} \end{split}$ | _   | _    | 200 | μA   | V <sub>SS</sub> |

| Current Consumption<br>(Note 2) |           | Iss              | _               | $\begin{array}{l} V_{DD} = 5.0 \text{ V} \\ V_{LC5} = 0 \text{ V} \\ V_{LC3} = V_3 \\ V_{LC2} = V_2 \\ f_{FR} = 35 \text{ Hz} \\ f_{cp} = 215 \text{ kHz} \\ \text{SEG1 to SEG50: no load} \\ \text{(Note 3)} \end{array}$      | _   | _    | 20  | μΑ   | V <sub>SS</sub> |

Note 1: Current consumption while the internal data receiver is operating.

Note 2: Current consumption while the internal data receiver is sleeping.

Note 3:

$$V_3 = V_{DD} - \frac{3}{5} (V_{DD} - V_{LC5})$$

$V_2 = V_{DD} - \frac{2}{5} (V_{DD} - V_{LC5})$

$$V_2 = V_{DD} - \frac{2}{5} (V_{DD} - V_{LC5})$$

Data Level : H = 5.0 V, L = 0 V

# **AC Characteristics**

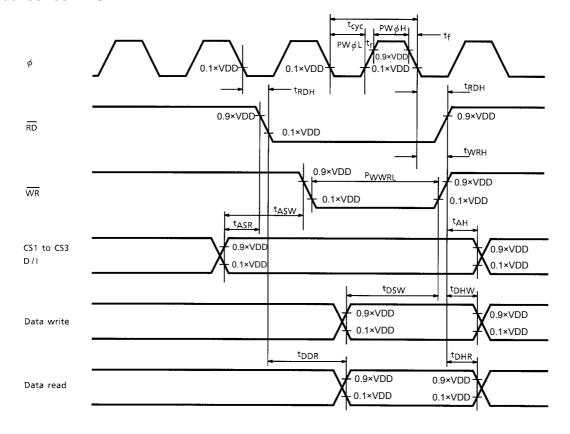

# • 80-series MPU

Test Conditions ( $V_{SS} = 0 \text{ V}, V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ Ta} = -20 \text{ to } 75^{\circ}\text{C}$ )

| ltem                           | Symbol                          | Min | Max | Unit |

|--------------------------------|---------------------------------|-----|-----|------|

| φ Cycle Time                   | t <sub>cyc</sub> Εφ             | 250 | _   | ns   |

| φ Pulse Width H, L             | PWφH, PWφL                      | 110 | _   | ns   |

| φ Pulse Rise / Fall Time       | t <sub>r</sub> , t <sub>f</sub> | _   | 30  | ns   |

| RD Hold Time                   | t <sub>RDH</sub>                | 0   | 100 | ns   |

| WR Hold Time                   | t <sub>WRH</sub>                | 0   | 100 | ns   |

| WR Pulse Width L               | P <sub>WWRL</sub>               | 300 | _   | ns   |

| Write mode Address Set-up Time | t <sub>ASW</sub>                | 0   | _   | ns   |

| Read mode Address Set-up Time  | t <sub>ASR</sub>                | 0   | _   | ns   |

| Address Hold Time              | t <sub>AH</sub>                 | 10  | _   | ns   |

| Data Set-up Time               | t <sub>DSW</sub>                | 100 | _   | ns   |

| Data Delay Time                | t <sub>DDR</sub>                | -   | 200 | ns   |

| Write Mode Data Hold Time      | t <sub>DHW</sub>                | 10  | _   | ns   |

| Read Mode Data Hold Time       | t <sub>DHR</sub>                | 20  | _   | ns   |

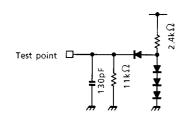

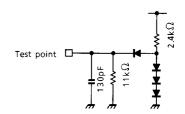

# Test Load (DB0 to DB7)

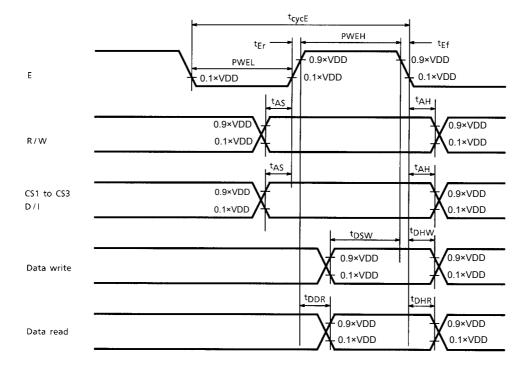

### • 68-series MPU

Test Conditions ( $V_{SS} = 0 \text{ V}, V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ Ta} = -20 \text{ to } 75^{\circ}\text{C}$ )

| ltem                      | Symbol             | Min | Max | Unit |

|---------------------------|--------------------|-----|-----|------|

| E Cycle Time              | t <sub>cyc</sub> E | 500 | _   | ns   |

| E Pulse Width H           | PWEH               | 220 | _   | ns   |

| E Pulse Width L           | PWEL               | 220 | _   | ns   |

| E Pulse Rise Time         | t <sub>r</sub>     | _   | 20  | ns   |

| E Pulse Fall Time         | t <sub>f</sub>     | 1   | 20  | ns   |

| Address Set-up Time       | t <sub>AS</sub>    | 40  | _   | ns   |

| Address Hold Time         | t <sub>AH</sub>    | 10  | _   | ns   |

| Data Set-up Time          | t <sub>DSW</sub>   | 60  | _   | ns   |

| Data Delay Time           | t <sub>DDR</sub>   | _   | 140 | ns   |

| Write Mode Data Hold Time | t <sub>DHW</sub>   | 10  |     | ns   |

| Read Mode Data Hold Time  | t <sub>DHR</sub>   | 20  | _   | ns   |

# Test Load (DB0 to DB7)

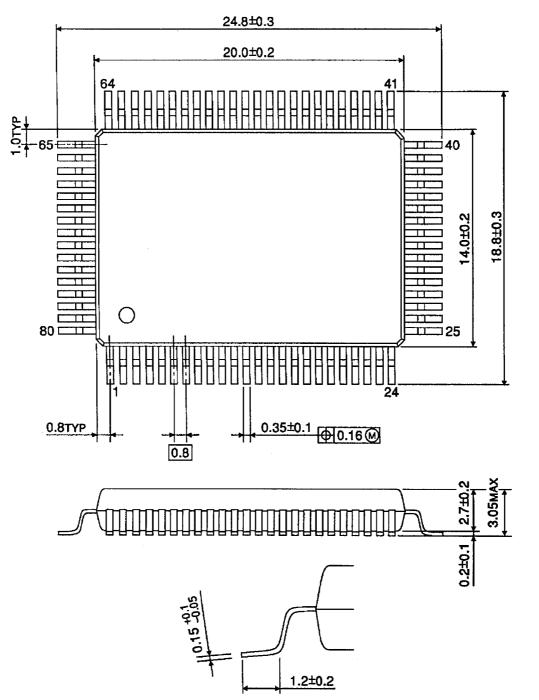

# **Package Dimensions**

QFP80-P-1420-0.80A Unit: mm

Weight: 1.5g (Typ.)