#### TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T7934

#### DOT MATRIX LCD CONTROLLER AND DRIVER LSI

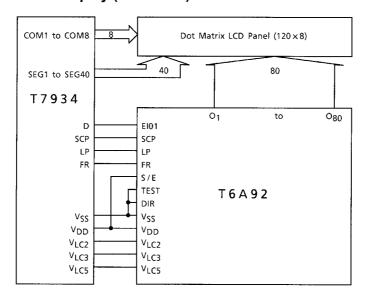

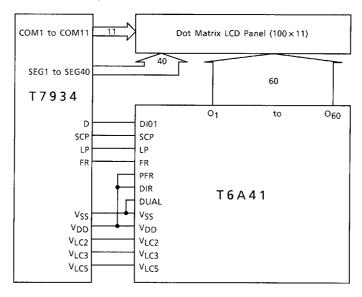

The T7934 is a dot matrix LCD controller. The T7934 realizes low power consumption for an LCD system using high speed CMOS silicon gate technology. The T7934 can display alphanumerics, kana and symbols, corresponding to the data received from a 4/8-bit MPU.

The T7934 has all the functions in one-chip to drive a dot matrix LCD. Therefore, the T7934 can constitute a minimal LCD drive and control system. The T7934 can drive the display of up to 80 characters by using an expansion driver (e.g. T6A41, T6A92).

#### **Features**

- Built-in controller for character-type LCD (character fonts: 5 × 7, 5 × 10)

- Direct interface with 4/8-bit MPU

- Bus interface timing : 2 MHz max

- Display data RAM : 80 × 8 bits (80 characters max)

Character generator ROM : 12000 bits (5 × 10 × 240)

Character font ................................ 5 × 10 dots × 240 characters

- Character generator RAM: 64 × 8 bits

- Both display data and character generator RAMs readable by MPU.

- Built-in LCD driver circuit 40-output column driver 16-output row driver

- Duty factor selection (programmable)

1/8 duty :  $(5 \times 7 \text{ dots} + \text{cursor}) \times 1$  line 1/11 duty :  $(5 \times 10 \text{ dots} + \text{cursor}) \times 1$  line 1/16 duty :  $(5 \times 7 \text{ dots} + \text{cursor}) \times 2$  lines

Weight: 1.5 g (typ.)

Maximum number of characters displayed per line

|                         | Expansi                      | on Driver                    |  |  |  |  |

|-------------------------|------------------------------|------------------------------|--|--|--|--|

| Number of Characters    | T6A41<br>(64-Output Columns) | T6A92<br>(80-output Columns) |  |  |  |  |

| 8 characters × 1 line   | _                            | _                            |  |  |  |  |

| 80 characters × 1 line  | 6 units                      | 5 units                      |  |  |  |  |

| 8 characters × 2 lines  | _                            | _                            |  |  |  |  |

| 40 characters × 2 lines | 3 units                      | 2 units                      |  |  |  |  |

- Built-in power-on reset circuit

- Numerous functions

Display clear, Cursor home, Display ON/OFF, Cursor ON/OFF, Display character blink, Display shift, Cursor shift

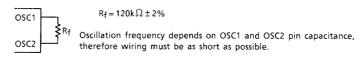

- Built-in clock generator (with external resistor or ceramic oscillator) (external clock operation possible)

- Power supply  $5 \text{ V} \pm 10\%$

- Low power consumption

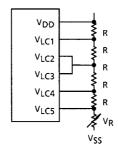

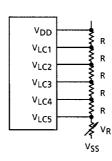

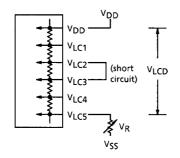

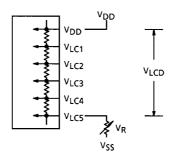

- Built–in resistance ladder for driver  $(1k\Omega \times 5)$

- CMOS and Si-gate processes, 80-pin flat plastic package

- LSI mark

| 10   | SHIBA |  |  |  |  |  |  |  |

|------|-------|--|--|--|--|--|--|--|

| T 7  | 9 3 4 |  |  |  |  |  |  |  |

| 0000 | JAPAN |  |  |  |  |  |  |  |

|      | 8901H |  |  |  |  |  |  |  |

| Rom Code | Column Driver | 68 / 80 | R.L. |  |

|----------|---------------|---------|------|--|

| 0000     | T6A41         | 68      | YES  |  |

| 0100     | T6A41         | 68      | NO   |  |

| 0200     | T6A41         | 80      | YES  |  |

| 0300     | T6A41         | 80      | NO   |  |

Note: 68 / 80 . MPU series

2

R.L. ..... Built-in resistance ladder

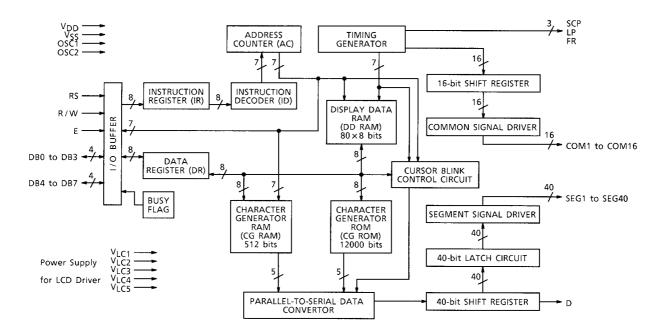

# **Block Diagram (T7934 interior)**

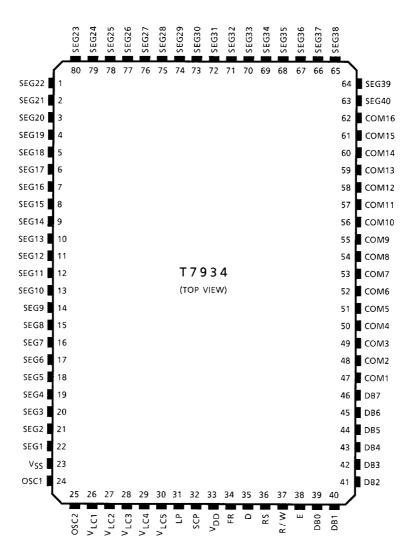

# **Pin Assignment**

# **Pin Functions**

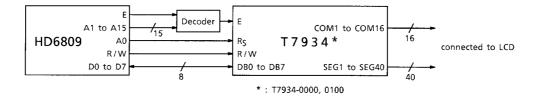

# (1) T7934-0000 pin functions

| Symbol                               | Pin                  | Туре   | Name and Function                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|--------------------------------------|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| RS                                   | 36                   | Input  | Register Select: Selects Data / Instruction register RS = 0 and R / W = 0: Instruction register is selected RS = 0 and R / W = 1: Busy flag and Address counter are selected RS = 1: Data register is selected |  |  |  |  |  |  |  |  |

| R/W                                  | 37                   | Input  | Read / Write: Selects Read / Write data bus state                                                                                                                                                              |  |  |  |  |  |  |  |  |

| E                                    | 38                   | Input  | Enable: Read / Write Enable                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| DB0 to DB3                           | 39 to 42             | 1/0    | Data Bus: Three-state bi-directional data bus (lower 4 bits) During 4-bit operation, these lines are not used                                                                                                  |  |  |  |  |  |  |  |  |

| DB4 to DB7                           | 43 to 46             | 1/0    | Data Bus: Three-state bi-directional data bus (higher 4 bits)                                                                                                                                                  |  |  |  |  |  |  |  |  |

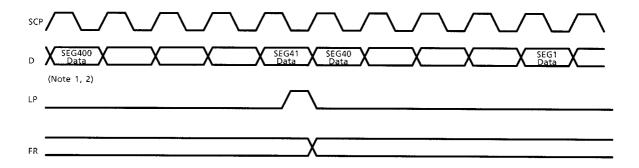

| LP                                   | 31                   | Output | Latch Pulse: Latch pulse for expansion driver                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| SCP                                  | 32                   | Output | Shift Clock Pulse: Shift clock pulse for expansion driver                                                                                                                                                      |  |  |  |  |  |  |  |  |

| FR                                   | 34                   | Output | Frame: Frame signal for expansion driver                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| D                                    | 35                   | Output | Data: Serial data output to the expansion driver 0: OFF 1: ON                                                                                                                                                  |  |  |  |  |  |  |  |  |

| COM1 to<br>COM16                     | 47 to 62             | Output | Common: Row signal output 1 / 8 duty operation: COM9 to COM16 are not selected 1 / 11 duty operation: COM12 to COM16 are not selected                                                                          |  |  |  |  |  |  |  |  |

| SEG1 to<br>SEG40                     | 1 to 22, 63<br>to 80 | Output | Segment: Column signal output                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| $V_{LC5}$                            | 30                   | Input  | Power supply for LCD                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| V <sub>LC1</sub> to V <sub>LC4</sub> | 26 to 29             | Output | Power supply for LCD                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| V <sub>DD</sub> , V <sub>SS</sub>    | 33, 23               | Input  | Power supply for T7934<br>V <sub>DD</sub> = 5.0 V ± 10%<br>V <sub>SS</sub> = 0 V                                                                                                                               |  |  |  |  |  |  |  |  |

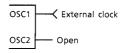

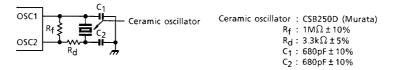

| OSC1, OSC2                           | 24, 25               | _      | When using the internal clock oscillator, connect a resistor or ceramic oscillator between OSC1 and OSC2 When using an external clock, connect the clock to OSC1 and leave OSC2 open                           |  |  |  |  |  |  |  |  |

# (2) T7934-0100 pin functions

| Symbol                               | Pin                 | Туре   | Name and Function                                                                                                                                                                                              |

|--------------------------------------|---------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS                                   | 36                  | Input  | Register Select: Selects Data / Instruction register RS = 0 and R / W = 0: Instruction register is selected RS = 0 and R / W = 1: Busy flag and Address counter are selected RS = 1: Data register is selected |

| R/W                                  | 37                  | Input  | Read / Write: Selects Read / Write data bus state                                                                                                                                                              |

| E                                    | 38                  | Input  | Enable: Read / Write Enable                                                                                                                                                                                    |

| DB0 to DB3                           | 39 to 42            | 1/0    | Data Bus: Three-state bi-directional data bus (lower 4 bits) During 4-bit operation, these lines are not used                                                                                                  |

| DB4 to DB7                           | 43 to 46            | 1/0    | Data Bus: Three-state bi-directional data bus (higher 4 bits)                                                                                                                                                  |

| LP                                   | 31                  | Output | Latch Pulse: Latch pulse for expansion driver                                                                                                                                                                  |

| SCP                                  | 32                  | Output | Shift Clock Pulse: Shift clock pulse for expansion driver                                                                                                                                                      |

| FR                                   | 34                  | Output | Frame: Frame signal for expansion driver                                                                                                                                                                       |

| D                                    | 35                  | Output | Data: Serial data output to the expansion driver 0: OFF 1: ON                                                                                                                                                  |

| COM1 to<br>COM16                     | 47 to 62            | Output | Common: Row signal output 1 / 8 duty operation: COM9 to COM16 are not selected 1 / 11 duty operation: COM12 to COM16 are not selected                                                                          |

| SEG1 to<br>SEG40                     | 1 to 22,63<br>to 80 | Output | Segment: Column signal output                                                                                                                                                                                  |

| V <sub>LC5</sub>                     | 30                  | Input  | Power supply for LCD                                                                                                                                                                                           |

| V <sub>LC1</sub> to V <sub>LC4</sub> | 26 to 29            | Output | Power supply for LCD                                                                                                                                                                                           |

| V <sub>DD</sub> , V <sub>SS</sub>    | 33, 23              | Input  | Power supply for T7934  V <sub>DD</sub> = 5.0 V ± 10%  V <sub>SS</sub> = 0 V                                                                                                                                   |

| OSC1, OSC2                           | 24, 25              | _      | When using the internal clock oscillator, connect a resistor or ceramic oscillator between OSC1 and OSC2 When using an external clock, connect the clock to OSC1 and leave OSC2 open                           |

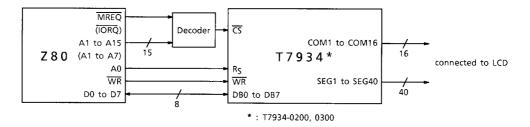

# (3) T7934-0200 pin functions

| Symbol                               | Pin                  | Туре   | Name and Function                                                                                                                                                                                           |

|--------------------------------------|----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS                                   | 36                   | Input  | Register Select: Selects Data / Instruction register  RS = 0 and WR = 0: Instruction register is selected  RS = 0 and WR = 1: Busy flag and address counter are selected  RS = 1: Data register is selected |

| WR                                   | 37                   | Input  | Write: Selects Read / Write data bus state                                                                                                                                                                  |

| CS                                   | 38                   | Input  | Chip Select: Read / Write Enable                                                                                                                                                                            |

| DB0 to DB3                           | 39 to 42             | 1/0    | Data Bus: Three-state bi-directional data bus (lower 4 bits) During 4-bit operation, these lines are not used                                                                                               |

| DB4 to DB7                           | 43 to 46             | 1/0    | Data Bus: Three-state bi-directional data bus (higher 4 bits)                                                                                                                                               |

| LP                                   | 31                   | Output | Latch Pulse: Latch pulse for expansion driver                                                                                                                                                               |

| SCP                                  | 32                   | Output | Shift Clock Pulse: Shift clock pulse for expansion driver                                                                                                                                                   |

| FR                                   | 34                   | Output | Frame: Frame signal for expansion driver                                                                                                                                                                    |

| D                                    | 35                   | Output | Data: Serial data output to the expansion driver 0: OFF 1: ON                                                                                                                                               |

| COM1 to<br>COM16                     | 47 to 62             | Output | Common: Row signal output 1 / 8 duty operation: COM9 to COM16 are not selected 1 / 11 duty operation: COM12 to COM16 are not selected                                                                       |

| SEG1 to<br>SEG40                     | 1 to 22,<br>63 to 80 | Output | Segment: Column signal output                                                                                                                                                                               |

| V <sub>LC5</sub>                     | 30                   | Input  | Power supply for LCD                                                                                                                                                                                        |

| V <sub>LC1</sub> to V <sub>LC4</sub> | 26 to 29             | Output | Power supply for LCD                                                                                                                                                                                        |

| V <sub>DD</sub> , V <sub>SS</sub>    | 33, 23               | Input  | Power supply for T7934  V <sub>DD</sub> = 5.0 V ± 10%  V <sub>SS</sub> = 0 V                                                                                                                                |

| OSC1, OSC2                           | 24, 25               | _      | When using the internal clock oscillator, connect a resistor or ceramic oscillator between OSC1 and OSC2 When using an external clock, connect the clock to OSC1 and leave OSC2 open                        |

# (4) T7934-0300 pin functions

| Symbol                               | Pin                  | Туре   | Name and Function                                                                                                                                                                                           |

|--------------------------------------|----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS                                   | 36                   | Input  | Register Select: Selects Data / Instruction register  RS = 0 and WR = 0: Instruction register is selected  RS = 0 and WR = 1: Busy flag and address counter are selected  RS = 1: Data register is selected |

| WR                                   | 37                   | Input  | Write: Selects Read / Write data bus state                                                                                                                                                                  |

| CS                                   | 38                   | Input  | Chip Select: Read / Write Enable                                                                                                                                                                            |

| DB0 to DB3                           | 39 to 42             | 1/0    | Data Bus: Three-state bi-directional data bus (lower 4 bits) During 4-bit operation, these lines are not used                                                                                               |

| DB4 to DB7                           | 43 to 46             | 1/0    | Data Bus: Three-state bi-directional data bus (higher 4 bits)                                                                                                                                               |

| LP                                   | 31                   | Output | Latch Pulse: Latch pulse for expansion driver                                                                                                                                                               |

| SCP                                  | 32                   | Output | Shift Clock Pulse: Shift clock pulse for expansion driver                                                                                                                                                   |

| FR                                   | 34                   | Output | Frame: Frame signal for expansion driver                                                                                                                                                                    |

| D                                    | 35                   | Output | Data: Serial data output to the expansion driver 0: OFF 1: ON                                                                                                                                               |

| COM1 to<br>COM16                     | 47 to 62             | Output | Common: Row signal output 1 / 8 duty operation: COM9 to COM16 are not selected 1 / 11 duty operation: COM12 to COM16 are not selected                                                                       |

| SEG1 to<br>SEG40                     | 1 to 22,<br>63 to 80 | Output | Segment: Column signal output                                                                                                                                                                               |

| V <sub>LC5</sub>                     | 30                   | Input  | Power supply for LCD                                                                                                                                                                                        |

| V <sub>LC1</sub> to V <sub>LC4</sub> | 26 to 29             | Input  | Power supply for LCD                                                                                                                                                                                        |

| V <sub>DD</sub> , V <sub>SS</sub>    | 33, 23               | Input  | Power supply for T7934  V <sub>DD</sub> = 5.0 V ± 10%  V <sub>SS</sub> = 0 V                                                                                                                                |

| OSC1, OSC2                           | 24, 25               | _      | When using the internal clock oscillator, connect a resistor or ceramic oscillator between OSC1 and OSC2 When using an external clock, connect the clock to OSC1 and leave OSC2 open                        |

### **Function of Each Block**

# Register

The T7934 has two 8-bit registers. One is an Instruction Register (IR), and the other is a Data Register (DR).

The IR stores an instruction code, DD RAM address data or CG RAM address data. The IR is a write-only register for the MPU.

The DR temporarily stores data that is to be written into or read from the DD RAM or the CG RAM. In the Write sequence, the data in the DR is automatically sent to the DD RAM or the CG RAM. In the Read sequence, when the address data has been written into the IR, the data is automatically sent to the DR from the DD RAM or the CG RAM. Therefore, the MPU can read the DD RAM or CG RAM data from the DR. The address data is automatically incremented or decremented after a Read operation.

The relation between RS, R / W ( $\overline{\text{WR}}$ ) and the operation is as shown below.

| RS | R/W<br>(WR) | Operation                                             |

|----|-------------|-------------------------------------------------------|

| 0  | 0           | Write into IR                                         |

| 0  | 1           | Read busy flag (DB7) and Address Counter (DB0 to DB6) |

| 1  | 0           | Write into DR                                         |

| 1  | 1           | Read from DR                                          |

## • Busy flag (BF)

When an instruction is executed, the T7934 sets the Busy flag. The MPU reads the status of the Busy flag using the Read Busy Flag instruction. When the Busy flag is set, the T7934 cannot accept any instructions from the MPU (other than Read Busy Flag). The MPU must check the setting of the Busy flag before sending each instruction.

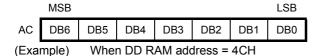

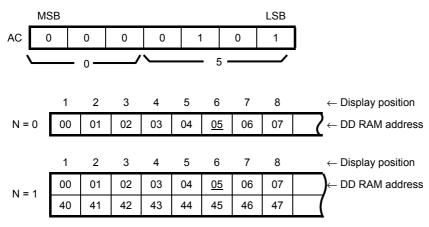

### Address Counter (AC)

The T7934 has a 7-bit Address Counter. The Address Counter points to an address in DD RAM or CG RAM, or to the cursor position. The Set DD RAM Address or Set CG RAM Address instruction specifies which type of address Address Counter contains. The Address Counter is automatically incremented (or decremented) after the data has been written into or read from RAM. When RS = 0 and R / W ( $\overline{\text{WR}}$ ) = 1, the contents of the Address Counter is output on DB0 to DB6.

# • Display data RAM (DD RAM)

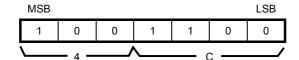

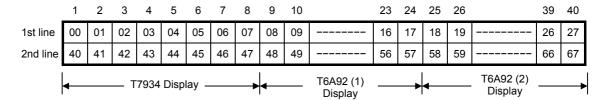

The display data RAM (DD RAM) stores the display data as 8-bit character codes. Its capacity is 80 characters  $\times$  8 bits. The relation between the DD RAM address and the display position is shown below. A DD RAM address is expressed as shown below.

T7934

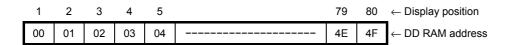

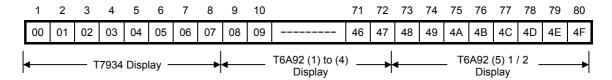

# (1) The relation between the DD RAM address and the display position in 1-Line Display mode (N = 0)

a) Using one T7934, the first 8 characters are displayed as shown below.

| 1  | 2  | 2 3 4 |    | 5  | 6  | 7  | 8  |

|----|----|-------|----|----|----|----|----|

| 00 | 01 | 02    | 03 | 04 | 05 | 06 | 07 |

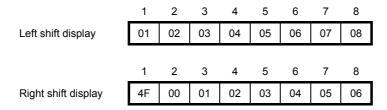

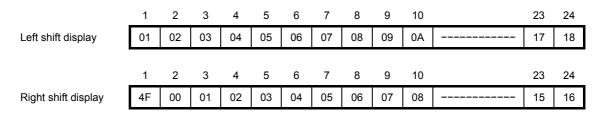

When a Display Shift operation is executed, the relation between the DD RAM address and the display position is as shown below.

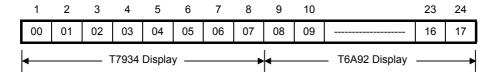

b) When the T7934 is used with one T6A92, the first 24 characters are displayed as shown below.

When a Display Shift operation is executed, the relation between the DD RAM address and the display position is as shown below.

c) Each extra T6A92 allows 16 more characters to be displayed. A maximum of five T6A92s can be used, allowing display of up to 80 characters.

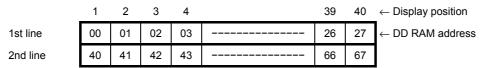

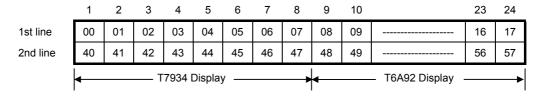

(2) The relation between the DD RAM address and the display position in 2-Line Display mode (N = 1)

Note: The DD RAM address of the 2nd line is not the next address after the last address of the 1st line.

a) Using one T7934, the first 16 characters (8 characters × 2 lines) are displayed as shown below.

| _        | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|----------|----|----|----|----|----|----|----|----|

| 1st line | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

| 2nd line | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

When a Display Shift operation is executed, the relation between the DD RAM address and the display position is as shown below.

Left shift display Right shift display

b) Using one T7934 with one T6A92, the first 48 characters (24 characters  $\times$  2 lines) are displayed as shown below.

When a Display Shift operation is executed, the relation between the DD RAM address and the display position is as shown below.

0A Left shift display 4A Right shift display

c) Each extra T6A92 allows 16 more character to be displayed. Two T6A92s can be used, allowing display of up to 40 characters  $\times$  2 lines.

#### • Character generator ROM (CG ROM)

The character generator ROM generates  $5 \times 10$ —dot character patterns (for 240 different characters) according to the 8-bit character codes in the DD RAM. In the  $5 \times 7$  Dots + Cursor Display mode, the character font uses the upper  $5 \times 7$  dots. The relation between character codes and character patterns is as shown overleaf.

# The Relation Between Character Codes and Character Pattern (CG ROM TYPE 0000 / 0100 / 0200 / 0300)

| HIGHER<br>4 BITS<br>LOWER<br>4 BITS | 0000         | 0001      | 0010  | 0011  | 0100                                   | 0101 | 0110     | 0111                                    | 1000  | 1001                                         | 1010                 | 1011       | 1100                                  | 1101             | 1110 | 1111  |

|-------------------------------------|--------------|-----------|-------|-------|----------------------------------------|------|----------|-----------------------------------------|-------|----------------------------------------------|----------------------|------------|---------------------------------------|------------------|------|-------|

| XXXX0000                            | CGRAM<br>(0) | *****     |       |       |                                        | 1    | •        | :                                       | ***** |                                              |                      | *****      | ****                                  | ****             |      |       |

| XXXX0001                            | (1)          |           |       |       |                                        |      | ***      | -11                                     |       |                                              |                      |            |                                       |                  | ***  | -     |

| XXXX0010                            | (2)          |           | 11    |       |                                        |      |          | <br>                                    | ***   |                                              | •                    | •          | :::                                   | ,:: <sup>‡</sup> |      |       |

| XXXX0011                            | (3)          | •.<br>••• |       | •:    |                                        | **** |          | -***<br>****<br>****                    | ***   |                                              |                      |            |                                       | ****             | ::   | ::-:: |

| XXXX0100                            | (4)          |           |       | •     |                                        |      |          | <br>!                                   | ::::  |                                              | ".<br>"              | *****      | # # # # # # # # # # # # # # # # # # # |                  |      | :::   |

| XXXX0101                            | (5)          |           | •••   | •:    | 1                                      | # F  | ::::     |                                         |       |                                              | ::                   | •          |                                       | ***              | :::  | • • • |

| XXXX0110                            | (6)          |           |       |       | ###################################### | ***  |          | <b>!</b> !                              |       | :::                                          |                      |            | ***                                   | *****            |      |       |

| XXXX0111                            | (7)          | *         |       | •     | ****                                   |      | ****     | <b>!!</b>                               | ===== |                                              |                      | *****      |                                       |                  |      |       |

| XXXX1000                            | (0)          | :::       | Ĺ.    |       |                                        |      |          | <b>.</b> ::                             | ."    |                                              | .:                   | ;          |                                       | •                | .i"  |       |

| XXXX1001                            | (1)          | 122       |       |       |                                        | 1.1  |          | ****                                    | : i.  |                                              | ****                 |            | ,"                                    |                  | i    | ****  |

| XXXX1010                            | (2)          |           | ••••  | 7     |                                        |      |          |                                         |       | ****                                         | *****                | *****      | **                                    | <b>.</b>         |      |       |

| XXXX1011                            | (3)          |           | ***** | ;;    |                                        |      |          |                                         |       |                                              | ***                  |            |                                       | 14881<br>2       | * *  |       |

| XXXX1100                            | (4)          |           | :     |       |                                        |      |          |                                         |       | ****                                         |                      | ::<br>::.: |                                       |                  | ***  |       |

| XXXX1101                            | (5)          |           |       | 34865 |                                        |      | <b>:</b> |                                         |       |                                              | ***                  |            | ***.                                  |                  |      |       |

| XXXX1110                            | (6)          |           | #     |       |                                        |      |          | ··j·                                    |       |                                              | ####<br>####<br>#### |            | ::::                                  |                  | ***  |       |

| XXXX1111                            | (7)          | ••••      | "     | •     |                                        | 2022 |          | ======================================= |       | ###<br>###<br>############################## | :::                  | ٠.!        |                                       | ***              |      |       |

## • Character generator RAM (CG RAM)

The T7934 can display user–defined original character using the character generator RAM.  $(5 \times 7 \text{ dots: } 8\text{-type}, 5 \times 10 \text{ dots: } 4\text{-type})$

The relation between the character codes, the CG RAM address and character patterns is as shown below.

#### (1) For 5 × 7-dot character patterns

|   | CH/<br>(D |   | ACT<br>RAN |   |   |   | 5 |                                        |   |   |   | RAN                   |                                 |                                 | CHARACTER PATTERNS<br>(CG RAM DATA) |   |   |                  |                                      |                                 |                                 |                       |                                                       |

|---|-----------|---|------------|---|---|---|---|----------------------------------------|---|---|---|-----------------------|---------------------------------|---------------------------------|-------------------------------------|---|---|------------------|--------------------------------------|---------------------------------|---------------------------------|-----------------------|-------------------------------------------------------|

| 7 | 6         |   | 4          | 3 | 2 | 1 | 0 | **** · * · · · · · · · · · · · · · · · | 5 | 4 | 3 | 2                     | 1                               | 0                               | 7                                   | 6 | 5 | 4                | 3                                    | 2                               | 1                               | 0                     | 1                                                     |

| 0 | 0         | 0 | 0          | * | 0 | 0 | 0 |                                        | 0 | 0 | 0 | 0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | *                                   | * | * | 1 1 1 1 0        | 1<br>0<br>0<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0<br>0<br>1 | 1<br>0<br>0                     | 1<br>1<br>0<br>1      | Character Pattern<br>Example (1)<br>← Cursor Position |

| 0 | 0         | 0 | 0          | * | 0 | 0 | 1 |                                        | 0 | 0 | 1 | 0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | *                                   | * | * | 0 1 0 0          | 1<br>0<br>0<br>1<br>0<br>0           | 1<br>0<br>0<br>1<br>0<br>0      | 1<br>0<br>0<br>1<br>0<br>0<br>1 | 0<br>0<br>0<br>1<br>1 | Character Pattern<br>Example (2)<br>← Cursor Position |

|   |           |   |            |   |   |   |   |                                        |   |   |   | 0                     | 0 0                             | 0                               | *                                   | * | * | 0                | 00000000                             | 1                               | 2000000                         | 1 0                   |                                                       |

| 0 | 0         | 0 | 0          | * | 1 | 1 | 1 |                                        | 1 | 1 | 1 | 0<br>1<br>1<br>1      | 1<br>0<br>0<br>1                | 1<br>0<br>1<br>0                | *                                   | * | * | 0<br>0<br>0<br>0 | 0 0 0 0 0                            | 1<br>1<br>1<br>1<br>0           | 0<br>0<br>0<br>0                | 0<br>0<br>0<br>0      | * : Invalid                                           |

- Note 1: Character code bit 0 to bit 2 correspond to CG RAM address bit 3 to bit 5.

- Note 2: Bit 0 to bit 2 of the CG RAM address indicate the row within the character bit map. The 8th row (the bottom row) corresponds to the cursor position on the LCD display. Normally the 8th row should be blank (all 0s), otherwise the lowest line of the character will be obscured when used with the cursor.

- Note 3: Character pattern line positions correspond to CG RAM data bit 0 to bit 4. CG RAM data bit 5 to bit 7 is not used for display; the data can be used for general RAM data.

- Note 4: If bit 4 to bit 7 are all 0, a CG RAM character is indicated. The value of bit 3 does not matter. Character codes 00H and 08H select the same character.

Note 5: 1: ON, 0: OFF

# (2) For 5 × 10-dot character patterns

| CHARACTER CODES<br>(DD RAM DATA) | CG RA<br>ADDRE | M<br>SS | CHARACTER PATTERNS<br>(CG RAM DATA) |                   |

|----------------------------------|----------------|---------|-------------------------------------|-------------------|

| 7 6 5 4 3 2 1 0                  | 5 4 3 2        |         | 7 6 5 4 3 2 1 0                     |                   |

|                                  | 0 0            | 0 0     | * * * 0 0 0 1 0                     |                   |

|                                  | 0 0            | 0 1     | 0 0 0 0 0                           |                   |

|                                  | 0 0            | 1 0     | 0 0 1 1 0                           |                   |

|                                  | 0 0            | 1 1     | 0 0 0 1 0                           | Character Pattern |

|                                  | 0 1            | 0 0     | 0 0 0 1 0                           | Example           |

| 0 0 0 0 * 0 0 *                  | 0 0 0 1        | 0 1     | 0 0 0 1 0                           |                   |

| ]                                | 0 1            | 1 0     | 0 0 0 1 0                           |                   |

|                                  | 0 1            | 1 1     | 0 0 0 1 0                           |                   |

|                                  | 1 0            | 0 0     | 10010                               |                   |

|                                  | 1 0            | 0 1     | 0 1 1 0 0                           |                   |

|                                  | 1 0            | 1 0     | * * * 0 0 0 0 0                     | ← Cursor Position |

|                                  | 1 0            | 1 1     | * * *   * * * * *                   |                   |

|                                  | 1 1            | 0 0     |                                     |                   |

|                                  | 1 1            | 0 1     |                                     |                   |

|                                  | 1 1            | 1 0     |                                     |                   |

|                                  | 1 1            | 1 1     | * * * * * * * *                     |                   |

|                                  | 0 0            | 0 0     | * * *                               |                   |

|                                  | 0 0            | 0 1     |                                     |                   |

|                                  | 0 0            | 1 0     |                                     |                   |

|                                  |                |         |                                     |                   |

|                                  | 1 0            | 0 0     |                                     |                   |

| 0 0 0 0 * 1 1 *                  | 1 1 1 0        | 0 1     | !<br>!                              |                   |

|                                  | 1 0            | 1 0     | * * *                               |                   |

|                                  | 1 0            | 1 1     | * * *   * * * * *                   |                   |

|                                  | 1 1            | 0 0     |                                     |                   |

|                                  | 1 1            | 0 1     |                                     |                   |

| 1                                | 1 1            | 1 0     |                                     |                   |

|                                  | 1 1            | 1 1     | * * *   * * * * *                   | * : Invalid       |

Note 1: Character code bit 1 and bit 2 correspond to CG RAM address bit 4 and bit 5.

Note 2: Bit 0 to bit 3 of the CG RAM address indicate the row within the character bit map. The 1 1th row corresponds to the cursor position on the LCD display. Normally the 11th row should be blank (all 0s), otherwise the lowest line of the character will be obscured when used with the cursor. Lines 12 to 16 are not used for display data and can be used for general RAM data.

Note 3: If bit 4 to bit 7 are all 0, a CG RAM character is indicated. The values of bits 0 and 3 do not matter. Character codes 00 H, 01 H, 08 H and 09 H all select the same character.

Note 4: 1: ON, 0: OFF

# • Timing generation circuit

The timing generation circuit generates timing signals for operating internal circuits such as the DD RAM, CG ROM and CG RAM.

The circuit is designed so that access by the MPU does not disturb the display. When data is written to the DD RAM, only the portion of RAM being written to is affected.

This circuit also generates timing signals which operate the extension driver (e.g. the T6A92).

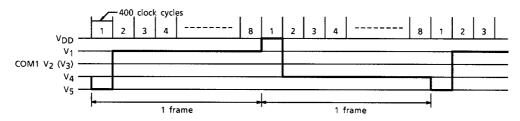

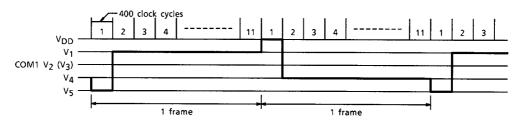

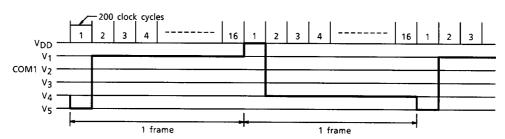

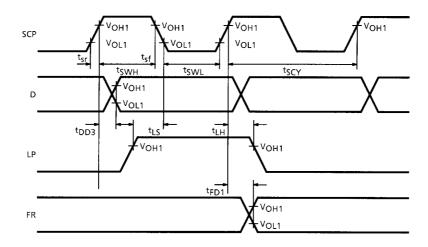

The relation between the timing signals in 1-Line Display mode is as shown below.

Note 1: SEG400 to SEG41 Data for the extension driver

SEG40 to SEG1 Data for the T7934

Note 2: In 2-Line Display mode, "SEG400 Data" changes to "SEG200 Data"

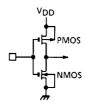

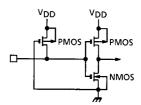

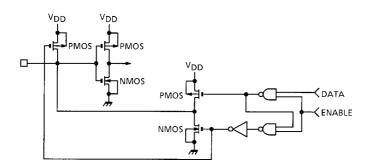

#### LCD drive circuit

The LCD drive circuit consists of 16 row drivers and 40 column drivers. When the character font type and the number of lines have been selected by the appropriate command, the valid row drivers automatically output drive waveforms, and the other row drivers output OFF waveforms.

The T7934 0000 to 0300 all have the same type of column driver.

T7934

## • Cursor / blink display control circuit

This circuit generates the cursor or blink display. The cursor or blink is displayed in the digit which corresponds to the DD RAM address set in the Address Counter.

When the Address Counter is 05H, the cursor is displayed as shown below.

Note: The cursor or blink is also displayed when the CG RAM address is set in the Address Counter. In this case, the cursor or blink is displayed regardless of the DD RAM address.

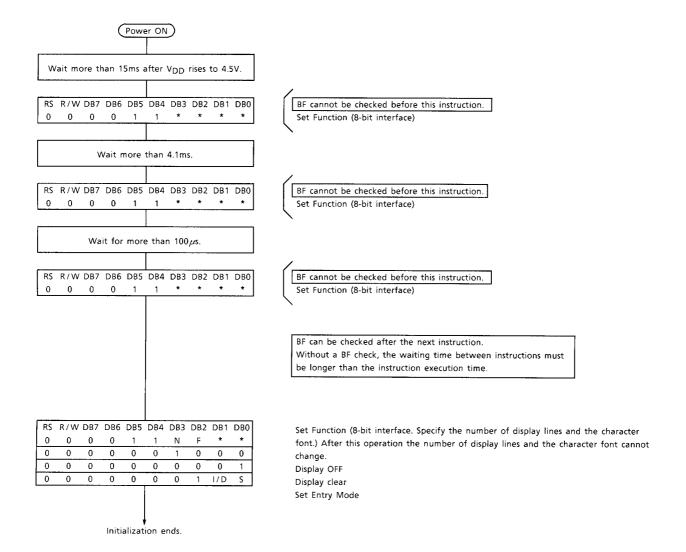

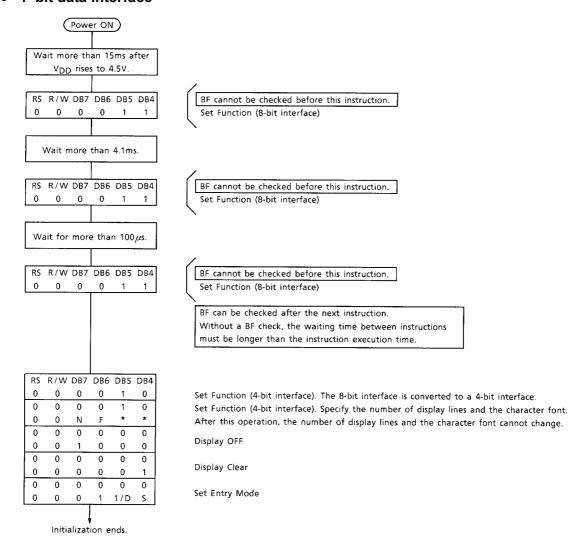

#### Internal reset circuit

When the power is on, the T7934 is automatically initialized by the internal reset circuit. The Busy flag (BF) remains at 1 (Busy state) until initialization ends. The following instructions are executed during initialization.

(1) Display Clear

(4) Display ON / OFF Control  $\cdots$  D = 0 : Display OFF C = 0 : Cursor OFF B = 0 : Blink OFF

Note: The MPU should execute commands (1) to (4), because the internal reset circuit may not move normally according to the power supply condition.

## • Interfacing to the MPU

The T7934 has two methods of interfacing to the MPU. One is the 8-bit data interface and the other is the 4-bit data interface.

- (1) When using the 4-bit interface, the T7934 uses DB4 to DB7 as the interface, and does not use DB0 to DB3. The data from the MPU to the T7934 is sent as 2 sets of 4 bits. First the higher 4 bits are sent to the T7934, then the lower 4 bits are sent.

- The Busy flag and Address Counter data is also sent in 2 parts.

- (2) When the 8-bit interface is used, the T7934 uses DB0 to DB7 as the interface.

#### Instruction

The MPU can directly control two registers. One is the Instruction register (IR) and the other is the Data register (DR).

While the T7934 is executing an instruction, it cannot execute any other instructions (except for the Read Busy flag and Address instruction). The Busy flag is maintained at 1 (Busy state) until the instruction completes. Before the instruction is sent from the MPU to the T7934, the MPU must check that the busy flag is set to 0 (Not Busy state). If the instruction is sent to the T7934 without a Busy check, the MPU must wait the execution time of the instruction before sending the next instruction to the T7934.

|                                |                |                     |    |    | Co | de |    |    |     |    |                                                                                                                                      | Execution                                  |

|--------------------------------|----------------|---------------------|----|----|----|----|----|----|-----|----|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Instruction                    | R <sub>S</sub> | R <u>/W</u><br>(WR) | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0 | Description                                                                                                                          | Time (Max)<br>(f <sub>osc</sub> = 250 kHz) |

| Test                           | 0              | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0  | Do not use.                                                                                                                          | 0 μs                                       |

| Clear<br>Display               | 0              | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1  | Clears the display and sets DD<br>RAM address 0 in Address<br>Counter                                                                | 1.64 ms                                    |

| Return<br>Home                 | 0              | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 1   | *  | Sets DD RAM address 0 in<br>Address Counter and returns<br>display to home position.<br>The contents of the DD RAM do<br>not change. | 1.64 ms                                    |

| Set Entry<br>Mode              | 0              | 0                   | 0  | 0  | 0  | 0  | 0  | 1  | I/D | S  | Sets cursor shift direction and display shift. These operations are executed when data is written.                                   | 40 μs                                      |

| Display<br>ON / OFF<br>Control | 0              | 0                   | 0  | 0  | 0  | 0  | 1  | D  | С   | В  | Sets ON / OFF for all displays (D), cursor ON / OFF (C), cursor position blink (B).                                                  | 40 μs                                      |

|                                   |                                         |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   | Cod | de   |        |                                      |       |    |                                                                                            | Execution                                  |  |  |

|-----------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----|------|--------|--------------------------------------|-------|----|--------------------------------------------------------------------------------------------|--------------------------------------------|--|--|

| Instruction                       | R <sub>S</sub>                          | R/W<br>(WR)                                                                                               | D7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D6                                                | D5  | D4   | D3     | D2                                   | D1    | D0 | Description                                                                                | Time (Max)<br>(f <sub>osc</sub> = 250 kHz) |  |  |

| Cursor /<br>Display<br>Shift      | 0                                       | 0                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                 | 0   | 1    | S/C    | R/L                                  | *     | *  | Shifts cursor and display without changing DD RAM contents                                 | 40 μs                                      |  |  |

| Set<br>Function                   | 0                                       | 0                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                 | 1   | DL   | N      | F                                    | *     | *  | Sets interface data length (DL),<br>number of display lines (N), and<br>character font (F) | 40 μs                                      |  |  |

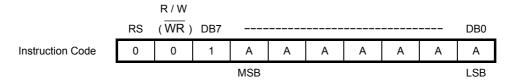

| Set CG<br>RAM<br>Address          | 0                                       | 0                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                 |     | C    | G RAM  | Addre                                | ess   |    | Sets CG RAM Address                                                                        | 40 μs                                      |  |  |

| Set DD<br>RAM<br>Address          | 0                                       | 0                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                   |     | DD R | AM Ac  | Idress                               |       |    | Sets DD RAM Address                                                                        | 40 μs                                      |  |  |

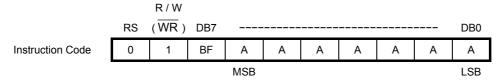

| Read Busy<br>Flag and<br>Address  | 0                                       | 1                                                                                                         | BF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   |     | Addr | ess Co | unter                                |       |    | Reads Busy Flag (BF), and Address Counter contents                                         | 0 μs                                       |  |  |

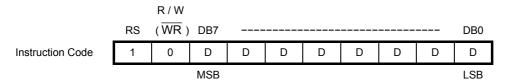

| Write Data<br>to CG or<br>DD RAM  | 1                                       | 0                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Write Data                                        |     |      |        | Writes data into DD RAM or CG<br>RAM | 46 µs |    |                                                                                            |                                            |  |  |

| Read Data<br>from CG or<br>DD RAM | 1                                       | 1                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                   |     | Read | Data   |                                      |       |    | Reads data from DD RAM or CG<br>RAM                                                        | 46 µs                                      |  |  |

| _                                 | I/D=<br>S=1<br>S/C<br>S/C<br>R/L<br>R/L | = 1: Diss<br>= 0: Cu<br>= 1: Shh<br>= 0: Sh<br>1 : 8 b<br>0 : 4 b<br>: 2 li<br>: 5x<br>1 : Bus<br>1 : Bus | crement play Suplay Supplay Su | nt<br>hift On<br>hift<br>nift<br>e Righ<br>e Left | t   | 1    |        |                                      |       |    | _                                                                                          | _                                          |  |  |

\*: Invalid

## Clear Display

When the T7934 executes this instruction, code 20~H (code 20~H must be the "Space code") is written to every address in the DD RAM. This command resets the DD RAM address in the Address Counter.

The display is inhibited and the cursor or blink is moved to the left of the display. (In 2–Line Display mode, the cursor moves to the left of 1st line of the display.) The I / D of Entry mode is set to 0. The S of Entry mode does not change.

#### Return Home

The DD RAM address in the Address Counter is reset by this instruction, and the display shift is cancelled (this is known as returning to the home position). The contents of the DD RAM do not change. The cursor or blink moves to the extreme left of the display. (In 2–Line Display mode, the cursor moves to the extreme left of the 1st line of the display.)

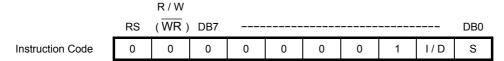

#### Set Entry Mode

I/D: The Address Counter is incremented (I/D=1) or decremented (I/D=0) after the data has been written to or read from DD RAM.

The same is true when date is written to or read from CG RAM.

S : If S = 1, the entire display is shifted left (I / D = 1) or right (I / D = 0) when data is written to the DD RAM. (The cursor position does not move)

If S = 0, the display is not shifted.

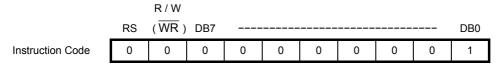

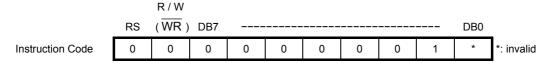

# • Display ON / OFF Control

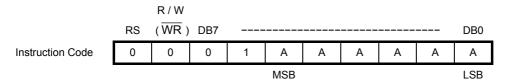

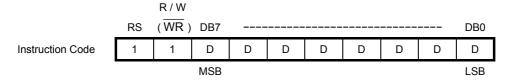

| R / W | RS (WR) DB7 | DB0 |

D: D = 1, display is ON; D = 0, display is OFF.

When D is reset, the contents of the DD RAM do not change. Therefore, the contents can be displayed as before by setting D.

C: C = 1, cursor display is ON; C = 0, cursor display is OFF.

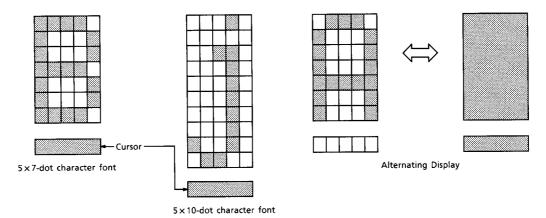

$5\times7\text{--dot}$  character font: cursor display uses 5 dots on the 8th line

$5 \times 10$ -dot character font: cursor display uses 5 dots on the 11th line

B: B = 1, character blink is ON (same position of cursor position); B = 0, character blink is OFF.

Cursor and blink can operate at same time.

Blink period: Font  $5 \times 7$ -dot,  $f_{osc} = 250 \text{ kHz}$

$(1/250 \text{ k}) \times 5 \times 80 \times 8 \times 32 = 409.6 \text{ (ms)}$

Font  $5 \times 10$ -dot, fosc = 250 kHz  $(1 / 250 \text{ k}) \times 5 \times 80 \times 11 \times 32 = 563.2 \text{ (ms)}$

(1) Cursor display example

(2) Blink display example

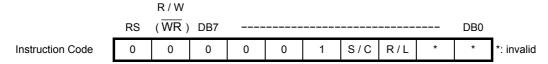

# • Cursor Display Shift

When this instruction is executed, the cursor or display is shifted to the right or left without display data being written or read.

In 2–Line Display mode, the cursor is shifted from the 40th digit of the 1st line to the 1st digit of the 2nd line.

| S/C | R/L | Functions                                                                             | Address Counter<br>(AC) |

|-----|-----|---------------------------------------------------------------------------------------|-------------------------|

| 0   | 0   | Shift the cursor to the left.                                                         | AC = AC - 1             |

| 0   | 1   | Shift the cursor to the right.                                                        | AC = AC + 1             |

| 1   | 0   | Shift the whole display to the left. The cursor follows the display shift direction.  | AC = AC                 |

| 1   | 1   | Shift the whole display to the right. The cursor follows the display shift direction. | AC = AC                 |

When S / C = 1, the contents of the Address Counter do not change.

#### Set Function

DL: DL = 1, 8-bit data interface (DB0 to DB7)

DL = 0, 4-bit data interface (DB4 to DB7)

N : N = 0, 1-Line Display mode

N = 1, 2-Line Display mode

$F : F = 0, \quad 5 \times 7$ -dot character font

F = 1,  $5 \times 10$ -dot character font

Note: Execute this instruction first in a program before executing any other instructions (except for the Busy Flag / Address Read instruction).

After this instruction has been used once, it cannot be used again, except to change the DL bit setting.

| N | F | No. of<br>Display Lines | Character Font | Duty   | Note                                                           |

|---|---|-------------------------|----------------|--------|----------------------------------------------------------------|