### AM / FM - PLL

### **Description**

The U4285BM is an integrated circuit in BICMOS technology for frequency synthesizers. It performs all the functions of a PLL radio tuning system and is controlled

by an I<sup>2</sup>C bus. The device is designed for all frequency synthesizer applications in radio receivers, as well as RDS ( **R**adio **D**ata **S**ystem ) applications.

#### **Features**

- Reference oscillator up to 15 MHz

- Two programmable 16 bit dividers adjustable from 2 to 65535

- Fine tuning steps:

$AM \ge 1 \text{ kHz}$  $FM \ge 2 \text{ kHz}$

- 4 programmable switching outputs (open drain up to 15 V)

- Few external component required due to integrated loop-push-pull stage for AM/FM

- High signal/ noise ratio

### **Ordering Information**

| Extended Type Number | Package       | Remarks                       |

|----------------------|---------------|-------------------------------|

| U4285BM-AFS          | SSO20 plastic |                               |

| U4285BM-AFSG3        | SSO20 plastic | Taping according to IEC-286-3 |

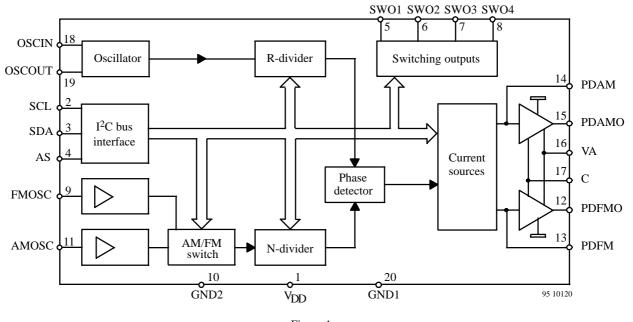

### **Block Diagram**

Figure 1.

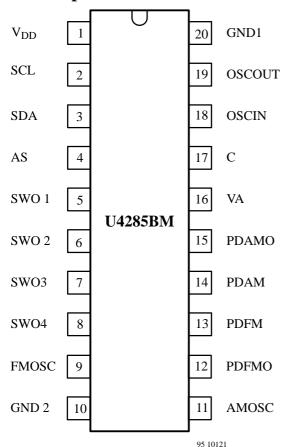

#### **Pin Description**

| Pin | Symbol   | Function                   |

|-----|----------|----------------------------|

| 1   | $V_{DD}$ | Supply voltage             |

| 2   | SCL      | I <sup>2</sup> C bus clock |

| 3   | SDA      | I <sup>2</sup> C bus data  |

| 4   | AS       | Address selection          |

| 5   | SWO 1    | Switching output 1         |

| 6   | SWO 2    | Switching output 2         |

| 7   | SWO3     | Switching output 3         |

| 8   | SWO4     | Switching output 4         |

| 9   | FMOSC    | FM oscillator input        |

| 10  | GND 2    | Ground 2 (analog)          |

| 11  | AMOSC    | AM oscillator input        |

| 12  | PDFMO    | FM analogue output         |

| 13  | PDFM     | FM current output          |

| 14  | PDAM     | AM current output          |

| 15  | PDAMO    | AM analogue output         |

| 16  | VA       | Analogue supply voltage    |

| 17  | С        | Capacitor                  |

| 18  | OSCIN    | Oscillator input           |

| 19  | OSCOUT   | Oscillator output          |

| 20  | GND1     | Ground 1 (digital)         |

### **Functional Description**

The U4285BM is controlled via the 2-wire I<sup>2</sup>C bus. For programming there are one module address byte, two subaddress bytes and five data bytes.

The module address contains a programmable address bit A 1 which with address select input AS (Pin 4) makes it possible to operate two U4285BM in one system. If bit A 1 is identical with the status of the address select input AS, the chip is selected .

The subaddress determines which one of the data bytes is transmitted first. If subaddress of R-divider is transmitted, the sequence of the next data bytes is DB 0 (Status), DB 1 and DB 2.

If subaddress of N-divider is transmitted, the sequence of the next data bytes is DB 3 and DB 4. The bit organisation of the module address, subaddress and 5 data bytes are shown in figure 2.

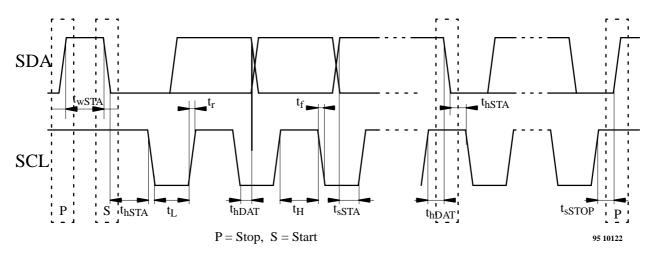

Each transmission on the  $I^2C$  bus begins with the "START"- condition and has to be ended by the "STOP"-condition (see figure 3).

The integrated circuit U4285BM has two separate inputs for AM and FM oscillator. Pre-amplified AM and FM signals are fed to the 16 bit N-divider via AM/FM switch. AM/FM switch is controlled by software. Tuning steps can be selected by 16 bit R-divider. Further there is a digital memory phase detector. There are two separate current sources for AM and FM amplifier (charge pump) as given in electrical characterisitics. It allows independent adjustment of gain, whereby providing high current for high speed tuning and low current for stable tuning.

## **Bit Organization**

|                        | MSB  |           |           |      |           |           |           | LSB       |  |

|------------------------|------|-----------|-----------|------|-----------|-----------|-----------|-----------|--|

| Module address         | 1    | 1         | 0         | 0    | 1         | 0         | 0/1       | 0         |  |

|                        | A7   | A6        | A5        | A4   | A3        | A2        | A1        | A0        |  |

|                        |      |           |           |      |           |           |           |           |  |

| Subaddress (R-divider) | X    | X         | X         | 0    | 0         | 1         | X         | X         |  |

|                        |      |           |           |      |           |           |           |           |  |

| Subaddress (N-divider) | X    | X         | X         | X    | 1         | 1         | X         | X         |  |

|                        |      |           |           |      |           |           |           |           |  |

|                        | MSB  |           |           |      |           |           |           | LSB       |  |

| Data byte 0 (Status)   | SWO1 | SWO2      | SWO3      | SWO4 | AM/<br>FM | PD<br>ANA | PD<br>POL | PD<br>CUR |  |

|                        | D7   | D6        | D5        | D4   | D3        | D2        | D1        | D0        |  |

|                        |      |           |           |      |           |           |           |           |  |

| Data byte 1            | 215  |           |           | R-di | vider     |           |           | 28        |  |

|                        |      | •         |           |      |           |           |           |           |  |

| Data byte 2            | 27   |           |           | R-di | vider     |           |           | 20        |  |

|                        |      | •         |           |      |           |           |           | •         |  |

| Data byte 3            | 215  | N-divider |           |      |           |           |           | 28        |  |

|                        |      |           |           |      |           |           |           |           |  |

| Data byte 4            | 27   |           | N-divider |      |           |           |           |           |  |

|          | LOW                       | HIGH              |

|----------|---------------------------|-------------------|

| AM/FM    | FM-operation AM-operation |                   |

| PD – ANA | PD analog                 | TEST              |

| PD – POL | Negative polarity         | Positive polarity |

| PD – CUR | Output current 2          | Output current 1  |

Figure 2.

# **U4285BM**

### **Transmission Protocol**

|   | MSB L   | SB |   |            |   |        |   |        |   |        |   |   |

|---|---------|----|---|------------|---|--------|---|--------|---|--------|---|---|

| S | Address |    | A | Subaddress | A | Data 0 | A | Data 1 | A | Data 2 | A | P |

|   | A7      | A0 |   | R-divider  |   |        |   |        |   |        |   |   |

|   | MSB L   | SB |   |            |   |        |   |        |   |   |

|---|---------|----|---|------------|---|--------|---|--------|---|---|

| S | Address |    | A | Subaddress | A | Data 3 | A | Data 4 | A | P |

|   | A7      | A0 |   | N-divider  |   |        |   | A      |   |   |

S = Start P = Stop A = Acknowledge

Figure 3.

## **Absolute Maximum Ratings**

| Par                                                         | rameters                         | Symbol                                 | Value                    | Unit   |

|-------------------------------------------------------------|----------------------------------|----------------------------------------|--------------------------|--------|

| Supply voltage                                              | Pin 1                            | V <sub>DD</sub>                        | -0.3 to +6               | V      |

| Input voltage                                               | Pins 2, 3, 4, 9, 11, 18 and 19   | $V_{\rm I}$                            | $-0.3$ to $V_{DD} + 0.3$ | V      |

| Output current                                              | Pins 3, 5, 6, 7 and 8            | I <sub>O</sub>                         | −1 to +5                 | mA     |

| Output drain voltage                                        | Pins 5, 6, 7 and 8               | V <sub>OD</sub>                        | 15                       | V      |

| Analogue supply voltage with 220 $\Omega$ seriell resistant | Pin 16 ce 2 minutes <sup>1</sup> | $egin{array}{c} V_A \ V_A \end{array}$ | 6 to 15<br>24            | V<br>V |

| Output current                                              | Pins 12 and 15                   | $I_{AO}$                               | −1 to +20                | mA     |

| Ambient temperature range                                   | 2                                | T <sub>amb</sub>                       | -30 to +85               | °C     |

| Storage temperature range                                   |                                  | T <sub>stg</sub>                       | -40 to +125              | °C     |

| Junction temperature                                        |                                  | Tj                                     | 125                      | °C     |

| Electrostatic handling (moderated method 3015.7: all supply |                                  | ± V <sub>ESD</sub>                     | 1000                     | V      |

corresponding our application circuit (page 8)

### **Thermal Resistance**

| Parameters       | Symbol     | Value | Unit |

|------------------|------------|-------|------|

| Junction ambient | $R_{thJA}$ | 160   | K/W  |

### **Electrical Characteristics**

$V_{DD}$  = 5 V,  $V_A$  = 10 V,  $T_{amb}$  = 25°C, unless otherwise specified

| Parameters                             | Test conditions / Pin              |        | Symbol                | Min. | Тур. | Max.     | Unit              |

|----------------------------------------|------------------------------------|--------|-----------------------|------|------|----------|-------------------|

| Supply voltage                         | Pin                                | 1      | $V_{\mathrm{DD}}$     | 4.5  | 5.0  | 5.5      | V                 |

| Quiescent supply current               | AM-mode Pin                        | 1      | $I_{DD}$              |      | 4.0  | 7.0      | mA                |

|                                        | FM-mode                            |        |                       |      | 4.0  | 7.0      |                   |

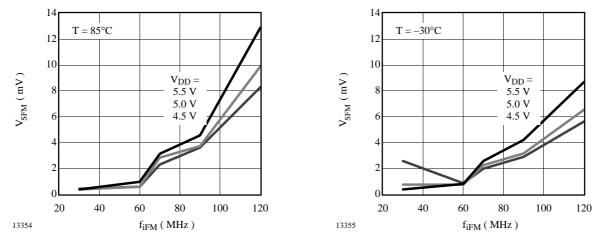

| FM input sensitivity, $R_G = 1$        | 50 Ω FMOSC                         |        |                       |      |      |          |                   |

| $f_i = 70 \text{ to } 120 \text{ MHz}$ | Pin                                | 9      | $V_{SFM}$             | 40   |      |          | $mV_{rms}$        |

| $f_i = 160 \text{ MHz}$                | Pin                                | 9      | $V_{SFM}$             | 150  |      |          | $mV_{rms}$        |

| AM input sensitivity, $R_G =$          | 50 Ω AMOSC                         |        |                       |      |      |          |                   |

| $f_i = 0.6 \text{ to } 35 \text{ MHz}$ | Pin                                | 11     | $V_{SAM}$             | 40   |      |          | mV <sub>rms</sub> |

| Oscillator input sensitivity,          | $R_G = 50 \Omega \text{ OSCIN}$    | •      |                       |      |      | •        |                   |

| $f_i = 0.1 \text{ to } 15 \text{ MHz}$ | Pin                                | 18     | V <sub>SOSC</sub>     | 100  |      |          | mV <sub>rms</sub> |

| Switching output SWO 1, S              | SWO 2, SWO 3, SWO 4 (              | open   |                       |      |      | •        |                   |

| Output voltage                         | Pins 5, 6, 7 and                   |        |                       |      |      |          |                   |

| LOW                                    | $I_L = 1 \text{ mA}$               |        | $V_{SWOL}$            |      | 100  | 400      | mV                |

| Output leakage current                 | Pins 5, 6, 7 and                   | 8      |                       |      |      |          |                   |

| HIGH                                   | V5, V6, V7, V8 = 10 V              |        | $I_{OHL}$             |      |      | 100      | nA                |

| Phase detector PDFM                    | 1                                  |        | -                     |      |      |          |                   |

| Output current 1                       | Pin                                |        | $\pm I_{PDFM}$        | 1600 | 2000 | 2400     | μΑ                |

| Output current 2                       | Pin                                |        | $\pm I_{PDFM}$        | 400  | 500  | 600      | μΑ                |

| Leakage current                        | Pin                                | 13   : | $\pm I_{PDFML}$       |      |      | 20       | nA                |

| Phase detector PDAM                    | T                                  |        |                       |      |      | T        | T                 |

| Output current 1                       | Pin                                |        | ± I <sub>PDAM</sub>   | 160  | 200  | 240      | μA                |

| Output current 2                       | Pin                                |        | ± I <sub>PDAM</sub>   | 40   | 50   | 60       | μΑ                |

| Leakage current                        | Pin                                | 14   : | ± I <sub>PDAM</sub> - |      |      | 20       | nA                |

| Analogue output PDFMO,                 | DDAMO                              |        | L                     |      |      |          |                   |

|                                        |                                    | _      |                       |      |      |          |                   |

| Saturation voltage<br>LOW              | Pins 12 and 1. $I = 15 \text{ mA}$ | 3      | $V_{satL}$            |      | 200  | 400      | mV                |

| HIGH                                   | 1 – 13 ma                          |        | V <sub>satH</sub>     | 9.5  | 9.95 | 400      | V                 |

| I <sup>2</sup> C bus SCL, SDA, AS      |                                    |        | Satii                 |      |      |          |                   |

| Input voltage                          | Pins 2, 3 and                      | 4      | V <sub>iBUS</sub>     |      |      |          |                   |

| HIGH                                   |                                    | ·      | ПВОЗ                  | 3.0  |      | $V_{DD}$ | V                 |

| LOW                                    |                                    |        |                       | 0    |      | 1.5      | V                 |

| Output voltage                         | Pin                                | 3      |                       |      |      |          |                   |

| Acknowledge LOW                        | $I_{SDA} = 3 \text{ mA}$           |        | $V_{O}$               |      |      | 0.4      | V                 |

| Clock frequency                        | Pin                                | 2      | $f_{SCL}$             |      |      | 100      | kHz               |

| Rise time SDA, SCL                     | Pins 2 and                         | 3      | t <sub>r</sub>        |      |      | 1        | μs                |

| Fall time SDA, SCL                     | Pins 2 and                         | 3      | $t_{\mathrm{f}}$      |      |      | 300      | ns                |

| Period of SCL                          | Pin                                | 2      |                       |      |      |          |                   |

| HIGH                                   | HIGH                               |        | t <sub>H</sub>        | 4.0  |      |          | μs                |

| LOW                                    | LOW                                |        | $t_{ m L}$            | 4.7  |      |          | μs                |

| Parameters                                        | Test conditions / Pin | Symbol                                                   | Min.                     | Тур. | Max. | Unit                 |

|---------------------------------------------------|-----------------------|----------------------------------------------------------|--------------------------|------|------|----------------------|

| Setup time                                        |                       |                                                          |                          |      |      |                      |

| Start condition Data Stop condition Time space 1) |                       | $t_{ m sSTA} \ t_{ m sDAT} \ t_{ m sSTOP} \ t_{ m wSTA}$ | 4.7<br>250<br>4.7<br>4.7 |      |      | μs<br>ns<br>μs<br>μs |

| Hold time                                         |                       |                                                          |                          |      |      |                      |

| Start condition<br>DATA                           |                       | t <sub>hSTA</sub><br>t <sub>hDAT</sub>                   | 4.0<br>0                 |      |      | μs<br>μs             |

$<sup>^{1)}</sup>$  This is a space of time where the bus must be free from data transmission and before a new transmission can be started

### **Bus Timing**

Figure 4.

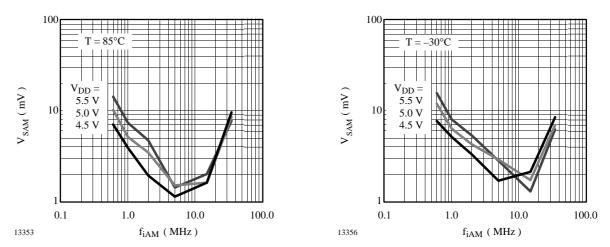

Figure 5. FM input sensitivity

Figure 6. AM input sensitivity

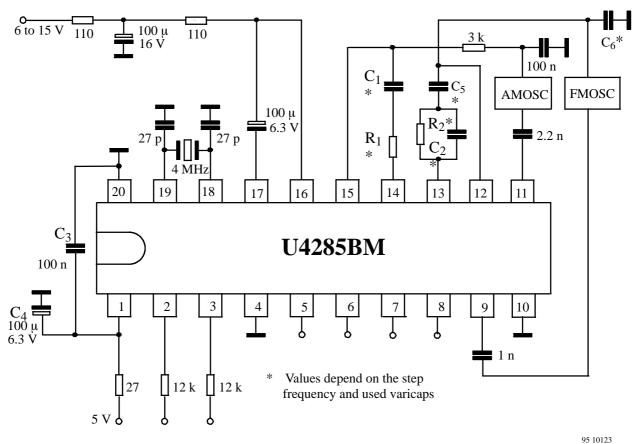

### **Application Circuit**

Figure 7.

#### **Recommendations for Applications**

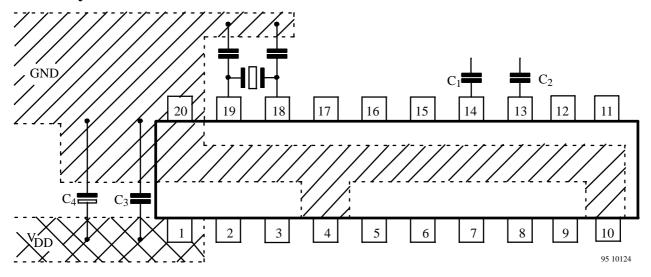

- $C_3 = 100 \text{ nF}$  should be very close to Pin 1 ( $V_{DD}$ ) and Pin 20 (GND 1)

- GND 2 (Pin 10 analogue ground) and GND 1

(Pin 20 digital ground) must be connected according to figure 8

- 4 MHz crystal must be very close to Pin 18 and Pin 19

- Components of the charge pump (C<sub>1</sub>/R<sub>1</sub> for AM and C<sub>2</sub>/R<sub>2</sub> for FM) should be very close to Pin 14 with respect to Pin 13.

### **PCB-Layout**

Figure 8.

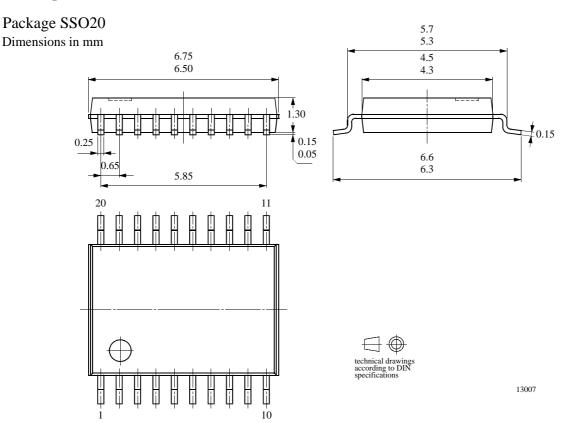

# **Package Information**

# **U4285BM**

### **Ozone Depleting Substances Policy Statement**

It is the policy of TEMIC TELEFUNKEN microelectronic GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC TELEFUNKEN microelectronic GmbH** semiconductor division has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC products for any unintended or unauthorized application, the buyer shall indemnify TEMIC against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC TELEFUNKEN microelectronic GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2831, Fax number: 49 (0)7131 67 2423