# BICMOS INTEGRATED CIRCUIT $\mu$ PC1934

### DC-DC CONVERTER CONTROL IC

### **DESCRIPTION**

The  $\mu$  PC1934 is an IC that controls a low-voltage input DC-DC converter. This IC is suitable for an operation with 3-V, 3.3-V input or a lithium ion secondary battery input, because the minimum operation supply voltage is 2.5 V. Because of its wide operating voltage range, it can also be used to control DC-DC converters that use an AC adapter for input.

### **FEATURES**

- Low supply voltage: 2.5 V (MIN.)

- Operating voltage range: 2.5 to 20 V (breakdown voltage: 30 V)

- Timer latch circuit for short-circuit protection.

- $\bullet$  Ceramic capacitor with low capacitance (0.1  $\mu$  F) can be used for short-circuit protection.

- Open drain outputs (Each of the outputs can be used to control a step-down converter, a step-up converter and an inverted converter.)

- Can control two output channels.

### ORDERING INFORMATION

| Part Number        | Package                              |  |

|--------------------|--------------------------------------|--|

| $\mu$ PC1934GR-1JG | 16-pin plastic SSOP (5.72 mm (225))  |  |

| $\mu$ PC1934GR-PJG | 16-pin plastic TSSOP (5.72 mm (225)) |  |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

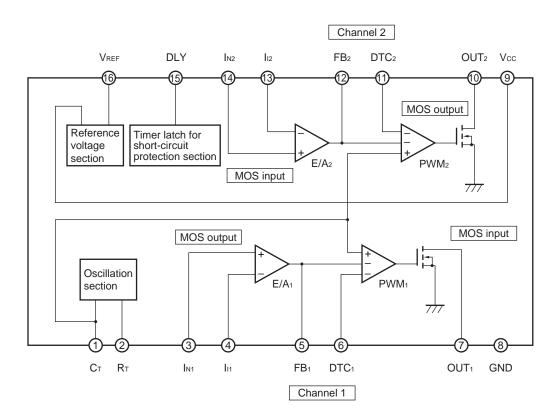

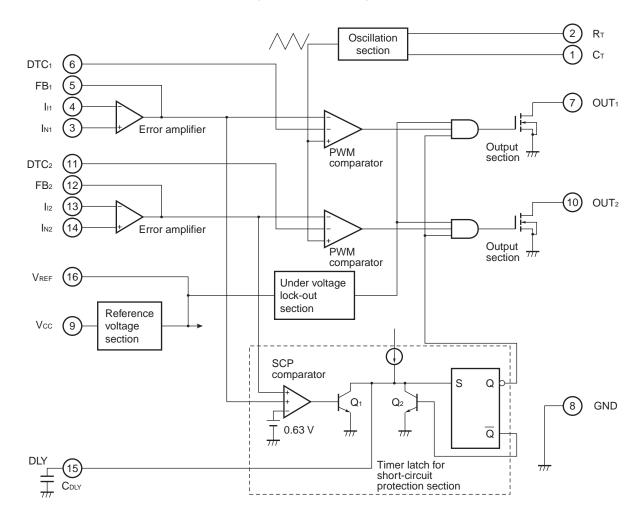

### **BLOCK DIAGRAM**

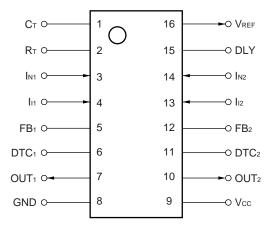

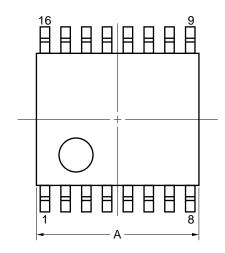

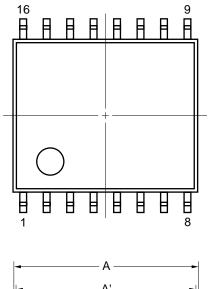

## PIN CONFIGURATION (Top View)

16-pin plastic SSOP (5.72 mm (225))

• μ PC1934GR-1JG

16-pin plastic TSSOP (5.72 mm (225))

• μ PC1934GR-PJG

### **PIN FUNCTIONS**

| Pin No. | Symbol           | Function                                     | Pin No. | Symbol           | Function                                                   |

|---------|------------------|----------------------------------------------|---------|------------------|------------------------------------------------------------|

| 1       | Ст               | Frequency setting capacitor connection       | 9       | Vcc              | Power supply                                               |

| 2       | R⊤               | Frequency setting resistor connection        | 10      | OUT <sub>2</sub> | Channel 2 open drain output                                |

| 3       | l <sub>N1</sub>  | Channel 1 error amplifier non-inverted input | 11      | DTC <sub>2</sub> | Channel 2 dead time setting                                |

| 4       | l <sub>11</sub>  | Channel 1 error amplifier inverted input     | 12      | FB <sub>2</sub>  | Channel 2 error amplifier output                           |

| 5       | FB <sub>1</sub>  | Channel 1 error amplifier output             | 13      | l <sub>12</sub>  | Channel 2 error amplifier inverted input                   |

| 6       | DTC <sub>1</sub> | Channel 1 dead time setting                  | 14      | l <sub>N2</sub>  | Channel 2 error amplifier non-inverted input               |

| 7       | OUT <sub>1</sub> | Channel 1 open drain output                  | 15      | DLY              | Delay capacitor connection of short-<br>circuit protection |

| 8       | GND              | Ground                                       | 16      | VREF             | Reference voltage output                                   |

### **CONTENTS**

|   | 1. | ELE | CTRICAL SPECIFICATIONS                                                            | 5  |

|---|----|-----|-----------------------------------------------------------------------------------|----|

| * | 2. | CON | IFIGURATION AND OPERATION OF EACH BLOCK                                           | 10 |

|   |    |     | Reference Voltage Generator                                                       |    |

|   |    |     | Oscillator                                                                        |    |

|   |    |     | Under Voltage Lock-out Circuit                                                    |    |

|   |    | 2.4 | -                                                                                 |    |

|   |    | 2.5 | PWM Comparators                                                                   |    |

|   |    | 2.6 | Timer Latch-Method Short Circuit Protection Circuit                               |    |

|   |    | 2.7 | Output Circuit                                                                    |    |

|   |    |     | ·                                                                                 |    |

| * | 3. | тои | ES ON USE                                                                         | 12 |

|   |    | 3.1 | Setting the Output Voltage                                                        | 12 |

|   |    | 3.2 | Setting the Oscillation Frequency                                                 | 13 |

|   |    | 3.3 | Preventing Malfunction of the Timer Latch-Method Short Circuit Protection Circuit | 13 |

|   |    | 3.4 | Connecting Unused Error Amplifiers                                                | 13 |

|   |    | 3.5 | ON/OFF Control                                                                    | 14 |

|   |    | 3.6 | Notes on Actual Pattern Wiring                                                    | 14 |

| * | 4. | APP | LICATION EXAMPLE                                                                  | 15 |

|   |    |     | Application Example                                                               |    |

|   |    |     | List of External Parts                                                            |    |

|   |    |     |                                                                                   |    |

|   | 5. | PAC | KAGE DRAWINGS                                                                     | 16 |

|   | 6  | DEC | COMMENDED SOI DEPING CONDITIONS                                                   | 10 |

### 1. ELECTRICAL SPECIFICATIONS

Absolute Maximum Ratings (unless otherwise specified, TA = 25 °C)

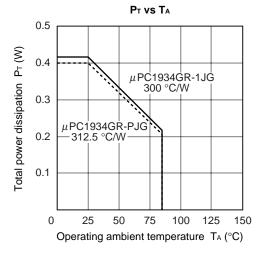

| Parameter                          | Symbol                                   | μ PC1934GR-1JG | μ PC1934GR-PJG | Unit |

|------------------------------------|------------------------------------------|----------------|----------------|------|

| Supply voltage                     | Vcc                                      | 30             |                | V    |

| Output voltage                     | Vo                                       | 3              | V              |      |

| Output current (open drain output) | lo                                       | 2              | mA             |      |

| Total power dissipation            | power dissipation P <sub>T</sub> 417 400 |                | 400            | mW   |

| Operating ambient temperature      | TA                                       | -20 to +85     |                | °C   |

| Storage temperature                | T <sub>stg</sub>                         | -55 to + 150   |                | °C   |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

### **Recommended Operating Conditions**

| Parameter             | Symbol | MIN. | TYP. | MAX. | Unit |

|-----------------------|--------|------|------|------|------|

| Supply voltage        | Vcc    | 2.5  |      | 20   | V    |

| Output voltage        | Vo     | 0    |      | 20   | V    |

| Output current        | lo     |      |      | 20   | mA   |

| Operating temperature | TA     | -20  |      | +85  | °C   |

| Oscillation frequency | fosc   | 20   |      | 1000 | kHz  |

★ Caution The recommended operating range may be exceeded without causing any problems provided that the absolute maximum ratings are not exceeded. However, if the device is operated in a way that exceeds the recommended operating conditions, the margin between the actual conditions of use and the absolute maximum ratings is small, and therefore thorough evaluation is necessary. The recommended operating conditions do not imply that the device can be used with all values at their maximum values.

Electrical Characteristics (unless otherwise specified,  $T_A = 25$  °C,  $V_{CC} = 3$  V, fosc = 100 kHz)

| Block         | Parameter                          | Symbol                       | Conditions                                      | MIN. | TYP. | MAX. | Unit |

|---------------|------------------------------------|------------------------------|-------------------------------------------------|------|------|------|------|

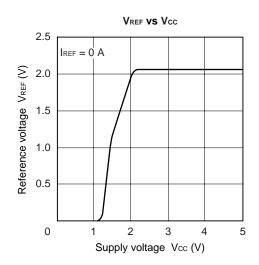

| Under         | Start-up voltage                   | Vcc (L-H)                    | Iref = 0.1 mA                                   |      | 1.57 |      | V    |

| voltage       | Operation stop voltage             | Vcc (H-L)                    | Iref = 0.1 mA                                   |      | 1.5  |      | V    |

| Lock-out      | Hysteresis voltage                 | Vн                           | Iref = 0.1 mA                                   | 30   | 70   |      | mV   |

| section       | Reset voltage (timer latch)        | Vccr                         | Iref = 0.1 mA                                   |      | 1.0  |      | V    |

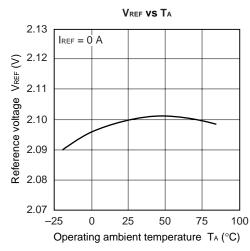

| Reference     | Reference voltage                  | V <sub>REF</sub>             | Iref = 1 mA                                     | 2.0  | 2.1  | 2.2  | V    |

| Voltage       | Line regulation                    | REGIN                        | 2.5 V≤Vcc≤20 V                                  |      | 2    | 12.5 | mV   |

| section       | Load regulation                    | REG∟                         | 0.1 mA≤lref≤1 mA                                |      | 2    | 7.5  | mV   |

|               | Temperature coefficient            | $\Delta V_{REF}/\Delta T$    | -20 °C≤Ta≤+85 °C, IREF = 0 A                    |      | 0.5  |      | %    |

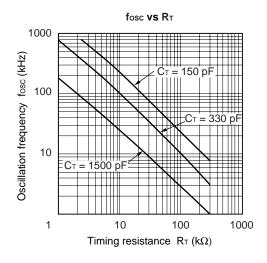

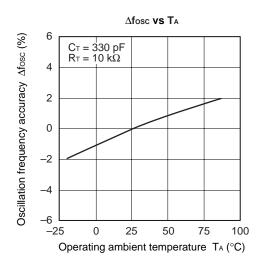

| Oscillation   | fosc setting accuracy              | $\Delta fosc$                | R <sub>T</sub> = 11 kΩ, C <sub>T</sub> = 330 pF | -15  |      | +15  | %    |

| section       | fosc total stability               | Δfosc                        | –20 °C≤T <sub>A</sub> ≤+85 °C,                  | -30  |      | +30  | %    |

|               |                                    |                              | 2.5 V≤Vcc≤20 V                                  |      |      |      |      |

| Dead time     | Input bias current                 | lвD                          |                                                 |      | 0.4  | 1.0  | μΑ   |

| control       | Low-level threshold voltage        | V <sub>TH (L)</sub>          | Duty = 100 %                                    |      | 1.2  |      | V    |

| section       | High-level threshold voltage       | V <sub>TH</sub> (H)          | Duty = 0 %                                      |      | 1.6  |      | V    |

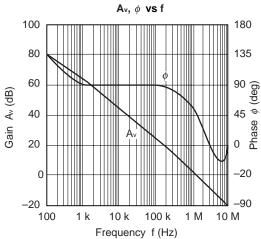

| Error         | Input offset voltage               | Vio                          |                                                 | -10  |      | +10  | mV   |

| Amplifier     | Input offset current               | lio                          |                                                 | -100 |      | +100 | nA   |

| section       | Input bias current                 | lв                           |                                                 | -100 |      | +100 | nA   |

|               | Common mode input voltage range    | VIMC                         |                                                 | 0    |      | 0.4  | V    |

|               | Open loop gain                     | Av                           | Vo = 0.3 V                                      | 70   | 80   |      | dB   |

|               | Unity gain                         | funity                       | Vo = 0.3 V                                      |      | 1.5  |      | MHz  |

|               | Maximum output voltage (+)         | V <sub>ом</sub> <sup>+</sup> | Io = -45 μA                                     | 1.6  | 2    |      | V    |

| +             | Maximum output voltage (-)         | Vом <sup>-</sup>             | Io = 45 μA                                      |      | 0.02 | 0.5  | V    |

|               | Output sink current                | losink                       | V <sub>FB</sub> = 0.5 V                         | 0.8  | 1.4  |      | mA   |

|               | Output source current              | lOsource                     | V <sub>FB</sub> = 1.6 V                         |      | -70  | -45  | μΑ   |

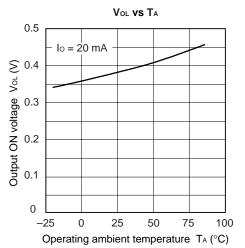

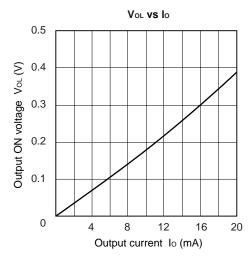

| Output        | Drain cutoff current               | ILEAK                        | Vo = 30 V                                       |      |      | 100  | μΑ   |

| section       | Output ON voltage                  | Vol                          | R <sub>L</sub> = 150 Ω                          |      | 0.2  | 0.6  | V    |

|               | Rise time                          | tr                           | R <sub>L</sub> = 150 Ω                          |      | 50   |      | ns   |

|               | Fall time                          | <b>t</b> f                   | R <sub>L</sub> = 150 Ω                          |      | 60   |      | ns   |

| Short-circuit | Input sense voltage                | Vтн                          |                                                 | 0.5  | 0.63 | 0.75 | V    |

| Protection    | UV sense voltage                   | Vuv                          |                                                 | 0.6  | 0.8  | 0.95 | V    |

| section       | Source current on short-circuiting | louv                         |                                                 | 1.0  | 1.6  | 2.5  | μΑ   |

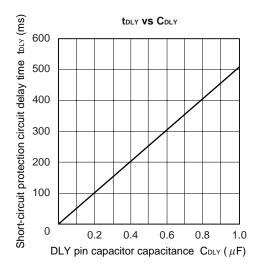

|               | Delay time                         | <b>t</b> DLY                 | CDLY = $0.1 \mu F$                              |      | 50   |      | ms   |

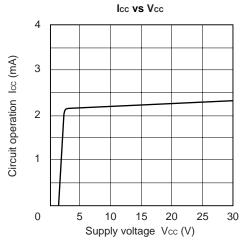

| Overall       | Circuit operation current          | Icc                          | Vcc = 3 V                                       | 1.4  | 2.2  | 3.7  | mA   |

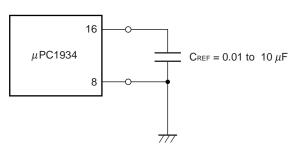

Caution Connect a capacitor of 0.01 to 10  $\mu$  F to the  $\mbox{V}_{\mbox{\scriptsize REF}}$  pin.

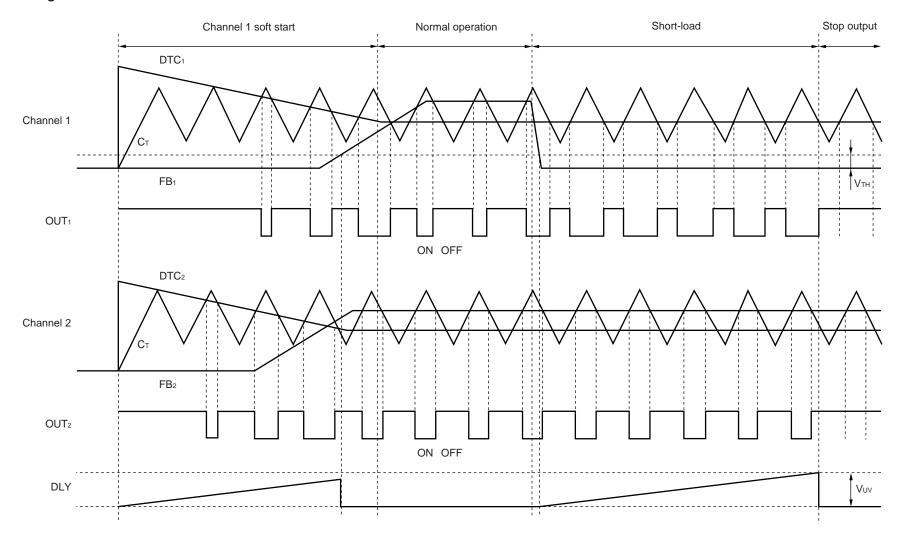

### **Timing Charts**

**Remark** These timings are an example when the channel 1 output has been a short- load. The outputs of channel 1 and 2 are also stopped when a short-circuit protection circuit starts operation by detecting a short- load of channel 2.

### Typical Characteristic Curves (unless otherwise specified, Vcc = 3 V, fosc = 100 kHz, TA = 25 °C) (Nominal)

### **★ 2. CONFIGURATION AND OPERATION OF EACH BLOCK**

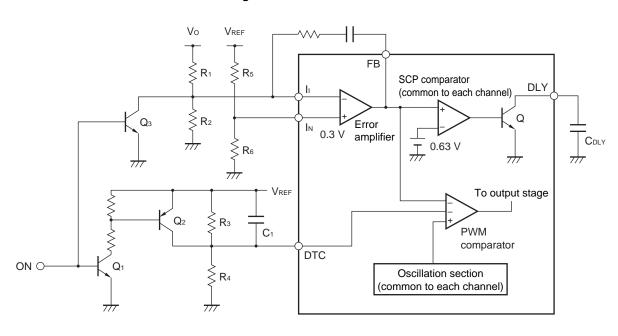

Figure 2-1 Block Diagram

### 2.1 Reference Voltage Generator

The reference voltage generator is comprised of a band-gap reference circuit, and outputs a temperature-compensated reference voltage (2.1 V). The reference voltage can be used as the power supply for internal circuits, or as a reference voltage, and can also be accessed externally via the VREF pin (pin 16).

### 2.2 Oscillator

The oscillator self-oscillates if a timing resistor is attached to the R<sub>T</sub> pin (pin 2). Also, the oscillator outputs the symmetrical triangular waveform if a timing capacitor is attached to the C<sub>T</sub> pin (pin 1). This oscillator waveform is input to the non-inverted input pins of the two PWM comparators to determine the oscillation frequency.

### 2.3 Under Voltage Lock-out Circuit

The under voltage lock-out circuit prevents malfunctioning of the internal circuits when the supply voltage is low, such as when the supply voltage is first applied, or when the power supply is interrupted. When the voltage is low, the two output transistors are cut off at the same time.

### 2.4 Error Amplifiers

The circuits of the error amplifiers E/A<sub>1</sub> and E/A<sub>2</sub> are exactly the same. The first stage of the error amplifier is a P-channel MOS transistor input. Be careful of the input voltage ranges (the common mode input voltage ranges are all 0 to 0.4 V (TYP.)).

### 2.5 PWM Comparators

The output ON duty is controlled according to the outputs of the error amplifiers and the voltage input to the Dead Time Control pin.

A triangular waveform is input to the non-inverted pin, and the error amplifier output and Dead Time Control pin voltage are input to the inverted pins of the PWM comparators. Therefore, the output transistor ON period is the period when the triangular waveform is higher than the error amplifier output and Dead Time Control pin voltage (refer to **Timing Charts**).

### 2.6 Timer Latch-Method Short Circuit Protection Circuit

When the converter outputs either a channel or both channels drop, the FB outputs of the error amplifiers of those outputs go low. If the FB output goes lower than the timer latch input detection voltage ( $V_{TH} = 0.63 \text{ V}$ )), then the output of the SCP comparator goes low, and  $Q_1$  goes off.

When Q<sub>1</sub> turns OFF, the constant-current supply charges  $C_{DLY}$  via the DLY pin. The DLY pin is internally connected to a flip-flop. When the DLY pin voltage reaches the UV detection voltage ( $V_{UV} = 0.8 \text{ V (TYP.)}$ ), the output Q of the flip-flop goes low, and the output stage of each channel is latched to OFF (refer to **Figure 2-1 Block Diagram**).

Make the power supply voltage briefly less than the reset voltage (VccR, 1.0 V TYP) to reset the latch circuit when the short-circuit protection circuit has operated.

### 2.7 Output Circuit

The output circuit has an N-channel open-drain output providing an output withstand voltage of 30 V (absolute maximum rating), and an output current of 21 mA (absolute maximum rating).

NEC  $\mu$  PC1934

### **★ 3. NOTES ON USE**

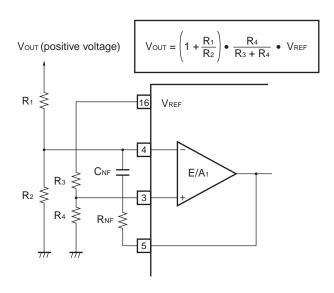

### 3.1 Setting the Output Voltage

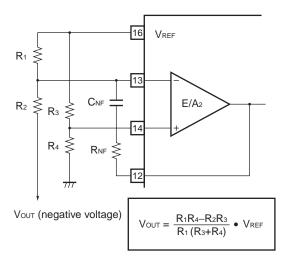

Figure 3-1 illustrates the method of setting the output voltage. The output voltage is obtained using the formula shown in the figure.

The common mode input voltage range of the error amplifier is 0 to 0.4 V (TYP.) for both the error amplifiers,  $E/A_1$  and  $E/A_2$ . Therefore, select a resistor value that gives this voltage range.

Figure 3-1 Setting the Output Voltage

(1) When setting a positive output voltage using error amplifier E/A<sub>1</sub>.

(2) When setting a negative output voltage using error amplifier E/A2.

### 3.2 Setting the Oscillation Frequency

Choose  $R_T$  according to the oscillation frequency (fosc) vs timing resistor ( $C_T$ ,  $R_T$ ) characteristics (refer To **Typical Characteristics Curves fosc vs C\_T, R\_T). The formula below (3-1) gives an approximation of fosc. However, the result of formula 3-1 is only an approximation, and the value must be confirmed in actual operation, especially for high-frequency operation.**

fosc [Hz]  $\cong 0.375/(C_T[F] \times R_T[\Omega])$  (3-1)

### 3.3 Preventing Malfunction of the Timer Latch-Method Short Circuit Protection Circuit

The timer latch short-circuit protection circuit operates when the error amplifier outputs (pin 5 and 12) goes below approximately 0.63 V, and cuts off the output. However, if the rise of the power supply voltage is fast, or if there is noise on the DLY pin (pin 15), the latch circuit may malfunction and cut the output off.

To prevent this, lower the wiring impedance between the DLY pin and the GND pin (pin 8), and avoid applying noise to the DLY pin.

### 3.4 Connecting Unused Error Amplifiers

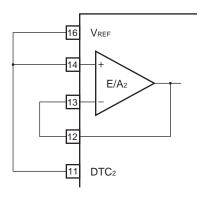

When one of the two control circuits is used, connect the circuit so that the output of the error amplifier of unused circuit is high. Figure 3-2 shows examples of how to connect unused error amplifiers.

Figure 3-2 Examples of Connecting Unused Error Amplifiers

(1) Error amplifier E/A<sub>1</sub>

# 3 + E/A<sub>1</sub> 5 DTC<sub>1</sub>

(2) Error amplifier E/A<sub>2</sub>

$\mu$  PC1934

### 3.5 ON/OFF Control

The ON/OFF control method of the output oscillation is to input the ON/OFF signal from ON as shown in Figure 3-3. The PWM converter can be turned ON/OFF by controlling the level of the DTC pin. However, it is necessary to keep the level of the FB output high so that the timer latch does not start when the PWM converter is OFF. In this circuit example, the FB output level is controlled by controlling the level of the II pin.

Figure 3-3 ON/OFF Control

### (1) When ON is high: OFF status

Q<sub>1</sub>: ON  $\rightarrow$  Q<sub>2</sub>: ON  $\rightarrow$  DTC pin: High level  $\rightarrow$  Output duty of PWM comparator: 0 %

$Q_3: ON \rightarrow I_1$  pin: Low level  $\rightarrow$  FB output: High level  $\rightarrow$  SCP comparator output: High level  $\rightarrow$  Q is ON.  $\rightarrow$  Timer latch stops.

### (2) When ON<sub>3</sub> is low: ON status

$Q_1: \mathsf{OFF} \to Q_2 \text{ is OFF.} \to C_1 \text{ is charged in the sequence of } [\mathsf{V}_\mathsf{REF} \to C_1 \to \mathsf{R}_4] \to \mathsf{DTC} \text{ pin voltage drops.} \to \mathsf{Soft} \text{ start}$   $Q_3: \mathsf{OFF} \to \mathsf{II} \text{ pin: High level} \to \mathsf{FB} \text{ output: Low level} \to \mathsf{SCP} \text{ comparator output: Low level} \to \mathsf{Q}: \mathsf{OFF}$   $\to \mathsf{Charging} \ \mathsf{C}_\mathsf{DLY} \text{ starts (timer latch start)}.$

Caution Keep the high-level voltage of the DTC pin at 1.6 V or higher and the low-level voltage of the l<sub>I</sub> pin within (R6/(R5+R6))•VREF. The maximum voltage that is applied to the l<sub>I</sub> pin must be equal to or lower than VREF.

### 3.6 Notes on Actual Pattern Wiring

When actually carrying out the pattern wiring, it is necessary to separate control-related grounds and power-related grounds, and make sure that they do not share impedances as far as possible. In addition, make sure the high-frequency impedance is lowered using capacitors and other components to prevent noise input to the VREF pin.

### **★ 4. APPLICATION EXAMPLE**

### 4.1 Application Example

Figure 4-1 shows an example circuit for obtaining ±5 V/50 mA from a +3 V power supply.

V<sub>N</sub> = 3 V COM

C: 1 μF

C: 10 μF

Figure 4-1 Chopper-Method Step-up/Inverting-Type Switching Regulator

### 4.2 List of External Parts

The list below shows the external parts.

| Symbol          | Parameter | Function               | Part number | Maker      | Remark            |

|-----------------|-----------|------------------------|-------------|------------|-------------------|

| C <sub>2</sub>  | 10 μ F    | Input stable capacitor | 25SC10M     | SANYO      | OS-CON, SC series |

| C <sub>14</sub> | 68 μ F    | Output capacitor       | 20SA68M     | SANYO      | OS-CON, SA series |

| D <sub>11</sub> |           | Schottkey diode        | D1FS4       | SHINDENGEN |                   |

| L <sub>11</sub> | 100 μ H   | Choke inductor         | 636FY-101M  | токо       | D73F series       |

| Q11, Q12        |           | Buffer transistor      | μ PA609T    | NEC        | Transistor array  |

| Q13             |           | Switching transistor   | 2SB1572     | NEC        |                   |

| C <sub>21</sub> | 68 μ F    | Output capacitor       | 20SA68M     | SANYO      | OS-CON, SA series |

| D21             |           | Schottkey diode        | D1FS4       | SHINDENGEN |                   |

| L21             | 100 μ H   | Choke inductor         | 636FY-101M  | токо       | D73F series       |

| Q21, Q22        |           | Buffer transistor      | μ PA609T    | NEC        | Transistor array  |

| <b>Q</b> 23     |           | Switching transistor   | 2SD2403     | NEC        |                   |

Table 4-1 List of External Parts

Remarks 1. The capacitors that are not specified in the above list are multilayer ceramic capacitors.

2. The resistors that are not specified in the above list are 1/4W resistors.

### 5. PACKAGE DRAWINGS

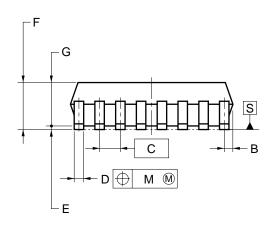

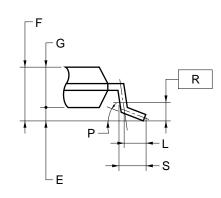

# 16-PIN PLASTIC SSOP (5.72 mm (225))

detail of lead end

### NOTE

Each lead centerline is located within 0.10 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            |

|------|------------------------|

| Α    | 5.2±0.3                |

| В    | 0.475 MAX.             |

| С    | 0.65 (T.P.)            |

| D    | 0.22±0.8               |

| Е    | 0.125±0.075            |

| F    | 1.565±0.235            |

| G    | 1.44                   |

| Н    | 6.2±0.3                |

| I    | 4.4±0.2                |

| J    | 0.9±0.2                |

| K    | $0.17^{+0.08}_{-0.07}$ |

| L    | 0.5±0.2                |

| М    | 0.10                   |

| N    | 0.10                   |

| Р    | 5°±5°                  |

|      |                        |

P16GM-65-225B-4

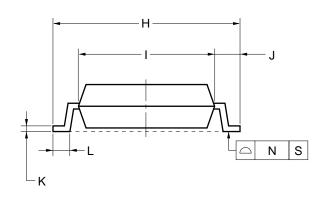

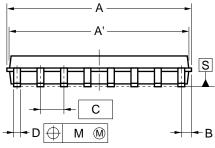

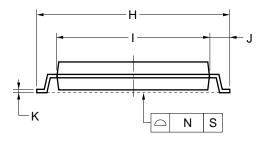

# 16-PIN PLASTIC TSSOP (5.72 mm (225))

detail of lead end

### NOTE

Each lead centerline is located within 0.10 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS               |

|------|---------------------------|

| Α    | 5.15±0.15                 |

| Α'   | 5.0±0.1                   |

| В    | 0.375 MAX.                |

| С    | 0.65 (T.P.)               |

| D    | $0.24^{+0.06}_{-0.04}$    |

| E    | $0.09^{+0.06}_{-0.04}$    |

| F    | 1.01+0.09                 |

| G    | 0.92                      |

| Н    | 6.4±0.2                   |

| ı    | 4.4±0.1                   |

| J    | 1.0±0.2                   |

| K    | $0.145^{+0.055}_{-0.045}$ |

| L    | 0.5                       |

| М    | 0.10                      |

| N    | 0.10                      |

| Р    | 3°+5°                     |

| R    | 0.25                      |

| S    | 0.6±0.15                  |

|      | S16GR-65-P.IG-1           |

S16GR-65-PJG-1

### 6. RECOMMENDED SOLDERING CONDITIONS

Recommended solder conditions for this product are described below.

For details on recommended soldering conditions, refer to Information Document "Semiconductor Device Mounting Technology Manual" (C10535E).

For soldering methods and conditions other than those recommended, consult NEC.

### **Surface Mount Type**

μ PC1934GR-1JG: 16-pin plastic SSOP (5.72 mm (225))

$\mu$  PC1934GR-PJG: 16-pin plastic TSSOP (5.72 mm (225))

| Soldering Method | Soldering Conditions                                                                                                                                  | Symbol of Recommended Conditions |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Infrared reflow  | Package peak temperature: 235 °C, Time: 30 seconds MAX. (210 °C MIN.), Number of times: 3 MAX.                                                        | IR35-00-3                        |

| VPS              | Package peak temperature: 215 °C, Time: 40 seconds MAX. (200 °C MIN.), Number of times: 3 MAX.                                                        | VP15-00-3                        |

| Wave soldering   | Soldering bath temperature: 260 °C MAX., Time: 10 seconds MAX., Number of times: 1, Preheating temperature: 120 °C MAX. (package surface temperature) | WS60-00-1                        |

Caution Do not use two or more soldering methods in combination.

### NOTES FOR BICMOS DEVICES

### (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### 2 HANDLING OF UNUSED INPUT PINS

Note:

No connection for device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. Input levels of devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### (3) STATUS BEFORE INITIALIZATION OF BICMOS DEVICES

Note:

Power-on does not necessarily define initial status of device. Production process of BiCMOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

[MEMO]

- The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

- No part of this document may be copied or reproduced in any form or by any means without the prior written

consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in

this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from use of a device described herein or any other liability arising from use

of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other

intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software, and information in the design of the customer's equipment shall be done under the full responsibility of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices,

the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or

property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety

measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

- "Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.