# MOS INTEGRATED CIRCUIT $\mu$ PD16430A

# 1/2, 1/3, 1/4 DUTY LCD CONTROLLER/DRIVER

The  $\mu$ PD16430A is an LCD controller/driver that enables the display of LCDs of 1/2 duty, 1/3 duty and 1/4 duty cycle.

The LCD controller contained in the  $\mu$ PD16430A employs serial data transfer and uses an automatic increment function for data addresses which eliminates the need to set addresses newly each time.

The LCD driver uses a medium voltage output (14 V max.), which enables higher contrast and a wider viewing angle even with a 1/3 or 1/4 duty cycle.

By using an on-chip drive bias circuit, it is possible to eliminate the need for external resistors.

#### **FEATURES**

- LCD direct drive (medium voltage output: 14 V MAX.)

- · Choice of 3 duty cycles

1/2 duty, 1/3 duty, 1/4 duty

• Display dot number:

1/2 duty: 120 1/3 duty: 160 1/4 duty: 240

· 2 types of drive bias

1/2 bias, 1/3 bias

- · Choice of 4 types of frame frequency

- · Multi-chip configuration possible

- · Control through 8-bit serial interface

- · On-chip power-on reset circuit

- · Low-power dissipation CMOS

- 3.5 to 6.0 V logic supply voltage

## ORDERING INFORMATION

| Part number     | Package                      |

|-----------------|------------------------------|

| μPD16430AGF-3B9 | 80-pin plastic QFP (14 × 20) |

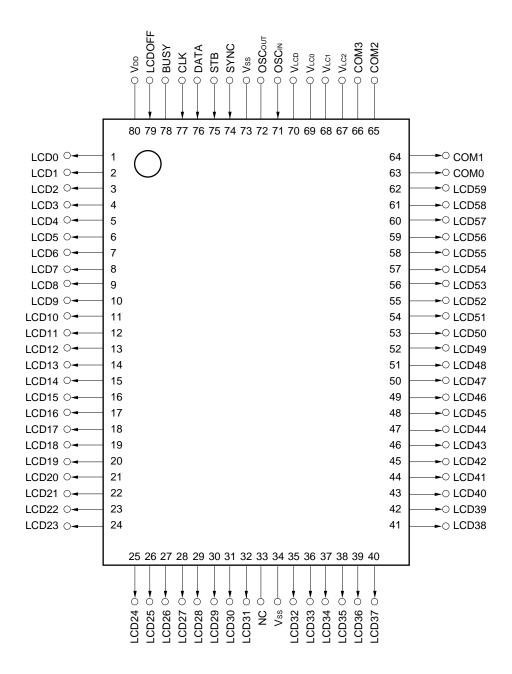

# PIN CONFIGURATION (Top View)

**Remark** Be sure to leave Pin 33 open since it is connected to the lead frame.

# PIN FUNCTIONS

| No.            | Symbol               | I/O    | Output Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|----------------|----------------------|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1<br>to        | LCD0<br>to           | Output | CMOS        | These pins serve as the LCD driver's segment signal output pins.  The following display modes can be selected for the LCD driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| 32<br>35       | LCD31<br>LCD32<br>to |        |             | Duty Bias Display Frame frequency (Hz) Dot No. (fosc = 140 kHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| 62             | LCD59                |        |             | 1/2 1/2 120 <u>fosc</u> <u>fosc</u> <u>fosc</u> <u>fosc</u> <u>fosc</u> <u>7024</u> , 2048 (547) (273) (137) (68)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

|                |                      |        |             | 1/3 1/3 160 <u>fosc</u> <u>fosc</u> <u>fosc</u> <u>fosc</u> <u>fosc</u> 384 , 768 , 1536 , 3072 (365) (182) (91) (46)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                |                      |        |             | 1/4     1/3     240     fosc fosc fosc fosc fosc fosc fosc fosc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|                |                      |        |             | A matrix of these segment signal output pins and COM3, COM2, COM1 and COM0 pins enables the maximum display of 240 dots (1/4 duty selected).  The output voltage of the segment signal output pins is supplied by the VLCD pin.  The output voltage of the segment signal output pin is supplied by dividing and outputting 0 to VLCD voltage using any driving method (any bias method).  Either internal or external voltage dividing resistor can be selected.                                                                                                                                               |  |  |  |  |  |  |  |  |

| 63<br>to<br>66 | COM0<br>to<br>COM3   | Output | CMOS        | These pins serve as the LCD driver's common signal output pins.  The LCD driver can select three display modes.  A matrix of these common signal output pins and LCD59 through LCD0 pins enables the maximum display of 240 dots (1/4 duty selected).  The output voltage of the common signal output pins is supplied by the VLCD pin.  VDD to 14 V voltage is supplied by this pin.  The output voltage of the common signal output pins is supplied by dividing and outputting 0 to VLCD voltage using any driving method (any bias method).  Either internal or external dividing resistor can be selected. |  |  |  |  |  |  |  |  |

| 67<br>68<br>69 | VLC2<br>VLC1<br>VLC0 | _      | _           | These pins serve as the LCD driver's drive voltage generation pins.  The drive voltage can be set by using either these pins or the on-chip drive voltage generation circuit, as specified by command data.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| 70             | VLCD                 | _      | _           | This pin supplies the LCD driver's supply voltage.  VDD to 14 V voltage is supplied to this pin.  The output voltage of the segment signal and command signal output pins is supplied by dividing and outputting the voltage applied to these pins using any driving method (any bias method).  Do not supply a voltage exceeding VDD to the VLCD pin before the device's supply voltage reaches 3.5 V, as this may cause incorrect display.                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| No.      | Symbol          | I/O   | Output Type       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71<br>72 | OSCIN<br>OSCOUT | 1/0   | CMOS              | These pins serve to connect the resistors of the system clock RC oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 34<br>73 | Vss             | _     | _                 | GND pin for device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

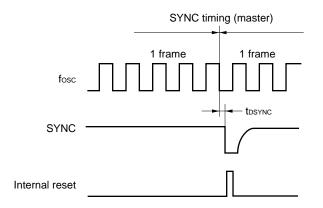

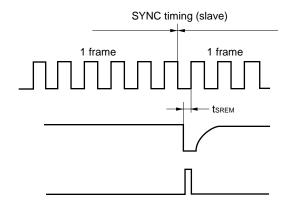

| 74       | SYNC            | I/O   | Nch<br>Open drain | Synchronous signal I/O pin. This pin is used to synchronize two or more $\mu$ PD16430A's. At this time, each chip must be wire-ORed and a pull-up resistor (5 k to 10 k $\Omega$ ) is required. This pin must be pulled up even when only one $\mu$ PD16430A is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

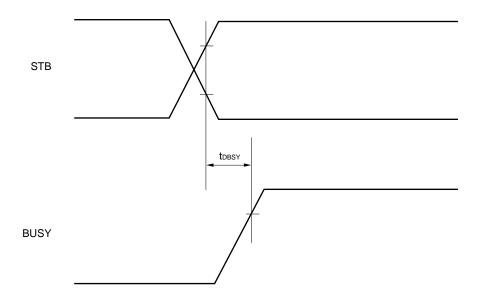

| 75       | STB             | Input |                   | Strobe signal input pin for device's select signal and serial communications.  This pin serves to latch display RAM data outputs, set the command data receive mode and initialize serial communications.  Serial communication is enabled when this signal is a logic low.  When this pin is a logic high, shift clocks that are input are ignored.  (1) Display RAM data output buffer latch function  The internal display RAM data output is latched to the output latch circuit at the rising edge of the STB signal when the BUSY pin outputs a logic high.  However, latch timing depends on the LATCH MD and LATCH flags.  The latch time is 504.5/fosc.  When the BUSY signal is a logic low, latching can cause incorrect display.  (2) Command data receive mode setting  The command data receive mode is set by the rising edge of the STB signal when the BUSY pin outputs a logic high.  Once the command data receive mode is set, the initial byte (8 bits) is processed as a command.  The command data processing time is approximately 300 ns.  The BUSY signal does not change during this time.  (3) Serial communication is initialized by the rising edge or the falling edge of the STB signal when the BUSY pin outputs a logic low.  Once serial communication is initialized, the command data receive mode is started.  During command data decoding or display data RAM interrupt, the STB signal interrupts processing and initializes serial communications. At this time, all displays are turned off (LCDON flag is reset). |

| 76       | DATA            | Input | _                 | This pin inputs serial data for serial communication at the rising edge of the shift clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 77       | CLK             | Input | _                 | This pin inputs a shift clock for serial communication. The signal is output at the rising edge of the shift clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| No. | Symbol | I/O    | Output Type       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----|--------|--------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 78  | BUSY   | Output | Nch<br>Open drain | This pin outputs the serial communication status and the internal data processing status.  When this signal is a logic high, serial communication is executed.  When this signal is a logic low, it indicates that the display RAM data is latched to the output buffer.  When the power-on reset circuit is operating, this pin holds a logic low until a rising or falling signal is input to the STB pin.                                                                                                                                                              |  |  |  |  |  |

| 79  | LCDOFF | Input  | _                 | This pin serves to turn off all the LCD displays.  When a logic low is input to this pin, all LCD displays are turned off.  Display RAM data is maintained.  Since displays are turned off only by the output driver, serial communications can be executed as usual.  To turn on displays, it is necessary to input a logic high to this pin and reset the LCDON flag.                                                                                                                                                                                                   |  |  |  |  |  |

| 80  | VDD    | _      | _                 | This pin is a power supply pin to the device.  A voltage of 3.5 to 6.0 V is supplied to this pin.  When the supply voltage rises from 0 V to 3 V, or when it reaches a value under 3 V and then rises again, the power-on reset circuit starts operating and the device is set to its initialized state.  When the device is in its initialized state, all displays are turned off (segment and common signals are fixed to VLCD).  Do not supply a voltage higher than VDD to the VLCD pin before the supply voltage reaches 3.5 V as this will cause incorrect display. |  |  |  |  |  |

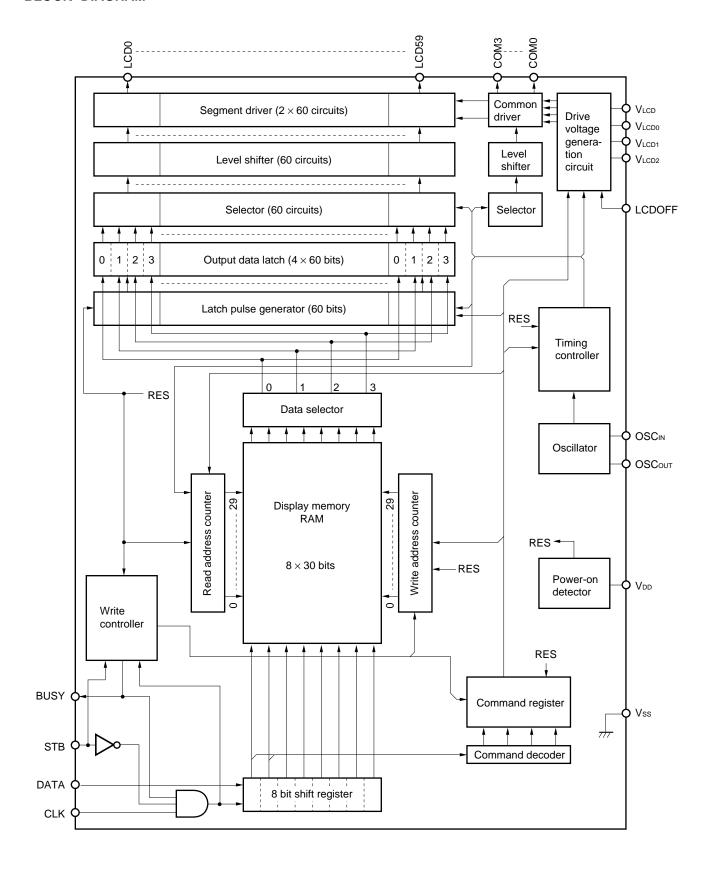

## **BLOCK DIAGRAM**

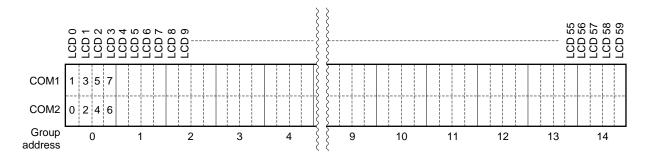

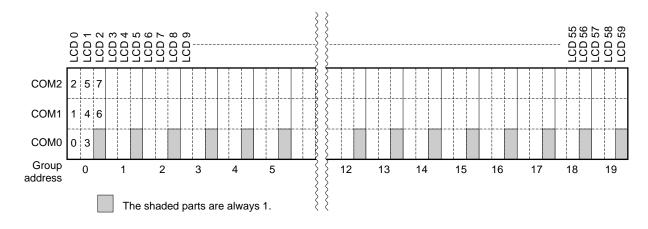

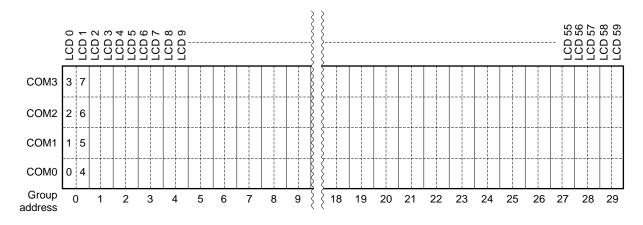

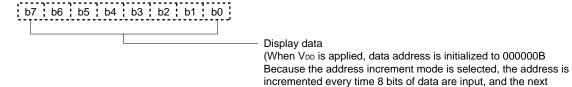

## **Display RAM Addresses and Display Dots**

Display RAM temporarily stores display data that has been sent serially.

Display RAM addresses are allocated in units of 8 bits (group address), and it is possible to store the display data of a group address transferred at one time.

The relations between group addresses and display dots for the three display modes are shown below.

## (1) 1/2 duty

## (2) 1/3 duty

# (3) 1/4 duty

**Remark** During auto incrementing, incrementing past the last group address of each duty (for example group address 14 in the case of 1/2 duty) brings the counter back to "0."

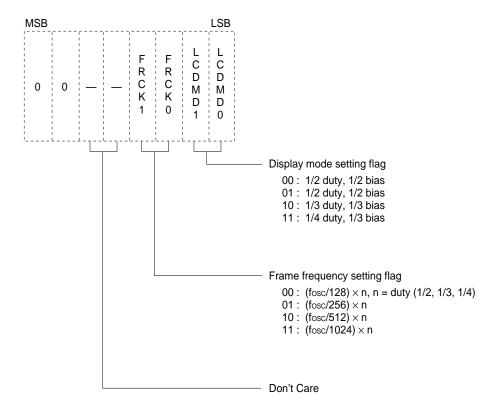

#### **Commands**

Commands serve to set the LCD driver's display mode and status.

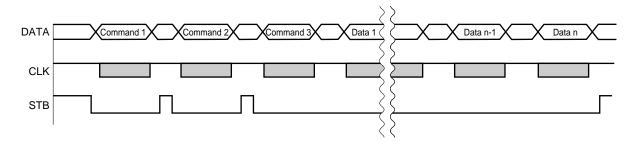

The first byte (8 bits) after the falling edge input of the STB signal is processed as a command.

The various types of commands are shown below.

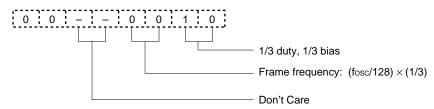

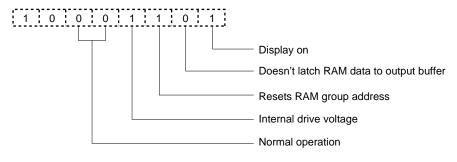

# (1) Display Mode Setting Command

| va | lues | at | рс    | W | er- | on | ır | es  | et |   |     |   |     |   |   |     |   |   |     |

|----|------|----|-------|---|-----|----|----|-----|----|---|-----|---|-----|---|---|-----|---|---|-----|

|    |      |    |       |   |     |    |    |     |    |   |     |   |     |   |   |     |   |   | ٦,  |

| 1  | 1    |    | 1 -   | _ | - 1 | _  | _  | 1   | _  | - |     | _ | - 1 | - | _ | - 1 | _ | _ | - 1 |

| 1  | L _  |    | . L . |   | 111 |    | _  | _1_ |    |   | L . |   |     |   |   | L   |   |   | _ 1 |

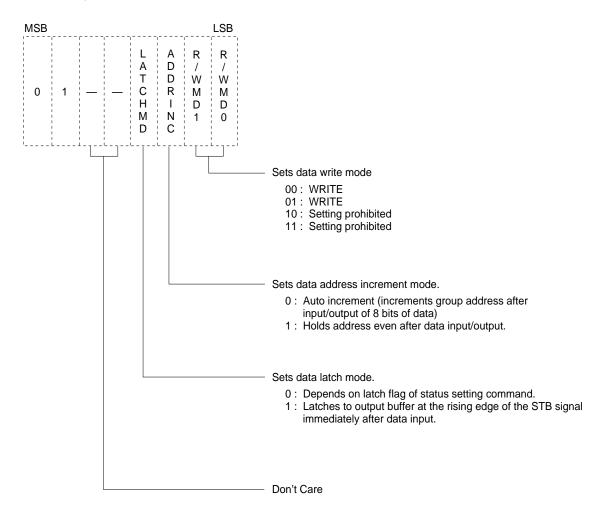

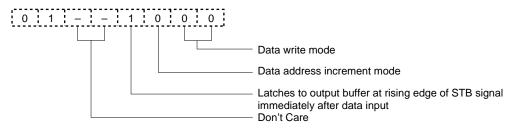

# (2) Data Setting Command

| Va | alues a | it powe | er-on res | set |     |   |     |

|----|---------|---------|-----------|-----|-----|---|-----|

| 1  | ,       | ,       |           |     |     |   | ,   |

| 1  | 1       | · —     | i — i     | 0 ' | 0 ' | Λ | · 0 |

| 1  | 1       | 1       |           |     |     | • | , 0 |

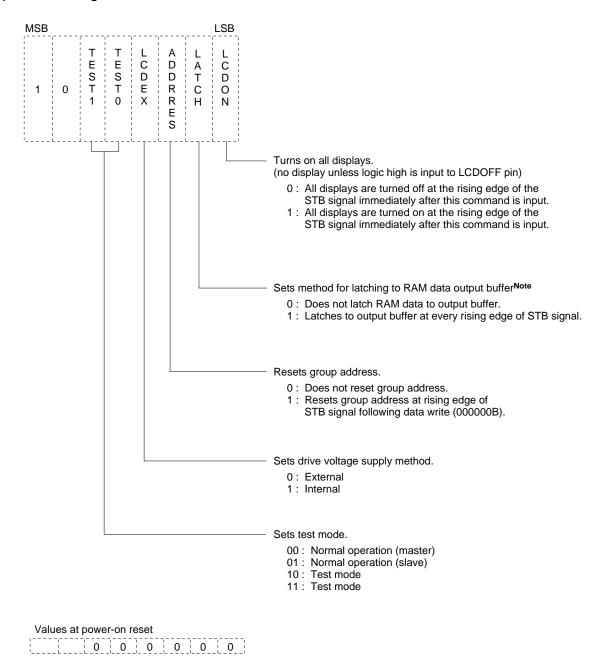

## (3) Status setting command

Remark LATCH MD flag and LATCH flag

The relations between the LATCH MD flag and the LATCH flag are shown below.

| Mode | LATCH MD | LATCH | Operation                                                                           |

|------|----------|-------|-------------------------------------------------------------------------------------|

| 1    | 0        | 0     | Does not latch RAM data to output buffer.                                           |

| 2    | 0        | 1     | Latches every time to output buffer at rising edge of STB signal.                   |

| 3    | 1        | 0     | Latches to output buffer at rising edge of STB signal immediately after data input. |

| 4    | 1        | 1     | Latches every time to output buffer at rising edge of STB signal.                   |

In modes 2 and 4, since latching to the output buffer is executed at the rising edge of the STB signal when only a command has been issued from the STB pin, busy status comes at each rising edge of the STB signal.

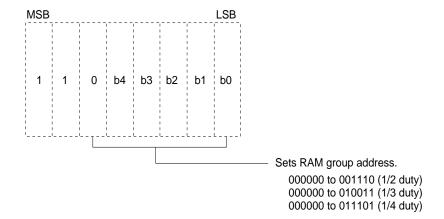

# (4) Address setting command

| Values at power-on reset |  |

|--------------------------|--|

| 000000                   |  |

DATA

CLK

STB

BUSY

Data

<10>

<4>

<9>

<4>

Command

- <1> Start serial communications by setting STB signal to logic low

- <2> Internal processing time = 300 ns

<1><2>

<3> Transmit mode setting command if initialized (duty cycle and others)

<8>

Command

- <4> Internal processing time = 300 ns

- <5> Wait for command data input after input of STB signal

- <6> Input data write method or address setting command

- <7> Transmit (receive) RAM data specified by set address

- <8> Transmit (receive) RAM data specified by set address

- <9> Input data write method or address setting command

- <10> Execute RAM data latch or display enable by rising STB pin.

- <11> Output logic low from BUSY pin during data latching. The time is 504.5/fosc.

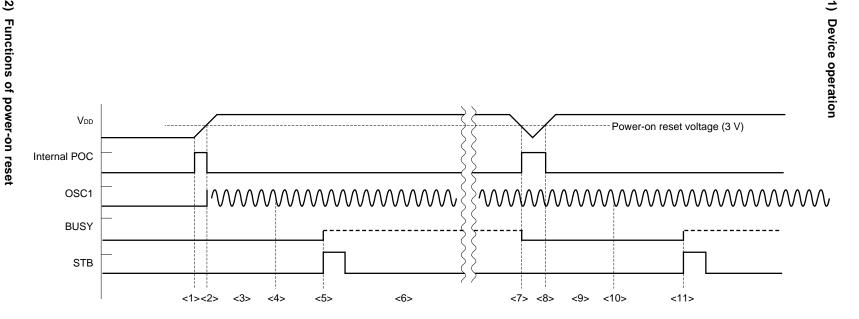

μ**PD16430A**

- <1> Apply supply voltage VDD.

- <2> When VDD becomes higher than power-on reset voltage, device starts operating.

- <3> Device stabilization time (less than 10 ms for internal oscillator) During this time, do not execute STB pin input.

- <4> After oscillation stabilization time is over, an STB signal input is waited for.

- When a logic high or logic low STB signal is input, a logic high is output from the BUSY pin, and a command input is waited for.

- A command input is waited for.

- <7> When VDD becomes again a value lower than the power-on reset voltage, device operation stops.

- When VDD becomes again a value higher than the power-on reset voltage, device operation starts.

- <9> Oscillation stabilization time (less than 10 ms for internal oscillator).

- <10> After oscillation stabilization time is over, an STB signal input is waited for.

- <11> When a logic high or logic low STB signal is input, a logic high is output from the BUSY pin, and a command input is waited for.

- <12> A command input is waited for.

## **Application**

## Data transmission examples according to address increment mode

## Command 1

#### Command 2

#### Command 3

#### Data 1 to n

data input is waited for.)

# Absolute Maximum Ratings ( $T_a = 25$ °C, GND = 0 V)

| Parameter                             | Symbol           | Condition | Rating                       | Unit |

|---------------------------------------|------------------|-----------|------------------------------|------|

| Logic supply voltage                  | V <sub>DD</sub>  |           | -0.3 to +7.0                 | ٧    |

| Logic input voltage                   | Vıı              |           | -0.3 to V <sub>DD</sub> +0.3 | ٧    |

| Logic output voltage                  | V <sub>O1</sub>  |           | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Driver supply voltage                 | VLCD             |           | -0.3 to +16                  | V    |

| Driver input voltage                  | VLC0 - VLC2      |           | -0.3 to VLCD + 0.3           | V    |

| Driver output voltage                 | V <sub>O2</sub>  |           | -0.3 to VLCD + 0.3           | ٧    |

| Operating temperature range           | Topt             |           | -40 to +85                   | °C   |

| Storage temperature range             | T <sub>stg</sub> |           | -65 to +150                  | °C   |

| Permissible package power dissipation | Pd               |           | 1000                         | mW   |

# Recommended Operating Conditions ( $T_a = -40$ to +85 °C, GND = 0 V)

| Parameter             | Symbol          | Condition | MIN.     | TYP. | MAX. | Unit |

|-----------------------|-----------------|-----------|----------|------|------|------|

| Logic supply voltage  | V <sub>DD</sub> |           | 3.5      |      | 6.0  | ٧    |

| Driver supply voltage | VLCD            |           | $V_{DD}$ |      | 14   | V    |

| Driver input voltage  | VLC0 - VLC2     |           | 0        |      | VLCD | V    |

# Electrical Characteristics ( $T_a = -40$ to +85 °C, $V_{DD} = 5$ V $\pm 10$ %, $V_{LCD} = 9$ to 12 V)

| Parameter                    | Symbol | Condition                                                        | MIN.                | TYP. | MAX.                | Unit |

|------------------------------|--------|------------------------------------------------------------------|---------------------|------|---------------------|------|

| Input voltage, high          | ViH    |                                                                  | 0.7·V <sub>DD</sub> |      | V <sub>DD</sub>     | V    |

| Input voltage, low           | VIL    |                                                                  | 0                   |      | 0.3·V <sub>DD</sub> | V    |

| Output voltage, high         | Vон    | OSC <sub>OUT</sub> , SYNC, BUSY<br>IoH = -1 mA                   | 0.9·V <sub>DD</sub> |      |                     | V    |

| Output voltage, low          | Vol    | OSCOUT, SYNC, BUSY<br>IOL = 1 mA                                 |                     |      | 0.1·V <sub>DD</sub> | V    |

| Input leak current, high     | Іін    | VIN = VDD                                                        |                     |      | 10                  | μΑ   |

| Input leak current, low      | lı∟    | V <sub>IN</sub> = 0 V                                            | -10                 |      |                     | μΑ   |

| Output leak current, high    | Ісон   | SYNC, BUSY<br>Vo = VDD                                           |                     |      | 10                  | μΑ   |

| Output leak current, low     | ILOL   | SYNC, BUSY<br>Vo = 0 V                                           | -10                 |      |                     | μΑ   |

| Common output ON resistance  | Rсом   | COM0 - COM3, $V_{LCD} = 9 \text{ V}$<br>IIoI = 100 $\mu\text{A}$ |                     | 1.2  | 2.4                 | kΩ   |

| Segment output ON resistance | Rseg   | LCD0 - LCD59, VLCD = 9 V llol = 100 $\mu$ A                      |                     | 2.0  | 4.0                 | kΩ   |

| Logic current dissipation    | lod    | fosc = 140 kHz                                                   |                     | 100  | 500                 | μΑ   |

| Driver current dissipation   | ILCD   | VLCD = 12 V, without load                                        |                     | 500  | 1000                | μΑ   |

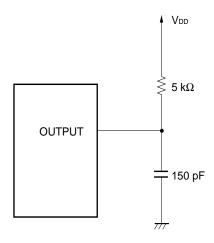

# Switching Characteristics (Ta = -40 to +85 $^{\circ}$ C, VdD = 5 V $\pm$ 10 %, VLCD = 9 to 12 V, RL = 5 k $\Omega$ , CL = 150 pF)

| Parameter             | Symbol | Condition                          | MIN. | TYP. | MAX. | Unit |

|-----------------------|--------|------------------------------------|------|------|------|------|

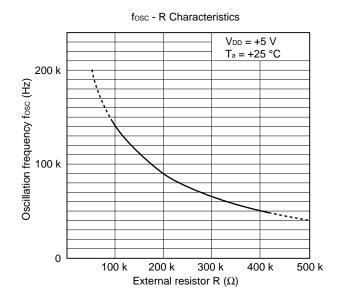

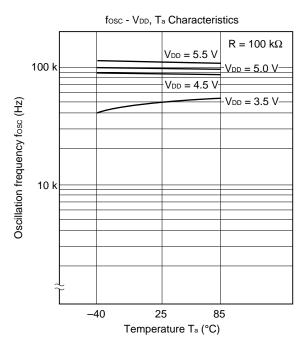

| Oscillation frequency | fsoc   | R = 100 kΩ                         | 98   | 140  | 182  | kHz  |

| BUSY delay time       | tobsy  | $STB \uparrow \to BUSY \downarrow$ |      |      | 1.5  | μs   |

| SYNC delay time       | tosync |                                    |      |      | 1.5  | μs   |

# Timing Requirements (Ta = -40 to +85 °C, VdD = 5 V $\pm$ 10 %, VLCD = 9 to 12 V, RL = 5 k $\Omega$ , CL = 150 pF)

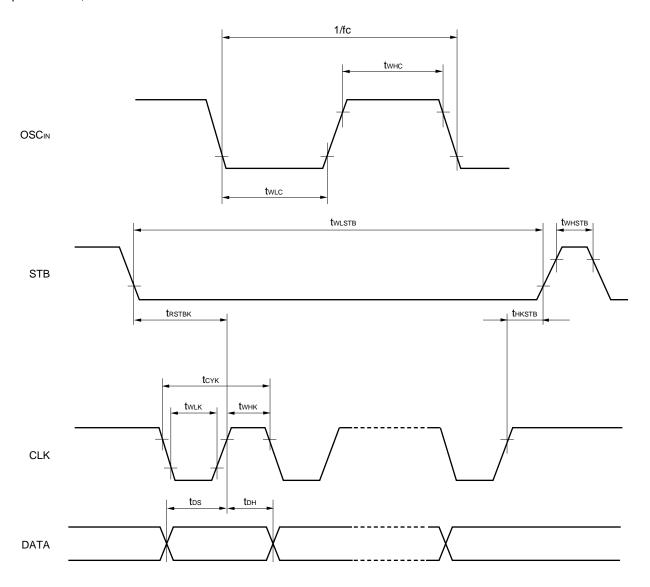

| Parameter                          | Symbol         | Condition                         | MIN. | TYP. | MAX. | Unit |

|------------------------------------|----------------|-----------------------------------|------|------|------|------|

| Clock frequency                    | fc             | OSC <sub>IN</sub> external clock  | 50   |      | 150  | kHz  |

| High-level clock pulse width       | twnc           | OSC <sub>IN</sub> external clock  | 3    |      | 16   | μs   |

| Low-level clock pulse width        | twLc           | OSC <sub>IN</sub> external clock  | 3    |      | 16   | μs   |

| Shift clock cycle                  | <b>t</b> cyk   | CLK                               | 900  |      |      | ns   |

| High-level shift clock pulse width | twнк           | CLK                               | 400  |      |      | ns   |

| Low-level shift clock pulse width  | twlk           | CLK                               | 400  |      |      | ns   |

| Data setup time                    | tos            |                                   | 100  |      |      | ns   |

| Data hold time                     | tон            |                                   | 200  |      |      | ns   |

| STB removal time                   | trsтвк         | $STB \downarrow \to CLK \uparrow$ | 300  |      |      | ns   |

| STB hold time                      | tнкsтв         | From the 8th CLK pulse            | 1    |      |      | μs   |

| High-level STB pulse width         | <b>t</b> wnstb |                                   | 1    |      |      | μs   |

| Low-level STB pulse width          | twlstb         |                                   | 8.2  |      |      | μs   |

| SYNC removal time                  | <b>t</b> srem  |                                   | 250  |      |      | ns   |

# **Output Load Circuit**

# **Switching Characteristic Waveform**

Measurement points: Input: 0.7 VDD, 0.3 VDD

Output: 0.8 VDD, 0.2 VDD

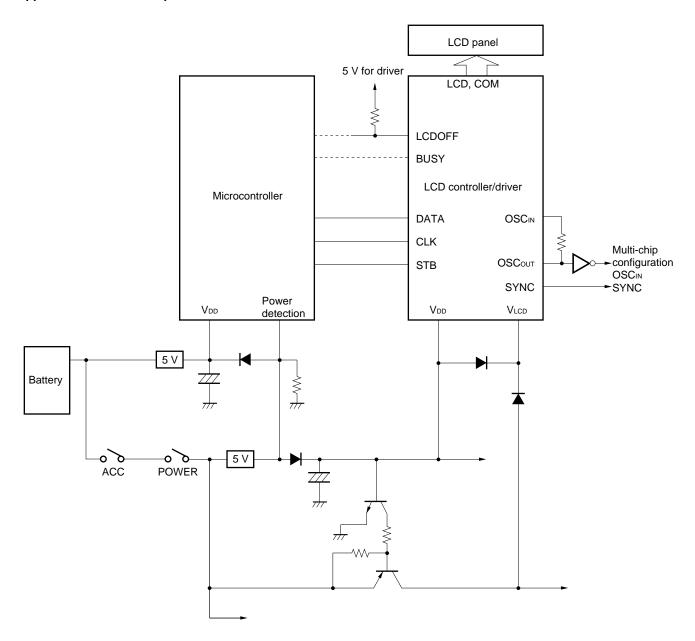

# **Application Circuit Example**

**Remark** Use low-V<sub>F</sub> diodes such as Schottky-barrier diodes, and make sure that V<sub>DD</sub>, V<sub>LCD</sub>, V<sub>I</sub>, etc. do not exceed absolute maximum ratings of the diodes.

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

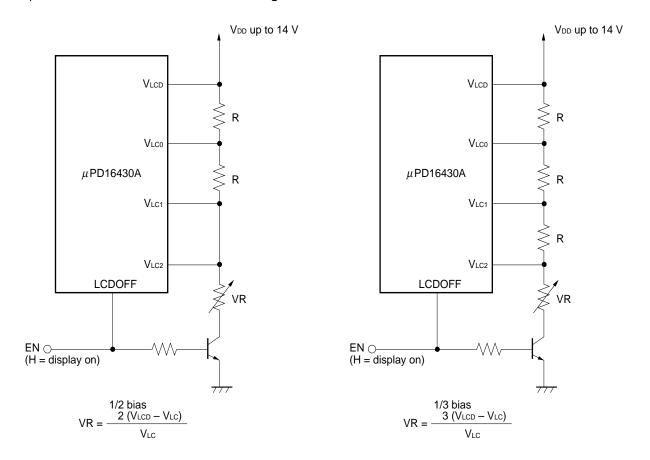

## 1. $\mu$ PD16430A External Bias Resistor Setting Method

VLC is the peak value of the optimum drive voltage for LCD. (it varies depending on the LCD.)

R is a resistance of 1 k $\Omega$  to 10 k $\Omega$ . Select the resistance value according to the load.

A larger value for R reduces the power dissipation, but causes drive waveform distortions.

Select a largish value for a variable resistor so as to satisfy the equation above.

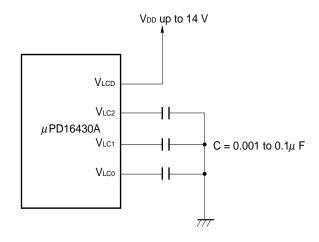

# 2. When using internal bias

A heavy LCD load may cause distortions in the common waveform. In this case, insert a capacitor for  $V_{LC0}$ ,  $V_{LC1}$  and  $V_{LC2}$ .

#### **Characteristic Curves**

## **Recommended Soldering Conditions**

When soldering on this product, please observe the recommended conditions indicated in the table below. If planning to solder under different conditions, please consult an NEC sales representative.

μPD16430AGF-3B9

| Soldering method    | Soldering conditions                                                                                                            | Symbol    |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------|

| Infrared ray reflow | Peak package temperature: 235 °C, time: 30 seconds max. (210 °C min.), number of reflow processes: 2, exposure limit: none Note | IR35-00-2 |

| VPS                 | Peak package temperature: 215 °C, time: 40 seconds max. (200 °C min.), number of reflow processes: 2, exposure limit: none Note | VP15-00-2 |

| Wave soldering      | Solder temperature: 260 °C max., time: 10 seconds max. number of reflow processes: 1, exposure limit: none Note                 | WS60-00-1 |

| Partial heating     | Pin temperature: 300 °C max., time: 10 seconds max., exposure limit: none Note                                                  | 0         |

**Note** Exposure limit before soldering after dry-package is opened. Storage conditions: 25 °C, relative humidity of 65 % or less.

Caution Do not apply two or more soldering methods (except partial heating) in combination.

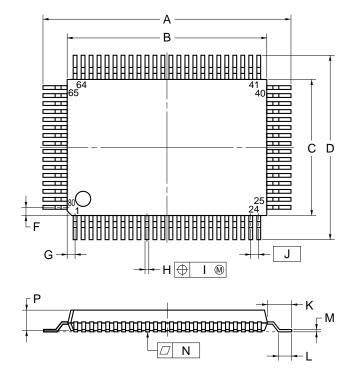

# 80 PIN PLASTIC QFP (14×20)

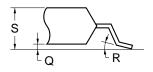

detail of lead end

## NOTE

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                    |  |  |

|------|------------------------|---------------------------|--|--|

| А    | 23.2±0.2               | 0.913+0.009               |  |  |

| В    | 20.0±0.2               | $0.787^{+0.009}_{-0.008}$ |  |  |

| С    | 14.0±0.2               | $0.551^{+0.009}_{-0.008}$ |  |  |

| D    | 17.2±0.2               | 0.677±0.008               |  |  |

| F    | 1.0                    | 0.039                     |  |  |

| G    | 1.8                    | 0.031                     |  |  |

| Н    | 0.35±0.10              | 0.014+0.004               |  |  |

| ı    | 0.15                   | 0.006                     |  |  |

| J    | 0.8 (T.P.)             | 0.031 (T.P.)              |  |  |

| K    | 1.6±0.2                | 0.063±0.008               |  |  |

| L    | 0.8±0.2                | $0.031^{+0.009}_{-0.008}$ |  |  |

| М    | $0.15^{+0.10}_{-0.05}$ | $0.006^{+0.004}_{-0.003}$ |  |  |

| N    | 0.10                   | 0.004                     |  |  |

| Р    | 2.7                    | 0.106                     |  |  |

| Q    | 0.125±0.075            | 0.005±0.003               |  |  |

| R    | 5°±5°                  | 5°±5°                     |  |  |

| S    | 3.0 MAX.               | 0.119 MAX.                |  |  |

S80GF-80-3B9-3

[MEMO]

NEC

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5