# MOS INTEGRATED CIRCUIT $\mu$ PD17P149

# SMALL, GENERAL-PURPOSE 4 BIT SINGLE-CHIP MICROCONTROLLER

The  $\mu$ PD17P149 is a one-time PROM version of the  $\mu$ PD17149. It uses a one-time PROM, which can be written just once, instead of internal masked ROM of the  $\mu$ PD17149.

Since a user program can be written into the PROM, this microcontroller is suited for program evaluation and low-volume production of the  $\mu$ PD17145,  $\mu$ PD17147,  $\mu$ PD17149, or for program evaluation of the  $\mu$ PD17145(A),  $\mu$ PD17147(A),  $\mu$ PD17149(A),  $\mu$ PD17145(A1),  $\mu$ PD17147(A1), and  $\mu$ PD17149(A1).

The following user's manual completely describes the functions of the  $\mu$ PD17P149. Be sure to read it before designing an application system.

μPD17145 Sub-Series User's Manual: U10261E

#### FEATURES

- 17K architecture : General registers, 16-bit instructions

- Pin compatible with the  $\mu$ PD17149 (except for PROM programming function)

- Internal one-time PROM : 8K bytes (4096 × 16 bits)

- Supply voltage : V<sub>DD</sub> = 2.7 to 5.5 V (when operating at the range between 400 kHz and 2 MHz with ceramic oscillation)

$V_{DD}$  = 4.5 to 5.5 V (when operating at the range between 400 kHz and 8 MHz with ceramic oscillation)

#### **ORDERING INFORMATION**

| Part number      | Package                             |

|------------------|-------------------------------------|

| μPD17P149CT      | 28-pin plastic shrink DIP (400 mil) |

| $\mu$ PD17P149GT | 28-pin plastic SOP (375 mil)        |

In the program memory write/verify mode, the voltage used for programming is applied to pin No. 23,  $POF_0/\overline{RLS}/V_{PP}$ . If a voltage of VDD plus 0.3 V or more is applied to this pin in the normal operation mode, the microcontroller may crash. Design the circuit so that a voltage of this magnitude is never applied to the pin.

The information in this document is subject to change without notice.

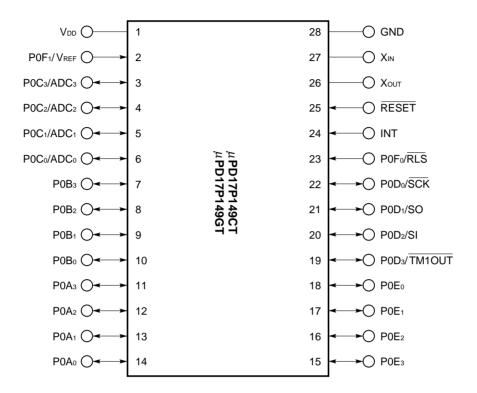

# **PIN CONFIGURATION (TOP VIEW)**

# (1) Normal operation mode

| ADC <sub>0</sub> - ADC <sub>3</sub> | : | Analog input             | RESET     | : | Reset input                             |

|-------------------------------------|---|--------------------------|-----------|---|-----------------------------------------|

| GND                                 | : | Ground                   | RLS       | : | Standby release signal input            |

| INT                                 | : | External interrupt input | SCK       | : | Serial clock input/output               |

| P0A0 - P0A3                         | : | Port 0A                  | SI        | : | Serial data input                       |

| P0B0 - P0B3                         | : | Port 0B                  | SO        | : | Serial data output                      |

| P0C <sub>0</sub> - P0C <sub>3</sub> | : | Port 0C                  | TM1OUT    | : | Timer 1 carry output                    |

| P0D0 - P0D3                         | : | Port 0D                  | Vdd       | : | Power supply                            |

| P0E0 - P0E3                         | : | Port 0E                  | Vref      | : | Reference voltage for the A/D converter |

| P0F0 and P0F1                       | : | Port 0F                  | Xin, Xout | : | System clock oscillation                |

|                                     |   |                          |           |   |                                         |

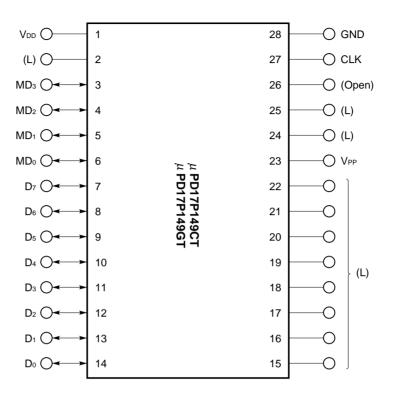

#### (2) Program memory write/verify mode

| CLK : Input clock for address update | MDo - MDa | : Operating mode selection |

|--------------------------------------|-----------|----------------------------|

| Do-D7 : Data                         | Vdd       | : Power supply             |

| GND : Ground                         | Vpp       | : Programming power supply |

Caution Symbols in parentheses denote processing for pins not used in the program memory write/verify mode.

L : Connect these pins separately to the GND pin through pull-down resistors.

Open : Nothing should be connected on these pins.

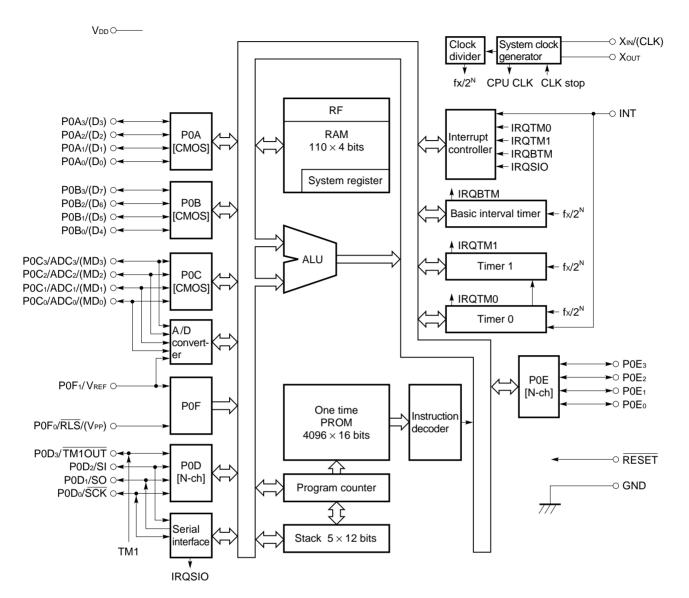

# **BLOCK DIAGRAM**

**Remark** () : PROM programming mode The terms CMOS and N-ch in brackets indicate the output form of the port.

CMOS : CMOS push-pull output

N-ch : N-channel open-drain output

# CONTENTS

| 1. | PIN F     | UNCTIONS                                                             | 6  |

|----|-----------|----------------------------------------------------------------------|----|

|    | 1.1       | NORMAL OPERATION MODE                                                |    |

|    | 1.2       | PROGRAM MEMORY WRITE/VERIFY MODE                                     | 8  |

|    | 1.3       | EQUIVALENT INPUT/OUTPUT CIRCUITS                                     | 9  |

|    | 1.4       | HANDLING UNUSED PINS                                                 | 13 |

|    | 1.5       | NOTES ON USE OF THE RESET AND P0F0/RLS PINS (ONLY AT THE NORMAL      |    |

|    |           | OPERATION MODE)                                                      | 14 |

| 2. | DIFF      | ERENCES BETWEEN THE $\mu$ PD17145, $\mu$ PD17147, $\mu$ PD17149, AND |    |

|    | $\mu$ PD1 | 7P149                                                                | 15 |

| 3. | WRIT      | ING TO AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY)                  | 16 |

|    | 3.1       | PROGRAM MEMORY WRITE/VERIFY MODES                                    | 16 |

|    | 3.2       | WRITING TO PROGRAM MEMORY                                            | 17 |

|    | 3.3       | READING PROGRAM MEMORY                                               | 18 |

| 4. | ELEC      | TRICAL CHARACTERISTICS                                               | 19 |

| 5. | PAC       | AGE DRAWINGS                                                         | 27 |

| 6. | RECO      | OMMENDED SOLDERING CONDITIONS                                        | 29 |

| AP | PENDI     | X A. $\mu$ PD17145 SUB-SERIES PRODUCTS LIST                          | 30 |

| AP | PENDI     | X B. DEVELOPMENT TOOLS                                               | 31 |

# 1. PIN FUNCTIONS

#### 1.1 NORMAL OPERATION MODE

| Pin No.              | Symbol                       | Function                                                                                                                                                                                                                                                                                                                                            | Output          | Upon reset      |

|----------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|

| 1                    | Vdd                          | Power supply                                                                                                                                                                                                                                                                                                                                        | -               | -               |

| 2                    | P0F1/VREF                    | <ul> <li>Port 0F. The reference voltage is supplied to the A/D converter through this pin.</li> <li>P0F1</li> <li>Bit 1 of 2-bit input port P0F</li> <li>V<sub>REF</sub></li> <li>Reference voltage input for the A/D converter</li> </ul>                                                                                                          | Input           | Input<br>(P0F1) |

| 3 - 6                | P0C3/ADC3 -<br>P0C0/ADC0     | <ul> <li>Port 0C. Analog voltage is supplied to the A/D converter through these pins.</li> <li>POC<sub>3</sub> - POC<sub>0</sub> <ul> <li>4-bit input/output port</li> <li>Input/output setting allowed in units of 1 bit</li> </ul> </li> <li>ADC<sub>3</sub> - ADC<sub>0</sub> <ul> <li>Analog input for the A/D converter</li> </ul> </li> </ul> | CMOS push-pull  | Input<br>(P0C)  |

| 7<br>8<br>9<br>10    | P0B3<br>P0B2<br>P0B1<br>P0B0 | <ul> <li>Port 0B</li> <li>4-bit input/output port</li> <li>Input/output setting allowed in units of 4 bits</li> <li>Pull-up resistor incorporation specifiable by program in units of 4 bits</li> </ul>                                                                                                                                             | CMOS push-pull  | Input           |

| 11<br>12<br>13<br>14 | P0A3<br>P0A2<br>P0A1<br>P0A0 | <ul> <li>Port 0A</li> <li>4-bit input/output port</li> <li>Input/output setting allowed in units of 4 bits</li> <li>Pull-up resistor incorporation specifiable by program in units of 4 bits</li> </ul>                                                                                                                                             | CMOS push-pull  | Input           |

| 15<br>16<br>17<br>18 | P0E3<br>P0E2<br>P0E1<br>P0E0 | <ul> <li>Port 0E</li> <li>Withstand voltage is V<sub>DD</sub> (Max.).</li> <li>4-bit input/output port</li> <li>Input/output setting allowed in units of 4 bits</li> <li>Pull-up resistor incorporation specifiable by program in units of 4 bits</li> </ul>                                                                                        | N-ch open drain | Input           |

| Pin No.  | Symbol                | Function                                                                                                                                                                                                                                                                                                                                                                                                         | Output          | Upon reset      |

|----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|

| 19       | P0D3/TM1OUT           | <ul> <li>Pin for port 0D, timer 1 output, serial data input, serial data output, and serial clock input/output</li> <li>Pull-up resistor incorporation specified by program bit by bit</li> <li>Withstand voltage is VDD (Max.).</li> <li>POD<sub>3</sub> - POD<sub>0</sub></li> <li>4-bit input/output port</li> <li>Input/output setting allowed bit by bit</li> <li>TM1OUT</li> <li>Timer 1 output</li> </ul> | N-ch open drain | Input<br>(P0D)  |

| 20       | P0D2/SI               | <ul><li>SI</li><li>Serial data input</li></ul>                                                                                                                                                                                                                                                                                                                                                                   |                 |                 |

| 21       | P0D1/SO               | <ul><li>SO</li><li>Serial data output</li></ul>                                                                                                                                                                                                                                                                                                                                                                  |                 |                 |

| 22       | P0D0/SCK              | SCK     Serial clock input/output                                                                                                                                                                                                                                                                                                                                                                                |                 |                 |

| 23       | P0F <sub>0</sub> /RLS | <ul> <li>Pin for port 0F and input for standby mode release signal</li> <li>P0F<sub>0</sub></li> <li>Bit 0 of 2-bit input port P0F</li> <li>RLS</li> <li>Input for standby mode release signal</li> </ul>                                                                                                                                                                                                        | Input           | Input<br>(P0F₀) |

| 24       | INT                   | Input for an external interrupt request signal and standby mode release signal.                                                                                                                                                                                                                                                                                                                                  | Input           | Input           |

| 25       | RESET                 | System reset input pin                                                                                                                                                                                                                                                                                                                                                                                           | Input           | Input           |

| 26<br>27 | Xout<br>Xin           | For system clock oscillation<br>The ceramic resonator is connected between X <sub>IN</sub> and<br>Xout.                                                                                                                                                                                                                                                                                                          | -               | _               |

| 28       | GND                   | Ground                                                                                                                                                                                                                                                                                                                                                                                                           | -               | -               |

# 1.2 PROGRAM MEMORY WRITE/VERIFY MODE

| Pin No.       | Pin name                                 | Function                                                                                                      | Input/output |

|---------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------|

| 1             | Vdd                                      | Power supply pin.<br>+6 V is applied to this pin when writing to program memory or verifying<br>its contents. | -            |

| 3<br>to<br>6  | MD <sub>3</sub><br>to<br>MD <sub>0</sub> | Input pins that select an operation mode when writing to program memory or verifying its contents             | Input        |

| 7<br>to<br>14 | D7<br>to<br>D0                           | Input/output pins for 8-bit data used when writing to program memory or verifying its contents                | Input/output |

| 23            | Vpp                                      | Voltage (+12.5 V) is applied to this pin when writing to program memory or verifying its contents.            | -            |

| 27            | CLK                                      | Input pin for address update clocks used when writing to program memory or verifying its contents             | Input        |

| 28            | GND                                      | Ground                                                                                                        | _            |

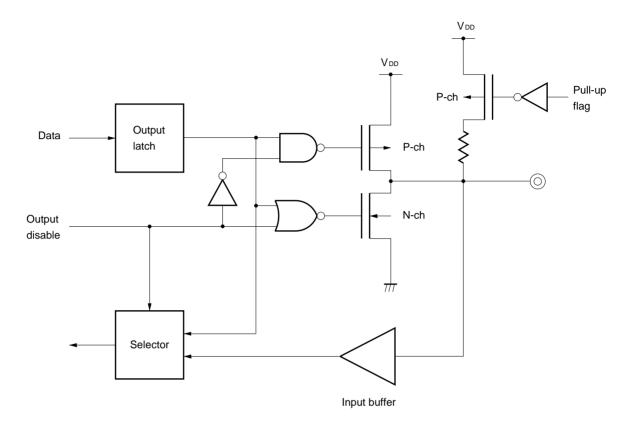

# **1.3 EQUIVALENT INPUT/OUTPUT CIRCUITS**

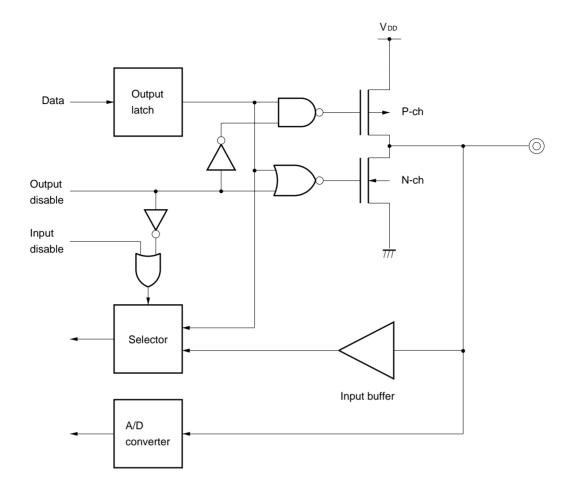

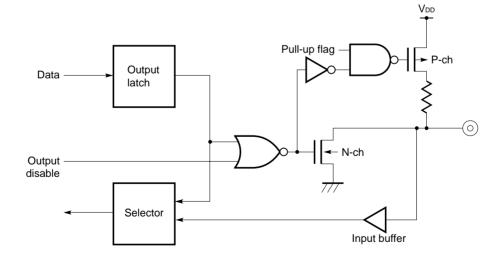

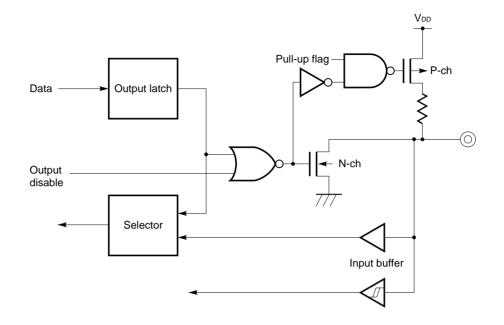

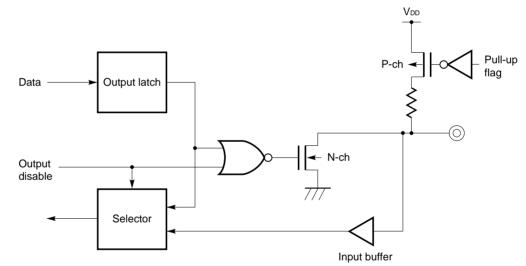

Below are simplified diagrams of the input/output circuits for each pin.

## (1) P0A<sub>0</sub> - P0A<sub>3</sub>, P0B<sub>0</sub> - P0B<sub>3</sub>

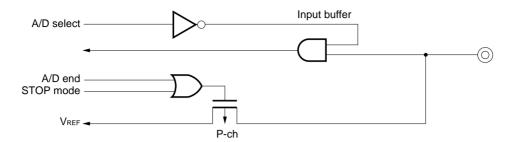

# (2) POC<sub>0</sub>/ADC<sub>0</sub> - POC<sub>3</sub>/ADC<sub>3</sub>

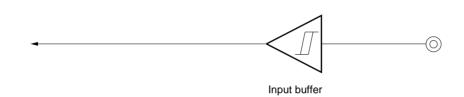

# (3) P0D<sub>3</sub>/TM1OUT, P0D<sub>1</sub>/SO

# (4) P0D<sub>2</sub>/SI, P0D<sub>0</sub>/SCK

(5) P0E<sub>0</sub> - P0E<sub>3</sub>

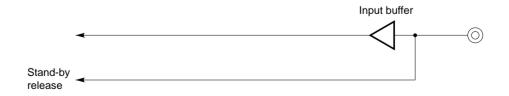

(6) P0Fo/RLS

# NEC

# (7) P0F1/VREF

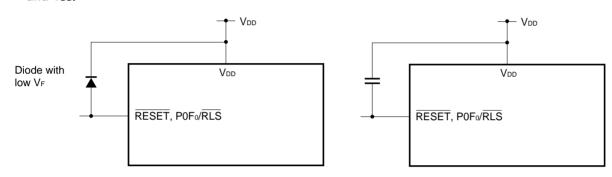

(8) RESET, INT

## 1.4 HANDLING UNUSED PINS

Connect unused pins at the normal operation mode as follows:

|     |                                                   | Pin                                                                         | Conditions                                                                           | and handling                       |

|-----|---------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------|

| Pin |                                                   |                                                                             | Internal                                                                             | External                           |

|     |                                                   | Pull-up resistors that can be specified with the software are incorporated. | Leave open.                                                                          |                                    |

|     |                                                   |                                                                             | Connect to V <sub>DD</sub> or ground through resistors for each pin.Note 1           |                                    |

|     |                                                   | P0F <sub>1</sub>                                                            | _                                                                                    | Connect directly to VDD or ground. |

|     |                                                   | P0F <sub>0</sub> Note 2                                                     | _                                                                                    | Connect directly to ground.        |

|     | Output<br>mode                                    | P0A, P0B, P0C<br>(CMOS ports)                                               | _                                                                                    | Leave open.                        |

|     | P0D (N-ch open-<br>drain port) Outputs low level. |                                                                             | Outputs low level.                                                                   |                                    |

|     |                                                   | P0E (N-ch open-<br>drain port)                                              | Outputs low level without pull-up resistors that can be specified with the software. |                                    |

|     |                                                   |                                                                             | Outputs low level with pull-up resistors that can be specified with the software.    |                                    |

| Ext | ernal inter                                       | rupt (INT)                                                                  | _                                                                                    | Connect directly to VDD or ground. |

Table 1-1 Handling Unused Pins

- **Notes 1.** When a pin is pulled up to V<sub>DD</sub> (connected to V<sub>DD</sub> through a resistor) or pulled down to ground (connected to ground through a resistor) outside the chip, take the driving capacity and maximum current consumption of a port into consideration. When using high-resistance pull-up or pull-down resistors, apply appropriate countermeasures to ensure that noise is not attracted by the resistors. Although the optimum pull-up or pull-down resistor varies with the application circuit, in general, a resistor of 10 to 100 kilohms is suitable.

- 2. Since the P0F<sub>0</sub>/RLS pin is also used as the V<sub>PP</sub> pin for writing and verifying the program memory, connect directly to ground when the pin is not used.

- Caution To fix the I/O mode, pull-up resistors that can be specified with the software, and output level of a pin, it is recommended that they should be specified repeatedly within a loop in a program.

# 1.5 NOTES ON USE OF THE RESET AND POF0/RLS PINS (ONLY AT THE NORMAL OPERATION MODE)

The RESET pin can be used as the test mode selection pin for testing the internal operation of the  $\mu$ PD17P149 (IC test), besides the usage shown in **Section 1.1**.

The P0F<sub>0</sub>/RLS pin can be used as the V<sub>PP</sub> pin in the program memory write/verify mode.

Applying a voltage exceeding V<sub>DD</sub> to the  $\overrightarrow{\text{RESET}}$  or P0F<sub>0</sub>/ $\overrightarrow{\text{RLS}}$  pin causes the  $\mu$ PD17P149 to enter the test mode or program memory write/verify mode. When noise exceeding V<sub>DD</sub> comes in during normal operation, the device may not operate normally.

For example, if the wiring from the RESET or P0F<sub>0</sub>/RLS pin is too long, noise may be induced on the wiring, causing this mode switching.

When installing the wiring, lay the wiring in such a way that noise is suppressed as much as possible. If noise yet arises, use an external part to suppress it as shown below.

- Connect a diode with low VF between the pin and VDD.

- Connect a capacitor between the pin and  $V_{\text{DD}}$ .

# 2. DIFFERENCES BETWEEN THE $\mu$ PD17145, $\mu$ PD17147, $\mu$ PD17149, AND $\mu$ PD17P149

The  $\mu$ PD17P149 is a one-time PROM version of the  $\mu$ PD17149, in which the internal mask ROM is replaced with a one-time PROM.

Table 2-1 lists the differences between the  $\mu$ PD17145,  $\mu$ PD17147,  $\mu$ PD17149, and  $\mu$ PD17P149.

The  $\mu$ PD17P149 has the same CPU functions and internal peripheral hardwares as those of  $\mu$ PD17145,  $\mu$ PD17147, and  $\mu$ PD17149 except for its program memory, program size, address register size, and mask option.

Part of electrical characteristics is also different between those products. For details of the electrical characteristics, refer to the data sheet of each product.

| Item                                                 | μPD17145                                                                                          | μPD17147                                                                                      | μPD17149                                                                                      | μPD17P149 |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|--|--|

| Program memory (ROM)                                 | Masked ROM                                                                                        | Masked ROM                                                                                    |                                                                                               |           |  |  |

|                                                      |                                                                                                   |                                                                                               |                                                                                               | -0FFFH)   |  |  |

| Program counter (PC)                                 | 10 bits                                                                                           | 11 bits                                                                                       | 12                                                                                            | bits      |  |  |

| Address register (AR)                                | _                                                                                                 |                                                                                               |                                                                                               |           |  |  |

| Address stack register                               | _                                                                                                 |                                                                                               |                                                                                               |           |  |  |

| Pull-up resistors of P0F,<br>RESET, and INT pins     | Mask option                                                                                       | Not provided                                                                                  |                                                                                               |           |  |  |

| Internal POC circuit                                 | Mask option                                                                                       |                                                                                               | Not provided                                                                                  |           |  |  |

| V <sub>PP</sub> pin and operating mode selection pin | Not provided                                                                                      |                                                                                               |                                                                                               | Provided  |  |  |

| Quality grade                                        | <ul> <li>Standard<br/>μPD17145</li> <li>Special<br/>μPD17145 (A)<br/>μPD17145 (A1)</li> </ul>     | <ul> <li>Standard<br/>μPD17147</li> <li>Special<br/>μPD17147 (A)<br/>μPD17147 (A1)</li> </ul> | <ul> <li>Standard<br/>μPD17149</li> <li>Special<br/>μPD17147 (A)<br/>μPD17147 (A1)</li> </ul> | Standard  |  |  |

| Electrical characteristics                           | Partially differs between these products.<br>Refer to the data sheet of each product for details. |                                                                                               |                                                                                               |           |  |  |

Table 2-1 Differences between the  $\mu$ PD17145,  $\mu$ PD17147,  $\mu$ PD17149, and  $\mu$ PD17P149

Caution Although a PROM product is highly compatible with a mask ROM product in respect of functions, they differ in internal ROM circuits and part of electrical characteristics. Before changing the PROM product to the mask ROM product in an application system, evaluate the system carefully using the mask ROM product.

# 3. WRITING TO AND VERIFYING ONE-TIME PROM (PROGRAM MEMORY)

The  $\mu$ PD17P149's internal program memory consists of a 4096  $\times$  16 bit one-time PROM.

Writing to the one-time PROM or verifying the contents of the PROM is accomplished using the pins shown in Table 3-1. Note that address inputs are not used; instead, the address is updated using the clock input from the CLK pin.

Caution The P0F<sub>0</sub>/RLS/V<sub>PP</sub> pin is used as the V<sub>PP</sub> pin when writing to program memory or verifying its contents. If an voltage equal to or more than V<sub>DD</sub> + 0.3 V is applied to the P0F<sub>0</sub>/RLS pin in normal operation mode, the microcontroller may cause a system crash. Protect the pins from high voltages.

#### Table 3-1 Pins Used When Writing to Program Memory or Verifying Its Contents

| Pin       | Function                                                                                                            |

|-----------|---------------------------------------------------------------------------------------------------------------------|

| Vpp       | Pin for applying programming supply voltage.<br>Voltage (+12.5 V) is applied to this pin.                           |

| Vdd       | Positive power supply pin.<br>+6 V is applied to this pin.                                                          |

| CLK       | Input pin for address update clocks.<br>Input of four pulses to this pin updates the address of the program memory. |

| MDo - MD3 | Input pins that select an operation mode                                                                            |

| D0 - D7   | Input/output pins for 8-bit data                                                                                    |

#### 3.1 PROGRAM MEMORY WRITE/VERIFY MODES

If +6 V is applied to the V<sub>DD</sub> pin and +12.5 V is applied to the V<sub>PP</sub> pin after a certain duration of reset status (V<sub>DD</sub> = 5 V,  $\overline{\text{RESET}}$  = 0 V), the  $\mu$ PD17P149 enters program memory write/verify mode. A specific operating mode is then selected by setting the MD<sub>0</sub> through MD<sub>3</sub> pins as follows. The X<sub>OUT</sub> pin must be left open. Connect each pin not listed in Table 3-1 (including the  $\overline{\text{RESET}}$  pin) to ground through a resistor.

| Table 3-2 | Specification o | of Operating | Modes |

|-----------|-----------------|--------------|-------|

|-----------|-----------------|--------------|-------|

|              | Operating mode specification |                 |     |                 | Operating mode |                                   |  |

|--------------|------------------------------|-----------------|-----|-----------------|----------------|-----------------------------------|--|

| Vpp          | Vdd                          | MD <sub>0</sub> | MD1 | MD <sub>2</sub> | MD3            |                                   |  |

|              |                              | Н               | L   | Н               | L              | Program memory address clear mode |  |

| +12.5 V      | +6 V                         | L               | Н   | Н               | Н              | Write mode                        |  |

| +12.3 V +0 V | 10 0                         | L               | L   | Н               | Н              | Verify mode                       |  |

|              |                              | Н               | ×   | Н               | Н              | Program inhibit mode              |  |

**Remark** ×: Don't care. L (low) or H (high)

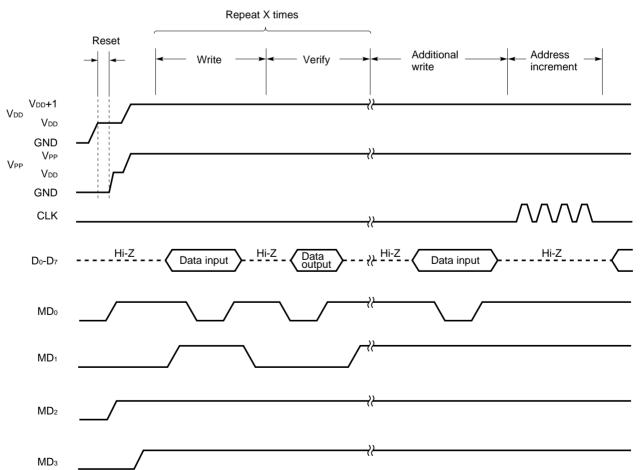

## 3.2 WRITING TO PROGRAM MEMORY

The procedure for writing to program memory is described below.

- (1) Connect all unused pins to GND through resistors (the Xou⊤ pin is left open). Apply a low-level signal to the CLK pin.

- (2) Apply 5 V to VDD and apply a low-level signal to the VPP pin.

- (3) Wait 10  $\mu$ s. Then apply 5 V to VPP.

- (4) Set the mode selection pins to program memory address clear mode.

- (5) Apply 6 V to VDD and 12.5 V to VPP.

- (6) Select program inhibit mode.

- (7) Write data in 1-ms write mode.

- (8) Select program inhibit mode.

- (9) Select verify mode. If the write operation is found successful, proceed to step (10). If the operation is found unsuccessful, repeat steps (7) to (9).

- (10) Perform additional write for X (number of repetitions of steps (7) to (9))  $\times$  1 ms.

- (11) Select program inhibit mode.

- (12) Increment the program memory address by one on reception of four pulses on the CLK pin.

- (13) Repeat steps (7) to (12) until the last address is reached.

- (14) Select program memory address clear mode.

- (15) Apply 5 V to the VDD and VPP pins.

- (16) Turn power off.

A timing chart for program memory writing steps (2) to (12) is shown in Fig. 3-1.

#### Fig. 3-1 Timing Chart for Program Memory Writing Steps

# NEC

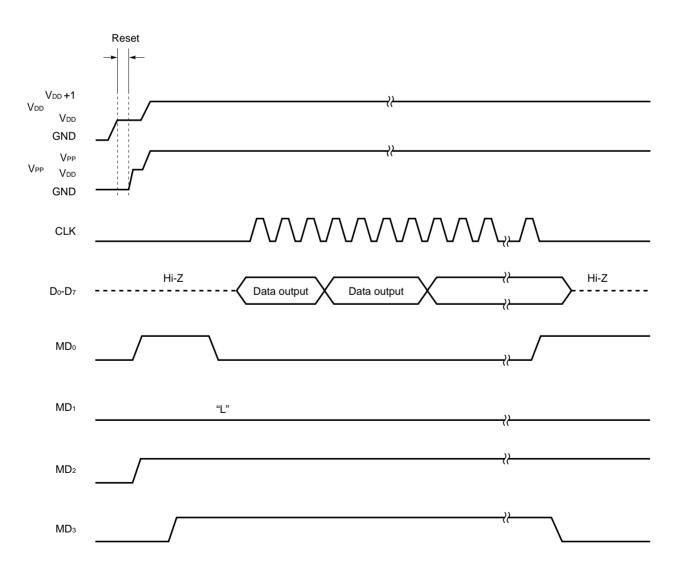

# 3.3 READING PROGRAM MEMORY

- (1) Connect all unused pins to GND through resistors (the Xout pin is left open). Apply a low-level signal to the CLK pin.

- (2) Apply 5 V to  $V_{\text{DD}}$  and apply a low-level signal to the  $V_{\text{PP}}$  pin.

- (3) Wait 10  $\mu s.$  Then apply 5 V to VPP.

- (4) Set the mode selection pins to program memory address clear mode.

- (5) Apply 6 V to V\_DD and 12.5 V to V\_PP.

- (6) Select program inhibit mode.

- (7) Select verify mode. Data is output sequentially one address at a time for every four input clock pulses on the CLK.

- (8) Select program inhibit mode.

- (9) Select program memory address clear mode.

- (10) Apply 5 V to the VDD and VPP pins.

- (11) Turn power off.

\*

A timing chart for program memory reading steps (2) to (9) is shown below.

# Fig. 3-2 Timing Chart for Program Memory Reading Steps

# 4. ELECTRICAL CHARACTERISTICS

#### ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)

| Parameter                       | Symbol             | Conditions                                        |                           | Rated value       | Unit                          |    |                               |   |

|---------------------------------|--------------------|---------------------------------------------------|---------------------------|-------------------|-------------------------------|----|-------------------------------|---|

| Supply voltage                  | Vdd                |                                                   |                           |                   | -0.3 to +7.0                  | V  |                               |   |

| PROM supply voltage             | Vpp                |                                                   |                           |                   | -0.3 to +13.5                 | V  |                               |   |

| A/D converter reference voltage | Vref               |                                                   |                           |                   | -0.3 to V <sub>DD</sub> + 0.3 | V  |                               |   |

| Input voltage                   | Vı                 | P0A, P0B, P0C, P0D, P0E, P0F, INT, RESET, and XIN |                           |                   |                               |    | -0.3 to V <sub>DD</sub> + 0.3 | V |

| Output voltage                  | Vo                 |                                                   |                           | -0.3 to Vpp + 0.3 | V                             |    |                               |   |

| High-level output current       | <sub>OH</sub> Note | Each of P0A, P0B,<br>and P0C pins                 |                           | Peak value        | -15                           | mA |                               |   |

|                                 |                    |                                                   |                           | rms               | -7.5                          | mA |                               |   |

|                                 |                    | Total of P0A, P0B,                                |                           | Peak value        | -30                           | mA |                               |   |

|                                 |                    | and P0C pins                                      |                           | rms               | -15                           | mA |                               |   |

| Low-level output current        | <sub>OL</sub> Note | Each of P0A, P0B,<br>and P0C                      |                           | Peak value        | 15                            | mA |                               |   |

|                                 |                    |                                                   |                           | rms               | 7.5                           | mA |                               |   |

|                                 |                    | Each of P0D and P0E                               |                           | Peak value        | 30                            | mA |                               |   |

|                                 |                    |                                                   |                           | rms               | 15                            | mA |                               |   |

|                                 |                    | Total of P0A, P0B,<br>P0C, P0D, and P0E pins      |                           | Peak value        | 100                           | mA |                               |   |

|                                 |                    |                                                   |                           | rms               | 50                            | mA |                               |   |

| Operating ambient temperature   | TA                 |                                                   |                           |                   | -40 to +85                    | °C |                               |   |

| Storage temperature             | Tstg               |                                                   |                           |                   | -65 to +150                   | °C |                               |   |

| Allowable dissipation           | Pd                 | TA = 85 °C                                        | 28-pin plastic shrink DIP |                   | 140                           | mW |                               |   |

|                                 |                    | 28-pin p                                          |                           | astic SOP         | 85                            | mW |                               |   |

**Note** Calculate a root-mean-square value as follows: [rms value] = [peak value]  $\times \sqrt{duty}$ .

Caution Absolute maximum ratings are rated values beyond which some physical damages may be caused to the product; if any of the parameters in the table above exceeds its rated value even for a moment, the quality of the product may deteriorate. Be sure to use the product within the rated values.

#### RECOMMENDED POWER VOLTAGE RANGE (TA = -40 to +85 °C)

| Parameter      | Symbol                                | Conditions       |                                                |     | Тур. | Max. | Unit |

|----------------|---------------------------------------|------------------|------------------------------------------------|-----|------|------|------|

| Supply voltage | Vdd                                   | CPU              | $f_x = 400 \text{ kHz to } 2 \text{ MHz}$      | 2.7 |      | 5.5  | V    |

|                | · · · · · · · · · · · · · · · · · · · | (except A/D con- | $f_x = 400 \text{ kHz to } 4 \text{ MHz}$      | 3.6 |      | 5.5  | V    |

|                |                                       | verter)          | fx = 400  kHz to  8  MHz                       | 4.5 |      | 5.5  | V    |

|                |                                       | A/D converter    | Absolute accuracy: ±1.5 LSB,                   | 4.0 |      | 5.5  | V    |

|                |                                       |                  | $2.5~V \leq V_{\text{REF}} \leq V_{\text{DD}}$ |     |      |      |      |

## **DC CHARACTERISTICS** (VDD = 2.7 to 5.5 V, T<sub>A</sub> = -40 to +85 °C)

| Parameter                            | Symbol | Conditions                                                    |                                                                       |                                              | Min.      | Тур. | Max. | Unit |

|--------------------------------------|--------|---------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------|-----------|------|------|------|

| High-level input                     | VIH1   | P0A, P0B, P0C, P0D, P0E, and P0F                              |                                                                       |                                              | 0.7Vdd    |      | Vdd  | V    |

| voltage                              | VIH2   | RESET, SCK, S                                                 | 0.8Vdd                                                                |                                              | Vdd       | V    |      |      |

|                                      | Vінз   | Xin                                                           | Vdd - 0.5                                                             |                                              | Vdd       | V    |      |      |

| Low-level input<br>voltage           | VIL1   | P0A, P0B, P0C                                                 | 0                                                                     |                                              | 0.3Vdd    | V    |      |      |

|                                      | VIL2   | RESET, SCK, S                                                 | 0                                                                     |                                              | 0.2VDD    | V    |      |      |

|                                      | VIL3   | Xin                                                           | 0                                                                     |                                              | 0.4       | V    |      |      |

| High-level output<br>voltage         | Vон    | Voн P0A, P0B, and P0C                                         |                                                                       | 4.5 - V <sub>DD</sub> - 5.5<br>Іон = -1.0 mA | Vdd - 0.3 |      |      | V    |

|                                      |        |                                                               |                                                                       | 2.7 - V <sub>DD</sub> < 4.5<br>Іон = -0.5 mA | Vdd - 0.3 |      |      | V    |

| Low-level output<br>voltage          | Vol1   | P0A, P0B, P0C, P0D, and P0E                                   |                                                                       | 4.5 - V <sub>DD</sub> - 5.5<br>Iol = 1.0 mA  |           |      | 0.3  | V    |

|                                      |        |                                                               |                                                                       | 2.7 - V <sub>DD</sub> < 4.5<br>Io∟ = 0.5 mA  |           |      | 0.3  | V    |

|                                      | Vol2   |                                                               |                                                                       | 4.5 - VDD - 5.5                              |           |      | 1.0  | V    |

|                                      |        |                                                               |                                                                       | 2.7 - V <sub>DD</sub> < 4.5                  |           |      | 2.0  | V    |

| High-level input<br>leakage current  | Цин    | P0A, P0B, P0C,                                                |                                                                       |                                              | 3         | μΑ   |      |      |

| Low-level input<br>leakage current   | Lu     | P0A, P0B, P0C, P0D, P0E, P0F, RESET, and INT $V_{IN} = 0 V$   |                                                                       |                                              |           |      | -3   | μΑ   |

| High-level output<br>leakage current | Ігон   | P0A, P0B, P0C, P0D, and P0E Vout = VDD                        |                                                                       |                                              |           |      | 3    | μΑ   |

| Low-level output leakage current     | ILOL   | P0A, P0B, P0C, P0D, and P0E Vout = 0 V                        |                                                                       |                                              |           |      | -3   | μΑ   |

| Built-in pull-up<br>resistanceNote 1 | Rpull  | P0A, P0B, and P0E                                             |                                                                       |                                              | 50        | 100  | 200  | kΩ   |

|                                      |        | P0D                                                           |                                                                       |                                              | 3         | 10   | 30   | kΩ   |

| Power supply                         |        | Normal $f_x = 8.0 \text{ MHz}, V_{DD} = 5 \text{ V} \pm 10\%$ |                                                                       |                                              |           | 5.5  | 8.0  | mA   |

| currentNote 2                        |        |                                                               | fx = 4.0 MHz, VDD = 5 V ±10%                                          |                                              |           | 3.3  | 5.5  | mA   |

|                                      |        |                                                               | $fx = 2.0 \text{ MHz}, \text{ V}_{DD} = 3 \text{ V} \pm 10\%$         |                                              |           | 1.0  | 2.5  | mA   |

|                                      |        |                                                               | fx = 400 kHz                                                          | $V_{DD} = 5 V \pm 10\%$                      |           | 2.0  | 4.7  | mA   |

|                                      |        |                                                               |                                                                       | $V_{DD} = 3 V \pm 10\%$                      |           | 0.7  | 2.4  | mA   |

|                                      | IDD2   | IDD2 HALT mode                                                | $fx = 8.0 \text{ MHz}, \text{ V}_{\text{DD}} = 5 \text{ V} \pm 10\%$  |                                              |           | 3.5  | 5.0  | mA   |

|                                      |        | $f_x = 4.0 \text{ MHz}, V_{DD} = 5 \text{ V} \pm 10\%$        |                                                                       |                                              | 2.7       | 4.1  | mA   |      |

|                                      |        |                                                               | $f_x = 2.0 \text{ MHz}, \text{ V}_{\text{DD}} = 3 \text{ V} \pm 10\%$ |                                              |           | 0.8  | 2.0  | mA   |

|                                      |        |                                                               |                                                                       |                                              |           | 1.8  | 3.8  | mA   |

|                                      |        |                                                               |                                                                       |                                              |           | 0.6  | 2.2  | mA   |

|                                      | IDD3   | STOP mode                                                     |                                                                       |                                              |           | 12   | 50   | μΑ   |

|                                      |        |                                                               |                                                                       |                                              |           | 10   | 45   | μA   |

Notes 1. Pull-up resistors are not incorporated for the P0F, RESET, and INT pins.

2. This current excludes the current which flows through the A/D converter and built-in pull-up resistors.