# PRELIMINARY DATA SHEET

# MOS INTEGRATED CIRCUIT $\mu PD30550$

# V<sub>R</sub>5500<sup>™</sup>

#### 64-/32-BIT MICROPROCESSOR

#### **DESCRIPTION**

The  $\mu$ PD30550 (V<sub>R</sub>5500) is a member of the V<sub>R</sub> Series<sup>TM</sup> of RISC (Reduced Instruction Set Computer) microprocessors. It is a high-performance 64-/32-bit microprocessor that employs the RISC architecture developed by MIPS<sup>TM</sup>.

The  $V_R5500$  allows selection of a 64-bit or 32-bit bus width for the system interface, and can operate using protocols compatible with the  $V_R5000$  Series<sup>TM</sup> and  $V_R5432^{TM}$ .

Detailed function descriptions are provided in the following user's manual. Be sure to read the manual before designing.

VR5500 User's Manual (U16044E)

#### **FEATURES**

- MIPS 64-bit RISC architecture

- · High-speed operation processing

- Two-way superscalar super pipeline

- 300 MHz product: 603 MIPS

400 MHz product: 804 MIPS

- High-speed translation lookaside buffer (TLB) (48 entries)

- · Address space

- Physical: 36 bits (64-bit bus selected)

- 32 bits (32-bit bus selected)

- Virtual: 40 bits (in 64-bit mode)

- 31 bits (in 32-bit mode)

- On-chip floating-point unit (FPU)

- Supports sum-of-products instructions

- On-chip primary cache memory (instruction/data: 32 KB each)

- 2-way set associative

- · Supports line lock feature

- 64-/32-bit address/data multiplexed bus

- Bus width selectable during reset

- Bus protocol compatibility with existing products retained

- Maximum operating frequency

- 300 MHz product: Internal 300 MHz, external 133 MHz

- 400 MHz product: Internal 400 MHz, external 133 MHz

- External/internal multiplication factor selectable from ×2 to ×5.5 by increments of 0.5

- Conforms to MIPS I, II, III, and IV instruction sets. Also supports product-sum operation instruction, rotate instruction, register scan instruction, and instruction for low power mode.

- Supports hardware debug function (N-Wire)

- Supply voltage

Core block: 1.5 V ±5% (300 MHz product)

1.6 to 1.7 V (400 MHz product)

I/O block: 3.3 V  $\pm$ 5%, 2.5 V  $\pm$ 5%

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

#### **APPLICATIONS**

- Set-top boxes

- RAID

- High-end embedded devices, etc.

#### **ORDERING INFORMATION**

| Part Number             | Package                                                  | Maximum Operating Frequency (MHz) |

|-------------------------|----------------------------------------------------------|-----------------------------------|

| $\mu$ PD30550F2-300-NN1 | 272-pin plastic BGA (C/D advanced type) (29 $\times$ 29) | 300                               |

| $\mu$ PD30550F2-400-NN1 | 272-pin plastic BGA (C/D advanced type) (29 $\times$ 29) | 400                               |

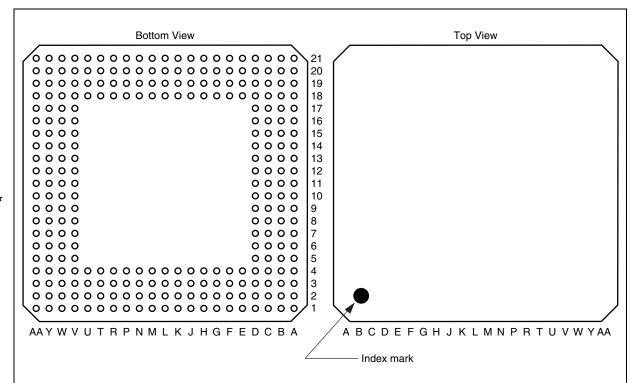

#### PIN CONFIGURATION

• 272-pin plastic BGA (C/D advanced type) (29  $\times$  29)  $\mu$ PD30550F2-300-NN1  $\mu$ PD30550F2-400-NN1

\*

(1/2)

| No. | Pin Name           | No. | Pin Name           | No. | Pin Name           | No. | Pin Name        |

|-----|--------------------|-----|--------------------|-----|--------------------|-----|-----------------|

| A1  | Vss                | B17 | SysAD27            | D12 | Vss                | H4  | V <sub>DD</sub> |

| A2  | Vss                | B18 | V <sub>DD</sub> IO | D13 | SysAD31            | H18 | Vss             |

| А3  | VDDIO              | B19 | VDDIO              | D14 | V <sub>DD</sub>    | H19 | Vss             |

| A4  | VDDIO              | B20 | Vss                | D15 | SysAD60            | H20 | Vss             |

| A5  | Reset#             | B21 | Vss                | D16 | Vss                | H21 | SysAD21         |

| A6  | PReq#              | C1  | V <sub>DD</sub> IO | D17 | SysAD26            | J1  | SysCmd7         |

| A7  | ValidIn#           | C2  | V <sub>DD</sub> IO | D18 | Vss                | J2  | SysCmd8         |

| A8  | ValidOut#          | С3  | Vss                | D19 | Vss                | J3  | TIntSel         |

| A9  | Vss                | C4  | Vss                | D20 | V <sub>DD</sub> IO | J4  | Int0#           |

| A10 | SysADC7            | C5  | Vss                | D21 | V <sub>DD</sub> IO | J18 | SysAD52         |

| A11 | SysADC3            | C6  | V <sub>DD</sub>    | E1  | SysCmd0            | J19 | SysAD20         |

| A12 | SysADC1            | C7  | WrRdy#             | E2  | DisDValidO#        | J20 | SysAD51         |

| A13 | SysADC4            | C8  | Vss                | E3  | DWBTrans#          | J21 | SysAD19         |

| A14 | SysAD62            | C9  | SysID1             | E4  | O3Return#          | K1  | Int1#           |

| A15 | SysAD30            | C10 | V <sub>DD</sub>    | E18 | SysAD57            | K2  | Vss             |

| A16 | SysAD28            | C11 | SysADC2            | E19 | SysAD25            | КЗ  | Vss             |

| A17 | SysAD59            | C12 | Vss                | E20 | SysAD56            | K4  | Vss             |

| A18 | V <sub>DD</sub> IO | C13 | SysAD63            | E21 | SysAD24            | K18 | V <sub>DD</sub> |

| A19 | V <sub>DD</sub> IO | C14 | V <sub>DD</sub>    | F1  | SysCmd1            | K19 | V <sub>DD</sub> |

| A20 | Vss                | C15 | SysAD29            | F2  | Vss                | K20 | V <sub>DD</sub> |

| A21 | Vss                | C16 | Vss                | F3  | Vss                | K21 | V <sub>DD</sub> |

| B1  | Vss                | C17 | SysAD58            | F4  | Vss                | L1  | Int2#           |

| B2  | Vss                | C18 | V <sub>DD</sub> IO | F18 | V <sub>DD</sub>    | L2  | Int3#           |

| В3  | VddIO              | C19 | Vss                | F19 | V <sub>DD</sub>    | L3  | Int4#           |

| B4  | VddIO              | C20 | V <sub>DD</sub> IO | F20 | V <sub>DD</sub>    | L4  | Int5#           |

| B5  | ColdReset#         | C21 | V <sub>DD</sub> IO | F21 | SysAD55            | L18 | SysAD17         |

| В6  | Release#           | D1  | VDDIO              | G1  | SysCmd2            | L19 | SysAD49         |

| B7  | ExtRqst#           | D2  | VDDIO              | G2  | SysCmd3            | L20 | SysAD18         |

| B8  | BusMode            | D3  | Vss                | G3  | SysCmd4            | L21 | SysAD50         |

| В9  | SysID2             | D4  | Vss                | G4  | SysCmd5            | M1  | RMode#/BKTGIO#  |

| B10 | V <sub>DD</sub>    | D5  | IC                 | G18 | SysAD23            | M2  | V <sub>DD</sub> |

| B11 | SysADC6            | D6  | V <sub>DD</sub>    | G19 | SysAD54            | МЗ  | V <sub>DD</sub> |

| B12 | Vss                | D7  | RdRdy#             | G20 | SysAD22            | M4  | V <sub>DD</sub> |

| B13 | SysADC0            | D8  | Vss                | G21 | SysAD53            | M18 | Vss             |

| B14 | V <sub>DD</sub>    | D9  | SysID0             | H1  | SysCmd6            | M19 | Vss             |

| B15 | SysAD61            | D10 | V <sub>DD</sub>    | H2  | V <sub>DD</sub>    | M20 | Vss             |

| B16 | Vss                | D11 | SysADC5            | НЗ  | V <sub>DD</sub>    | M21 | Vss             |

Caution Leave the IC pin open.

Remark # indicates active low.

(2/2)

| No. | Pin Name           | No. | Pin Name           | No. | Pin Name            | No.  | Pin Name            |

|-----|--------------------|-----|--------------------|-----|---------------------|------|---------------------|

| N1  | V <sub>DD</sub> IO | T21 | SysAD12            | W2  | VDDIO               | Y12  | V <sub>DD</sub>     |

| N2  | NMI#               | U1  | NTrcClk            | W3  | Vss                 | Y13  | SysAD3              |

| N3  | V <sub>DD</sub> IO | U2  | NTrcData0          | W4  | Vss                 | Y14  | Vss                 |

| N4  | BigEndian          | U3  | NTrcData1          | W5  | V <sub>DD</sub> PA2 | Y15  | SysAD37             |

| N18 | SysAD15            | U4  | NTrcData3          | W6  | Vss                 | Y16  | SysAD39             |

| N19 | SysAD47            | U18 | SysAD10            | W7  | V <sub>DD</sub> IO  | Y17  | SysAD40             |

| N20 | SysAD16            | U19 | SysAD42            | W8  | V <sub>DD</sub>     | Y18  | V <sub>DD</sub> IO  |

| N21 | SysAD48            | U20 | SysAD11            | W9  | JTDI                | Y19  | V <sub>DD</sub> IO  |

| P1  | Vss                | U21 | SysAD43            | W10 | Vss                 | Y20  | Vss                 |

| P2  | Vss                | V1  | NTrcData2          | W11 | SysAD1              | Y21  | Vss                 |

| P3  | Vss                | V2  | NTrcEnd            | W12 | V <sub>DD</sub>     | AA1  | Vss                 |

| P4  | Vss                | V3  | Vss                | W13 | SysAD35             | AA2  | Vss                 |

| P18 | V <sub>DD</sub>    | V4  | Vss                | W14 | Vss                 | AA3  | V <sub>DD</sub> IO  |

| P19 | V <sub>DD</sub>    | V5  | VssPA2             | W15 | SysAD38             | AA4  | V <sub>DD</sub> IO  |

| P20 | V <sub>DD</sub>    | V6  | Vss                | W16 | V <sub>DD</sub>     | AA5  | V <sub>DD</sub> PA1 |

| P21 | SysAD46            | V7  | V <sub>DD</sub> IO | W17 | SysAD9              | AA6  | V <sub>DD</sub> IO  |

| R1  | DivMode0           | V8  | V <sub>DD</sub>    | W18 | Vss                 | AA7  | IC                  |

| R2  | DivMode1           | V9  | JTMS               | W19 | Vss                 | AA8  | JTDO                |

| R3  | DivMode2           | V10 | Vss                | W20 | V <sub>DD</sub> IO  | AA9  | DrvCon              |

| R4  | VDDIO              | V11 | SysAD33            | W21 | V <sub>DD</sub> IO  | AA10 | Vss                 |

| R18 | SysAD44            | V12 | V <sub>DD</sub>    | Y1  | Vss                 | AA11 | SysAD0              |

| R19 | SysAD13            | V13 | SysAD4             | Y2  | Vss                 | AA12 | SysAD2              |

| R20 | SysAD45            | V14 | Vss                | Y3  | V <sub>DD</sub> IO  | AA13 | SysAD34             |

| R21 | SysAD14            | V15 | SysAD7             | Y4  | V <sub>DD</sub> IO  | AA14 | SysAD36             |

| T1  | V <sub>DD</sub>    | V16 | V <sub>DD</sub>    | Y5  | VssPA1              | AA15 | SysAD5              |

| T2  | V <sub>DD</sub>    | V17 | SysAD41            | Y6  | SysClock            | AA16 | SysAD6              |

| Т3  | V <sub>DD</sub>    | V18 | Vss                | Y7  | JTRST# (Vss)        | AA17 | SysAD8              |

| T4  | V <sub>DD</sub>    | V19 | Vss                | Y8  | V <sub>DD</sub>     | AA18 | VDDIO               |

| T18 | Vss                | V20 | V <sub>DD</sub> IO | Y9  | JTCK                | AA19 | VDDIO               |

| T19 | Vss                | V21 | V <sub>DD</sub> IO | Y10 | Vss                 | AA20 | Vss                 |

| T20 | Vss                | W1  | V <sub>DD</sub> IO | Y11 | SysAD32             | AA21 | Vss                 |

Caution Leave the IC pin open.

**Remarks 1.** The name in parentheses indicates the pin name in the revision 1.x product.

2. # indicates active low.

NEC  $\mu$ PD30550

#### **PIN NAMES**

Big Endian: Big endian PReq#: Processor request

BKTGIO#: Break/trigger input/output RdRdy#: Read ready

BusMode: Bus mode Release#: Release

ColdReset#: Cold reset Reset#: Reset

DisDValidO#: Disable delay ValidOut# SysAD(63:0): System address/data bus

DivMode(2:0): Divide mode SysADC(7:0): System address/data check

DrvCon: Driver control bus

DWBTrans#: Doubleword block transfer SysClock: System clock

ExtRqst#: SysCmd(8:0): System command/data

IC Internally connected identifier bus

Int(5:0)#:InterruptSysID(2:0):System bus identifierJTCK:JTAG clockTIntSel:Timer interrupt selection

JTDI: JTAG data input ValidIn#: Valid input

JTDO: JTAG data output ValidOut#: Valid output

JTMS: JTAG mode select VDD: Power supply for CPU core

JTRST#: JTAG reset VDDIO: Power supply for I/O NMI#: VDDPA1, VDDPA2: Quiet VDD for PLL

NTrcClk: N-Trace clock Vss: Ground

NTrcData(3:0): N-Trace data output VssPA1, VssPA2: Quiet Vss for PLL

NTrcEnd: N-Trace end WrRdy#: Write ready

O3Return#: Out-of-Order Return mode

Remark # indicates active low.

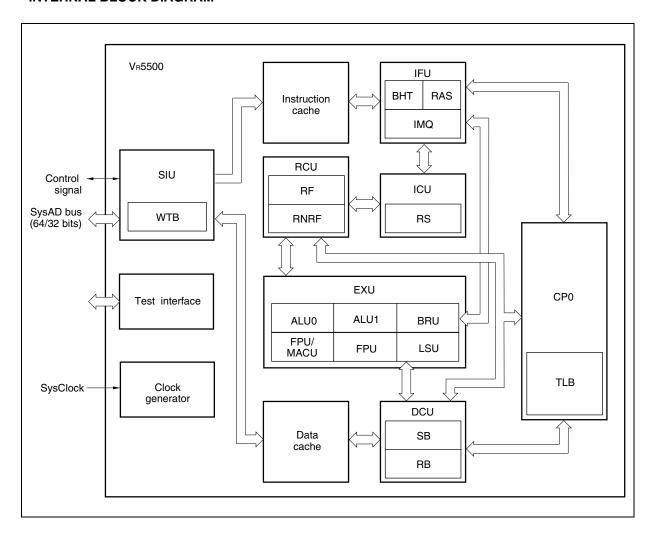

# **INTERNAL BLOCK DIAGRAM**

# **CONTENTS**

| 1. | PIN F | UNCTIONS                              | 8  |

|----|-------|---------------------------------------|----|

|    | 1.1   | List of Pin Functions                 | 8  |

|    | 1.2   | Recommended Connection of Unused Pins | 12 |

| 2. | ELEC  | TRICAL SPECIFICATIONS                 | 14 |

| 3. | PACK  | KAGE DRAWING                          | 24 |

| 4. | RECO  | DMMENDED SOLDERING CONDITIONS         | 25 |

# 1. PIN FUNCTIONS

Remark # indicates active low.

#### 1.1 List of Pin Functions

# (1) System interface signals

| Pin Name    | I/O    | Function                                                                                                                                                                                                                                                                                                                     |

|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SysAD(63:0) | I/O    | System address/data bus  A 64-bit bus for communication between the processor and external agent. The lower 32 bits (SysAD(31:0)) are used in 32-bit bus mode.                                                                                                                                                               |

| SysADC(7:0) | I/O    | System address/data check bus A bus for SysAD bus parity. Valid only during a data cycle. The lower 4 bits (SysADC(3:0)) are used in 32-bit bus mode.                                                                                                                                                                        |

| SysCmd(8:0) | I/O    | System command/data ID bus  A 9-bit bus that transfers command and data identifiers between the processor and external agent                                                                                                                                                                                                 |

| SysID(2:0)  | I/O    | System bus protocol ID  These signals transfer request identifiers in the out-of-order return mode.  The processor drives a valid identifier in synchronization with the activation of the ValidOut# signal.  The external agent must drive valid identifiers in synchronization with the activation of the ValidIn# signal. |

| ValidIn#    | Input  | Valid In  A signal indicating that the external agent is driving a valid address or data onto the SysAD bus, a valid command or data identifier onto the SysCmd bus, or a valid request identifier onto the SysID bus in the out-of-order return mode.                                                                       |

| ValidOut#   | Output | Valid out  A signal indicating that the processor is driving a valid address or data onto the SysAD bus, a valid command or data identifier onto the SysCmd bus, or a valid request identifier onto the SysID bus in the out-of-order return mode.                                                                           |

| RdRdy#      | Input  | Read ready  A signal indicating that the external agent is ready to accept a processor read request                                                                                                                                                                                                                          |

| WrRdy#      | Input  | Write ready  A signal indicating that the external agent is ready to accept a processor write request                                                                                                                                                                                                                        |

| ExtRqst#    | Input  | External request A signal indicating that the external agent is requesting the right to use the system interface                                                                                                                                                                                                             |

| Release#    | Output | Releases interface A signal indicating that the processor is releasing the system interface to a slave state                                                                                                                                                                                                                 |

| PReq#       | Output | Processor request A signal indicating that the processor has a request that is pending                                                                                                                                                                                                                                       |

# (2) Initialization interface signals

(1/2)

| Pin Name     | I/O   | Function                                                                                                                                                                                                                                                                                                                                        |

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DivMode(2:0) | Input | Division mode  These signals set the division ratio of PClock and SysClock as follows:  111: 5.5  110: 5  101: 4.5  100: 4  011: 3.5  010: 3  001: 2.5  000: 2  Set the input levels of these signals before a power-on reset. Make sure that the levels of these signals do not change while the VR5500 is operating.                          |

| BigEndian    | Input | Endian mode  This signal sets the byte ordering for addressing.  1: Big endian  0: Little endian  Set the input level of this signal before a power-on reset. Make sure that the level of this signal does not change while the VR5500 is operating.                                                                                            |

| BusMode      | Input | Bus mode This signal sets the bus width of the system interface.  1: 64 bits 0: 32 bits Set the input level of this signal before a power-on reset. Make sure that the level of this signal does not change while the VR5500 is operating.                                                                                                      |

| TIntSel      | Input | Interrupt source select  This signal sets the interrupt source to be assigned to the IP7 bit of the Cause register.  1: Timer interrupt  0: Int5# input and external write request (SysAD5)  Set the input level of this signal before a power-on reset. Make sure that the level of this signal does not change while the VR5500 is operating. |

| DisDValidO#  | Input | ValidOut# delay enable  1: ValidOut# is active even while the address cycle is stalled  0: ValidOut# is active during the address issuance cycle only  Set the input level of this signal before a power-on reset. Make sure that the level of this signal does not change while the VR5500 is operating.                                       |

| DWBTrans#    | Input | Doubleword block transfer enable (valid in 32-bit bus mode only)  1: Disabled  0: Enabled  Set the input level of this signal before a power-on reset. Make sure that the level of this signal does not change while the VR5500 is operating.                                                                                                   |

Remark 1: High level, 0: Low level

(2/2)

| Pin Name   | I/O   | Function                                                                                                                                                                                                                                                                          |

|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O3Return#  | Input | Out-of-Order Return mode  This signal sets the protocol of the system interface.  1: Normal mode  0: Out-of-order return mode  Set the input level of this signal before a power-on reset. Make sure that the level of this signal does not change while the VR5500 is operating. |

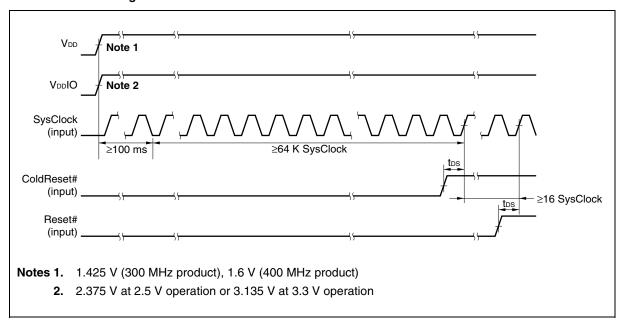

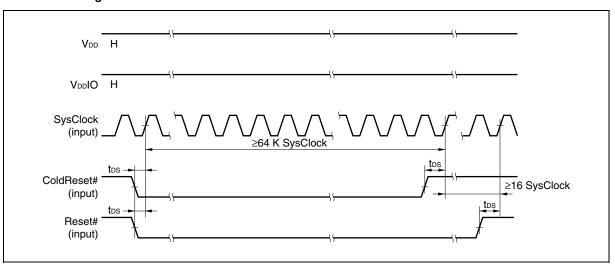

| ColdReset# | Input | Cold reset  This signal completely initializes the internal status of the processor. Deassert it in synchronization with SysClock.                                                                                                                                                |

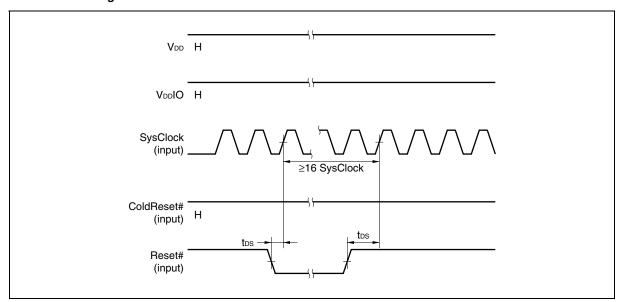

| Reset#     | Input | Reset This signal logically initializes the internal status of the processor. Deassert it in synchronization with SysClock.                                                                                                                                                       |

| DrvCon     | Input | Drive control  This signal sets the impedance of the external output driver.  1: Low  0: Normal (recommended)  Set the input level of this signal before a power-on reset. Make sure that the level of this signal does not change while the VR5500 is operating.                 |

|            |       | Remark Applies to revision 2.0 or later products. Fixed to 0 in revision 1.x products.                                                                                                                                                                                            |

Remark 1: High level, 0: Low level

The O3Return#, DWBTrans#, DisDValidO#, and BusMode signals are used for determining the protocol of the system interface. The protocol is selected as follows in accordance with the setting of these signals.

| Protocol                                    | O3Return# | DWBTrans# | DisDValidO# | BusMode   |

|---------------------------------------------|-----------|-----------|-------------|-----------|

| V <sub>R</sub> 5000 <sup>™</sup> compatible | 1         | 1         | 1           | 1         |

| RM523x compatible                           | 1         | 1         | 1           | 0         |

| V <sub>R</sub> 5432 native mode compatible  | 1         | 0         | 0           | 0         |

| Out-of-order return mode                    | 0         | Arbitrary | Arbitrary   | Arbitrary |

**Remark** 1: High level, 0:Low level

RM523x is a product of PMC-Sierra, Inc.

# (3) Interrupt interface signals

| Pin Name  | I/O   | Function                                                                                                       |

|-----------|-------|----------------------------------------------------------------------------------------------------------------|

| Int(5:0)# | Input | Interrupt                                                                                                      |

|           |       | These are general-purpose processor interrupt requests. The input states can be checked by the Cause register. |

|           |       | Whether Int5# is acknowledged or not depends on the status of the TIntSel signal during reset.                 |

| NMI#      | Input | Non-maskable interrupt                                                                                         |

|           |       | This is the non-maskable interrupt request.                                                                    |

#### (4) Clock interface signals

| Pin Name            | I/O   | Function                          |

|---------------------|-------|-----------------------------------|

| SysClock            | Input | System clock                      |

|                     |       | Clock input to the processor      |

| V <sub>DD</sub> PA1 | -     | V <sub>DD</sub> for PLL           |

| VDDPA2              |       | Power supply for the internal PLL |

| VssPA1              | _     | Vss for PLL                       |

| VssPA2              |       | Ground for the internal PLL       |

# (5) Power supply

| Pin Name           | I/O | Function                  |

|--------------------|-----|---------------------------|

| $V_{DD}$           | _   | Power supply pin for core |

| V <sub>DD</sub> IO | _   | Power supply pin for I/O  |

| Vss                | _   | Ground potential pin      |

Caution The V<sub>R</sub>5500 uses two power supply pins. These power supply pins can be applied in any sequence. However, power must not be applied to one pin for 100 ms or longer while it is not applied to the other.

# (6) Test interface signals

| Pin Name      | I/O    | Function                                                                                                                |

|---------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| NTrcData(3:0) | Output | Trace data                                                                                                              |

|               |        | Trace data output                                                                                                       |

| NTrcEnd       | Output | Trace end                                                                                                               |

|               |        | A signal that indicates the end of a trace data packet.                                                                 |

| NTrcClk       | Output | Trace clock                                                                                                             |

|               |        | Clock for the test interface. The same clock as SysClock is output.                                                     |

| RMode#/       | I/O    | Reset mode/break trigger I/O                                                                                            |

| BKTGIO#       |        | A debug reset mode input signal while the JTRST# signal (ColdReset# signal for revision 1.x products) is active.        |

|               |        | It serves as a break or trigger I/O signal during normal operation.                                                     |

| JTDI          | Input  | JTAG data input                                                                                                         |

|               |        | Serial data input for JTAG                                                                                              |

| JTDO          | Output | JTAG data output                                                                                                        |

|               |        | Serial data output for JTAG. Output is performed in synchronization with the fall of JTCK.                              |

| JTMS          | Input  | JTAG mode select                                                                                                        |

|               |        | This signal selects the JTAG test mode.                                                                                 |

| JTCK          | Input  | JTAG clock input                                                                                                        |

|               |        | Serial clock input for JTAG. The maximum frequency is 33 MHz. There is no need for it to be synchronized with SysClock. |

| JTRST#        | Input  | JTAG reset input                                                                                                        |

|               |        | A signal for initializing the JTAG test module.                                                                         |

|               |        | Remark Revision 2.0 or later products only.                                                                             |

#### 1.2 Recommended Connection of Unused Pins

#### (1) System interface pins

#### (a) 32-bit bus mode

The  $V_R5500$  allows selection of a SysAD bus width from 64 bits or 32 bits. When the 32-bit bus mode is selected, the  $V_R5500$  operates using only the required system interface pins. Therefore, set the unused pins as follows when operating the  $V_R5500$  in the 32-bit bus mode.

| Pin Name     | Recommended Connection of Unused Pins |

|--------------|---------------------------------------|

| SysAD(63:32) | Leave open                            |

| SysADC(7:4)  | Leave open                            |

#### (b) Normal mode

The  $V_R5500$  can process read/write transactions regardless of the order in which requests are issued in the out-of-order return mode. The SysID(2:0) signals are used to identify each request during this processing. Set these signals, which are not used in the normal mode, as follows.

| Pin Name   | Recommended Connection |

|------------|------------------------|

|            | of Unused Pins         |

| SysID(2:0) | Leave open             |

#### (c) Parity bus

The V<sub>R</sub>5500 allows selection of whether the data is protected using parity. When parity is used, the parity data is output from the processor or external agent to the SysADC bus.

However, whether the parity is used or not is selected by software, so unless the program is started, the  $V_R5500$  cannot determine the operation of the SysADC bus. Therefore, care must be taken to prevent the SysADC bus from being left open or in a high-impedance state.

When parity is not used, it is recommended to connect each pin of the SysADC bus to VDDIO via a resistor with a high resistance value.

#### (2) Test interface pins

The  $V_R5500$  can be used to perform testing and debugging with the device mounted on the board. The test interface pins are used for connection with the external debug tool during such debugging. Therefore set the test interface pins as follows when the debug function is not used and in the normal operation mode.

| Pin Name               | Recommended Connection of<br>Unused Pins |

|------------------------|------------------------------------------|

| JTCK                   | Pull up                                  |

| JTDI                   | Pull up                                  |

| JTMS                   | Pull up                                  |

| JTRST# <sup>Note</sup> | Pull down                                |

| JTDO                   | Leave open                               |

| NTrcClk                | Leave open                               |

| NTrcData(3:0)          | Leave open                               |

| NTrcEnd                | Leave open                               |

| RMode#/BKTGIO#         | Pull up                                  |

Note Revision 2.0 or later products only.

#### 2. ELECTRICAL SPECIFICATIONS

#### **Absolute Maximum Ratings**

| Parameter                     | Symbol             | Conditions              | Ratings                          | Unit |

|-------------------------------|--------------------|-------------------------|----------------------------------|------|

| Supply voltage                | V <sub>DD</sub> IO |                         | -0.5 to +4.0                     | V    |

|                               | V <sub>DD</sub>    |                         | -0.5 to +2.0                     | V    |

|                               | VDDP               |                         | -0.5 to +2.0                     | V    |

| Input voltage <sup>Note</sup> | Vı                 |                         | -0.5 to V <sub>DD</sub> IO + 0.3 | V    |

|                               |                    | Pulse of less than 7 ns | -1.5 to V <sub>DD</sub> IO + 0.3 | V    |

| Operating case temperature    | Tc                 |                         | -10 to +85                       | °C   |

| Storage temperature           | T <sub>stg</sub>   |                         | -40 to +125                      | °C   |

**Note** The upper limit of the input voltage (VDDIO + 0.3) is +4.0 V.

Cautions 1. Do not short-circuit two or more outputs at the same time.

2. Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

The specifications and conditions shown in the following DC Characteristics and AC Characteristics sections are the ranges within which the product can normally operate and the quality can be guaranteed.

#### **Operating conditions**

#### (1) 300 MHz product

| Parameter      | Symbol          | Conditions | MIN.  | MAX.  | Unit |

|----------------|-----------------|------------|-------|-------|------|

| Supply voltage | VDDIO           |            | 2.375 | 2.625 | ٧    |

|                |                 |            | 3.135 | 3.465 | V    |

|                | V <sub>DD</sub> |            | 1.425 | 1.575 | V    |

|                | VDDP            |            | 1.425 | 1.575 | V    |

Caution V<sub>DD</sub> can also be used with the voltage range of the 400 MHz product (1.6 to 1.7 V). In this case, internal operation at 300 MHz is guaranteed. The supply current of the core block in this case is the specified value of the 400 MHz product (MAX. 1.8 A).

#### (2) 400 MHz product

| Parameter      | Symbol            | Conditions | MIN.  | MAX.  | Unit |

|----------------|-------------------|------------|-------|-------|------|

| Supply voltage | VDDIO             |            | 2.375 | 2.625 | V    |

|                |                   |            | 3.135 | 3.465 | V    |

|                | V <sub>DD</sub>   |            | 1.6   | 1.7   | V    |

|                | V <sub>DD</sub> P |            | 1.6   | 1.7   | V    |

Caution V<sub>DD</sub> can also be used with the voltage range of the 300 MHz product (1.425 to 1.575 V). In this case, internal operation at 300 MHz is guaranteed. The supply current of the core block in this case is the specified value of the 300 MHz product (MAX. 1.4 A).

# **Supply Current**

| Parameter                    | Symbol | Conditions                        | MIN. | MAX. | Unit |

|------------------------------|--------|-----------------------------------|------|------|------|

| Supply current of core block | IDD    | 300 MHz product, during normal    |      | 1.4  | Α    |

|                              |        | operation,                        |      |      |      |

|                              |        | $V_{DD} = V_{DD}P = 1.575 V$      |      |      |      |

|                              |        | 400 MHz product, during normal    |      | 1.8  | Α    |

|                              |        | operation,                        |      |      |      |

|                              |        | $V_{DD} = V_{DD}P = 1.7 V$        |      |      |      |

|                              | loo_sb | 300 MHz product, in standby mode, |      | 0.35 | Α    |

|                              |        | $V_{DD} = V_{DD}P = 1.575 V$      |      |      |      |

|                              |        | 400 MHz product, in standby mode, |      | 0.45 | Α    |

|                              |        | $V_{DD} = V_{DD}P = 1.7 V$        |      |      |      |

**Remark** The supply current in the I/O block varies depending on the application used. It is normally 20% I<sub>DD</sub> or lower.

# **DC Characteristics**

(1) When  $V_{DD}IO = 2.5 V \pm 5\%$

(300 MHz product:  $T_C = -10$  to  $+85^{\circ}C$ ,  $V_{DDIO} = 2.5$  V  $\pm 5\%$ ,  $V_{DD} = V_{DD}P = 1.5$  V  $\pm 5\%$ ) (400 MHz product:  $T_C = -10$  to  $+85^{\circ}C$ ,  $V_{DDIO} = 2.5$  V  $\pm 5\%$ ,  $V_{DD} = V_{DD}P = 1.6$  to 1.7 V)

| Parameter                             | Symbol | Conditions                                         | MIN.                  | MAX.                     | Unit |

|---------------------------------------|--------|----------------------------------------------------|-----------------------|--------------------------|------|

| Output voltage, high                  | Vон    | V <sub>DD</sub> IO = MIN., I <sub>OH</sub> = -4 mA | $0.8 \times V_{DDIO}$ |                          | V    |

| Output voltage, low                   | Vol    | VDDIO = MIN., IOL = 4 mA                           |                       | 0.4                      | V    |

| Input voltage, high <sup>Note 1</sup> | ViH    |                                                    | 2.0                   | V <sub>DD</sub> IO + 0.3 | V    |

| Input voltage, low <sup>Note 1</sup>  | VIL    |                                                    | -0.5                  | 0.2 × V <sub>DD</sub> IO | V    |

|                                       |        | Pulse of less than 7 ns                            | -1.5                  | 0.2 × V <sub>DD</sub> IO | V    |

| Input voltage, high <sup>Note 2</sup> | VIHC   |                                                    | 0.8 × VddIO           | V <sub>DD</sub> IO + 0.3 | V    |

| Input voltage, low <sup>Note 2</sup>  | VILC   |                                                    | -0.5                  | 0.2 × VDDIO              | V    |

|                                       |        | Pulse of less than 7 ns                            | -1.5                  | 0.2 × VDDIO              | V    |

| Input current leakage, high           | Ішн    | VI = VDDIO                                         |                       | 5.0                      | μΑ   |

| Input current leakage, low            | luc    | V <sub>I</sub> = 0 V                               |                       | -5.0                     | μΑ   |

| Output current leakage, high          | Ісон   | Vo = VddIO                                         |                       | 5.0                      | μΑ   |

| Output current leakage, low           | ILOL   | Vo = 0 V                                           |                       | -5.0                     | μΑ   |

Notes 1. Does not apply to the SysClock pin.

2. Only applies to the SysClock pin.

(2) When  $V_{DDIO} = 3.3 \text{ V} \pm 5\%$

(300 MHz product:  $T_C = -10$  to  $+85^{\circ}C$ ,  $V_{DDIO} = 3.3$  V  $\pm 5\%$ ,  $V_{DD} = V_{DD}P = 1.5$  V  $\pm 5\%$ ) (400 MHz product:  $T_C = -10$  to  $+85^{\circ}C$ ,  $V_{DDIO} = 3.3$  V  $\pm 5\%$ ,  $V_{DD} = V_{DD}P = 1.6$  to 1.7 V)

| Parameter                             | Symbol | Conditions                | MIN.        | MAX.                     | Unit |

|---------------------------------------|--------|---------------------------|-------------|--------------------------|------|

| Output voltage, high                  | Vон    | VDDIO = MIN., IOH = -4 mA | 2.4         |                          | V    |

| Output voltage, low                   | Vol    | VDDIO = MIN., IOL = 4 mA  |             | 0.4                      | V    |

| Input voltage, high <sup>Note 1</sup> | VIH    |                           | 2.0         | V <sub>DD</sub> IO + 0.3 | V    |

| Input voltage, low <sup>Note 1</sup>  | VIL    |                           | -0.5        | 0.8                      | V    |

|                                       |        | Pulse of less than 7 ns   | -1.5        | 0.8                      | V    |

| Input voltage, high <sup>Note 2</sup> | VIHC   |                           | O.8 × VDDIO | V <sub>DD</sub> IO + 0.3 | V    |

| Input voltage, low Note 2             | VILC   |                           | -0.5        | 0.2 × VDDIO              | V    |

|                                       |        | Pulse of less than 7 ns   | -1.5        | 0.2 × VDDIO              | ٧    |

| Input current leakage, high           | Ішн    | VI = VDDIO                |             | 5.0                      | μΑ   |

| Input current leakage, low            | ILIL   | Vi = 0 V                  |             | -5.0                     | μΑ   |

| Output current leakage, high          | Ісон   | Vo = VDDIO                |             | 5.0                      | μΑ   |

| Output current leakage, low           | ILOL   | Vo = 0 V                  |             | -5.0                     | μΑ   |

Notes 1. Does not apply to the SysClock pin.

2. Only applies to the SysClock pin.

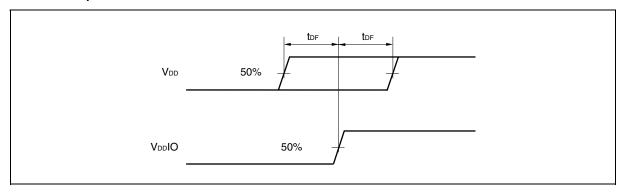

#### **Power-on Sequence**

The VR5500 uses two power supply pins. These power supply pins can be applied in any sequence. However, power must not be applied to one pin for 100 ms or longer while it is not applied to the other.

| Parameter      | Symbol | Conditions | MIN. | MAX. | Unit |

|----------------|--------|------------|------|------|------|

| Power-on delay | tof    |            | 0    | 100  | ms   |

# Capacitance (TA = 25°C, VDDIO = VDD = VDDP = 0 V)

| Parameter          | Symbol | Conditions                      | MIN. | MAX. | Unit |

|--------------------|--------|---------------------------------|------|------|------|

| Input capacitance  | Cin    | fc = 1 MHz                      |      | 5.0  | pF   |

| Output capacitance | Соит   | Unmeasured pins returned to 0 V |      | 7.0  | pF   |

#### **AC Characteristics**

(300 MHz product:  $T_C = -10$  to +85,  $V_{DDIO} = 2.5$  V  $\pm 5\%$ , 3.3 V  $\pm 5\%$ ,  $V_{DD} = V_{DDP} = 1.5$  V  $\pm 5\%$ ) (400 MHz product:  $T_C = -10$  to +85,  $V_{DDIO} = 2.5$  V  $\pm 5\%$ , 3.3 V  $\pm 5\%$ ,  $V_{DD} = V_{DDP} = 1.6$  to 1.7 V)

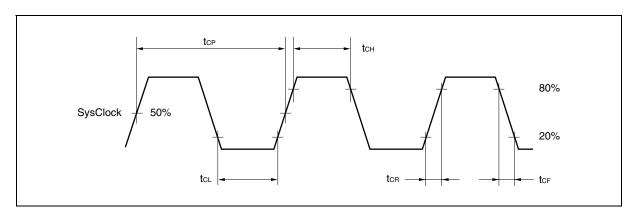

# Clock parameters (1/2)

| Parameter                              | Symbol |            | Conditions      | MIN. | MAX. | Unit |

|----------------------------------------|--------|------------|-----------------|------|------|------|

| System clock high-level width          | tсн    |            |                 | 1.8  |      | ns   |

| System clock low-level width           | tcL    |            |                 | 1.8  |      | ns   |

| Pipeline clock frequency               |        | 300 MHz pi | roduct          | 200  | 300  | MHz  |

|                                        |        | 400 MHz pi | roduct          | 200  | 400  | MHz  |

| System clock frequency <sup>Note</sup> |        | 300 MHz    | DivMode = 2:1   | 100  | 133  | MHz  |

|                                        |        | product    | DivMode = 2.5:1 | 80   | 120  | MHz  |

|                                        |        |            | DivMode = 3:1   | 66.7 | 100  | MHz  |

|                                        |        |            | DivMode = 3.5:1 | 57.2 | 85.7 | MHz  |

|                                        |        |            | DivMode = 4:1   | 50   | 75   | MHz  |

|                                        |        |            | DivMode = 4.5:1 | 44.5 | 66.6 | MHz  |

|                                        |        |            | DivMode = 5:1   | 40   | 60   | MHz  |

|                                        |        |            | DivMode = 5.5:1 | 36.4 | 54.5 | MHz  |

|                                        |        | 400 MHz    | DivMode = 2:1   | 100  | 133  | MHz  |

|                                        |        | product    | DivMode = 2.5:1 | 80   | 133  | MHz  |

|                                        |        |            | DivMode = 3:1   | 66.7 | 133  | MHz  |

|                                        |        |            | DivMode = 3.5:1 | 57.2 | 114  | MHz  |

|                                        |        |            | DivMode = 4:1   | 50   | 100  | MHz  |

|                                        |        |            | DivMode = 4.5:1 | 44.5 | 88.8 | MHz  |

|                                        |        |            | DivMode = 5:1   | 40   | 80   | MHz  |

|                                        |        |            | DivMode = 5.5:1 | 36.4 | 72.7 | MHz  |

Note This is the frequency at which the operation of the internal PLL is guaranteed.

#### Clock parameters (2/2)

| Parameter              | Symbol |         | Conditions      | MIN. | MAX. | Unit |

|------------------------|--------|---------|-----------------|------|------|------|

| System clock cycle     | tcp    | 300 MHz | DivMode = 2:1   | 7.5  | 10   | ns   |

|                        |        | product | DivMode = 2.5:1 | 8.3  | 12.5 | ns   |

|                        |        |         | DivMode = 3:1   | 10   | 15   | ns   |

|                        |        |         | DivMode = 3.5:1 | 11.7 | 17.5 | ns   |

|                        |        |         | DivMode = 4:1   | 13.3 | 20   | ns   |

|                        |        |         | DivMode = 4.5:1 | 15   | 22.5 | ns   |

|                        |        |         | DivMode = 5:1   | 16.7 | 25   | ns   |

|                        |        |         | DivMode = 5.5:1 | 18.3 | 27.5 | ns   |

|                        |        | 400 MHz | DivMode = 2:1   | 7.5  | 10   | ns   |

|                        |        | product | DivMode = 2.5:1 | 7.5  | 12.5 | ns   |

|                        |        |         | DivMode = 3:1   | 7.5  | 15   | ns   |

|                        |        |         | DivMode = 3.5:1 | 8.8  | 17.5 | ns   |

|                        |        |         | DivMode = 4:1   | 10   | 20   | ns   |

|                        |        |         | DivMode = 4.5:1 | 11.3 | 22.5 | ns   |

|                        |        |         | DivMode = 5:1   | 12.5 | 25   | ns   |

|                        |        |         | DivMode = 5.5:1 | 13.8 | 27.5 | ns   |

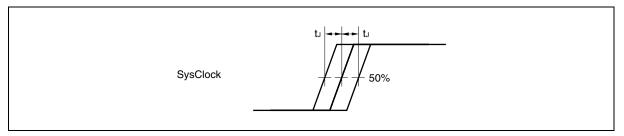

| System clock jitter    | tu     |         |                 |      | ±5   | %    |

| System clock rise time | tcr    |         |                 |      | 1.2  | ns   |

| System clock fall time | tcF    |         |                 |      | 1.2  | ns   |

| JTAG clock frequency   |        |         |                 |      | 33   | MHz  |

**Remarks 1.** The system clock jitter is a cycle-to-cycle jitter.

**2.** The JTAG clock runs asynchronously to the system clock.

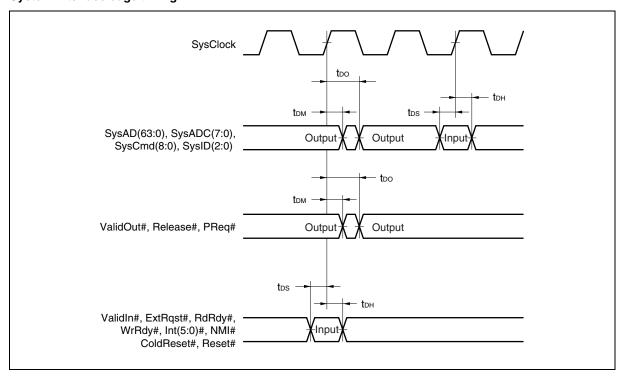

#### System interface parameters

| Parameter                                | Symbol | Conditions      | MIN. | MAX. | Unit |

|------------------------------------------|--------|-----------------|------|------|------|

| Data output hold time <sup>Note 1</sup>  | tом    |                 | 1.0  |      | ns   |

| Data output delay time <sup>Note 1</sup> | t□o    |                 |      | 5.0  | ns   |

| Data input setup time <sup>Note 2</sup>  | tos    |                 | 1.5  |      | ns   |

| Data input hold time <sup>Note 2</sup>   | tон    | 300 MHz product | 1.0  |      | ns   |

|                                          |        | 400 MHz product | 0.5  |      | ns   |

Notes 1. Applies to the Release#, ValidOut#, SysAD(63:0), SysADC(7:0), SysCmd(8:0), and SysID(2:0) pins.

2. Applies to the ColdReset#, Reset#, Int(5:0), NMI#, ExtRqst#, RdRdy#, ValidIn#, SysAD(63:0), SysADC(7:0), SysCmd(8:0), and SysID(2:0) pins.

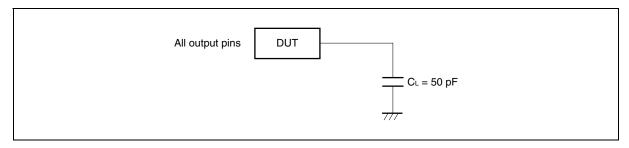

#### Load coefficient

| Parameter        | Symbol | Conditions | MIN. | MAX. | Unit     |

|------------------|--------|------------|------|------|----------|

| Load coefficient | CLD    |            |      | 1.0  | ns/25 pF |

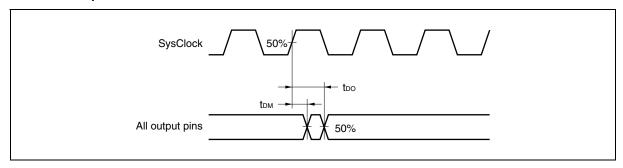

# **Measurement Conditions**

# **Measurement points**

# **Load conditions**

# **Timing Charts**

# **Clock timing**

# **Clock jitter**

# System interface edge timing

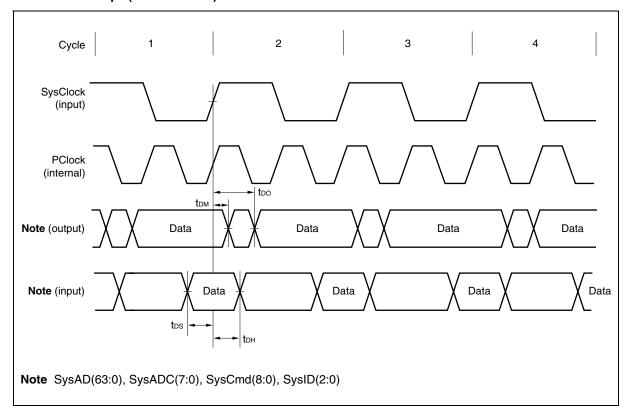

# Clock relationships (DivMode = 2:1)

# Power-on sequence

**Reset Timing**

#### Power-on reset timing

#### **Cold reset timing**

# Warm reset timing

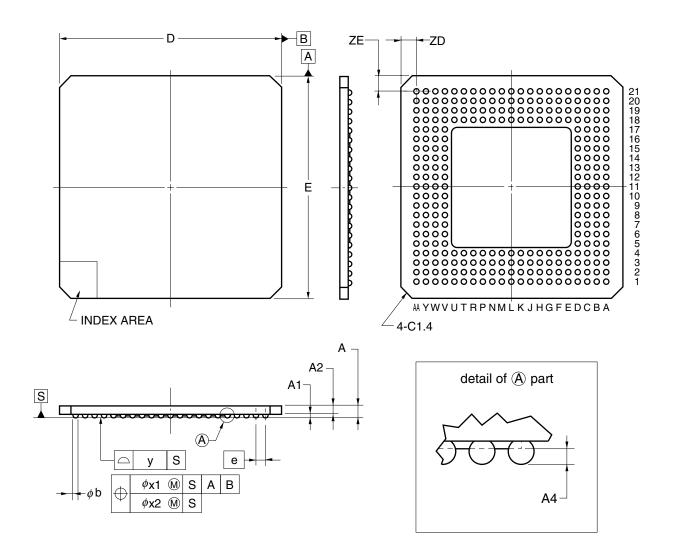

#### 3. PACKAGE DRAWING

# 272-PIN PLASTIC BGA (CAVITY DOWN ADVANCED TYPE) (29x29)

| ITEM | MILLIMETERS    |

|------|----------------|

| D    | 29.00±0.20     |

| E    | 29.00±0.20     |

| е    | 1.27           |

| Α    | 1.75±0.30      |

| Α1   | 0.60±0.10      |

| A2   | 1.15           |

| A4   | 0.25MIN.       |

| b    | φ0.75±0.15     |

| x1   | 0.30           |

| x2   | 0.15           |

| у    | 0.20           |

| ZD   | 1.80           |

| ZE   | 1.80           |

|      | P272F2-127-BA1 |

#### 4. RECOMMENDED SOLDERING CONDITIONS

This product should be soldered and mounted under the following recommended conditions.

For details on the recommended soldering conditions, refer to the **Semiconductor Device Mounting Technology Manual (C10535E)**.

For soldering methods and conditions other than those recommended below, contact an NEC sales representative.

Table 4-1. Surface mounting Type Soldering Conditions

$\mu$ PD30550F2-300-NN1: 272-pin plastic BGA (C/D advanced type) (29  $\times$  29)  $\mu$ PD30550F2-400-NN1: 272-pin plastic BGA (C/D advanced type) (29  $\times$  29)

| Soldering Method | Soldering Conditions                                                                                                                                                                              | Recommended Condition<br>Symbol |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Infrared reflow  | Package peak temperature: 235°C, Time: 30 seconds max. (at 210°C or higher), Count: Three times or less, Exposure limit: 3 days <sup>Note</sup> (after that, prebake at 125°C for 20 to 72 hours) | IR35-203-3                      |

**Note** After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.

#### **NOTES FOR CMOS DEVICES -**

# (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

**Reference document** Electrical Characteristics for Microcomputer (U15170J)<sup>Note</sup> **Note** This document number is that of Japanese version.

The related documents indicated in the publication may include preliminary versions. However, preliminary versions are not marked as such.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

# **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP, Brasil Tel: 11-6462-6810 Fax: 11-6462-6829

#### **NEC Electronics (Europe) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

#### • Sucursal en España

Madrid, Spain Tel: 091-504 27 87 Fax: 091-504 28 60

#### • Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### • Filiale Italiana

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### • Branch The Netherlands

Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

#### Branch Sweden

Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Shanghai, Ltd.**

Shanghai, P.R. China Tel: 021-6841-1138 Fax: 021-6841-1137

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### **NEC Electronics Singapore Pte. Ltd.**

Novena Square, Singapore

Tel: 253-8311 Fax: 250-3583 VR5000, VR5000 Series, VR5432, VR5500, and VR Series are trademarks of NEC Corporation.

MIPS is a registered trademark of MIPS Technologies, Inc. in the United States.

Exporting this product or equipment that includes this product may require a governmental license from the U.S.A. for some countries because this product utilizes technologies limited by the export control regulations of the U.S.A.

- The information contained in this document is being issued in advance of the production cycle for the

device. The parameters for the device may change before final production or NEC Corporation, at its own

discretion, may withdraw the device prior to its production.

- Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written

consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in

this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property

rights of third parties by or arising from use of a device described herein or any other liability arising from use

of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other

intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software, and information in the design of the customer's equipment shall be done under the full responsibility of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

- "Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.