#### DATA SHEET

# MOS INTEGRATED CIRCUIT $\mu PD6222$

#### I2C-BUS COMPATIBLE 8BIT 12CHANNEL D/A CONVERTER

#### **DESCRIPTION**

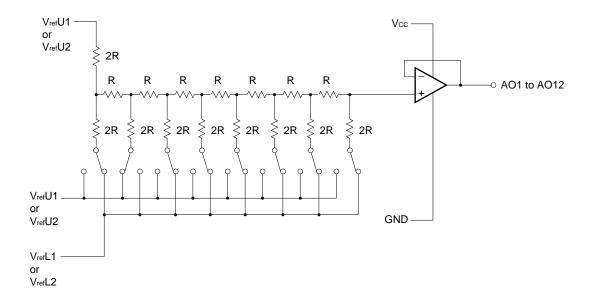

The  $\mu$ PD6222 is an 8-bit monolithic CMOS digital-to-analog converter using the R-2R technique. The  $\mu$ PD6222 incorporates a 12-channel digital-to-analog converters and I<sup>2</sup>C-bus compatible interface. The designer needs only 2 signals (Serial Data and Serial Clock) to interface and can use 8-ICs (96-channels) on same bus to control chipselect terminals.

The  $\mu$ PD6222 incorporates Output CMOS Buffer to achieve wide output voltage range and two reference voltage terminals.

The  $\mu$ PD6222 is ideal for automatic control for color-television.

#### **FEATURES**

- 12-channel 8-bit digital-to-analog converter using the R-2R ladder technique

- I<sup>2</sup>C-bus compatible serial interface (Serial Data and Serial Clock)

- 8-ICs (96-channels) can be connected by chip-select terminals

- · Output CMOS Buffer to achieve wide output voltage range

- Two reference voltage

#### ORDERING INFORMATION

| PART NO.  | PACKAGE                             |

|-----------|-------------------------------------|

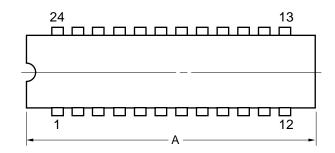

| μPD6222CS | 24-pin plastic shrink DIP (300 mil) |

| μPD6222GS | 24-pin plastic SOP (300 mil)        |

Caution Purchase of NEC I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C patent Right to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

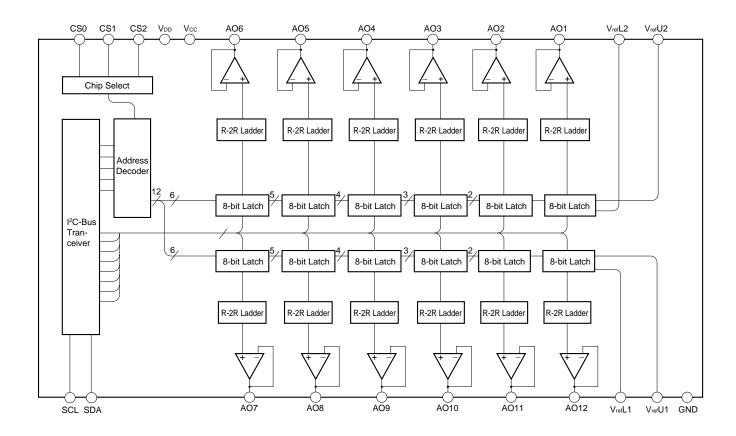

#### **BLOCK DIAGRAM**

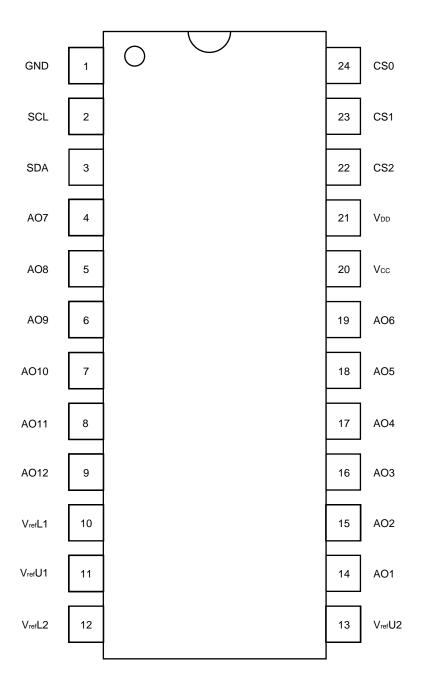

# PIN CONNECTION DIAGRAM (Top View)

#### PIN CONFIGURATION

| PIN NO. | SYMBOL              | FUNCTION                                                                      |

|---------|---------------------|-------------------------------------------------------------------------------|

| 1       | GND                 | Ground                                                                        |

| 2       | SCL                 | Serial Clock Input                                                            |

| 3       | SDA                 | Serial Data Input (Output: acknowledgement signal)                            |

| 4       | AO7                 | Analog Output Channel 7                                                       |

| 5       | AO8                 | Analog Output Channel 8                                                       |

| 6       | AO9                 | Analog Output Channel 9                                                       |

| 7       | AO10                | Analog Output Channel 10                                                      |

| 8       | AO11                | Analog Output Channel 11                                                      |

| 9       | AO12                | Analog Output Channel 12                                                      |

| 10      | VrefL1              | GND Side Reference Voltage Input 1 (The current of IrefL1 flows out from IC.) |

| 11      | V <sub>ref</sub> U1 | Vcc Side Reference Voltage Input 1 (The current of IrefU1 flows into IC.)     |

| 12      | V <sub>ref</sub> L2 | GND Side Reference Voltage Input 2 (The current of IrefL2 flows out from IC.) |

| 13      | V <sub>ref</sub> U2 | Vcc Side Reference Voltage Input 2 (The current of IrefU2 flows into IC.)     |

| 14      | AO1                 | Analog Output Channel 1                                                       |

| 15      | AO2                 | Analog Output Channel 2                                                       |

| 16      | AO3                 | Analog Output Channel 3                                                       |

| 17      | AO4                 | Analog Output Channel 4                                                       |

| 18      | AO5                 | Analog Output Channel 5                                                       |

| 19      | AO6                 | Analog Output Channel 6                                                       |

| 20      | Vcc                 | Analog Power Supply                                                           |

| 21      | V <sub>DD</sub>     | Digital Power Supply                                                          |

| 22      | CS2                 | Chip Select 2                                                                 |

| 23      | CS1                 | Chip Select 1                                                                 |

| 24      | CS0                 | Chip Select 0                                                                 |

**Note** For "Power On Reset" function, when this IC is powered on, Analog Output Data (D0, D1 ··· D7) will be set all 0. And the all Analog Output will be Zero Scale (1LSB + V<sub>ref</sub>L).

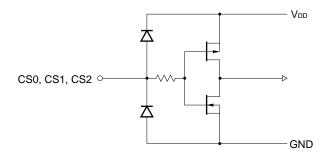

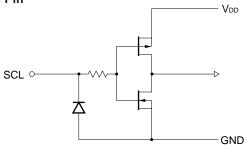

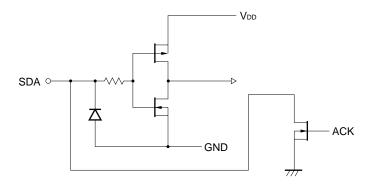

# **EQUIVALENT CIRCUIT OF PIN**

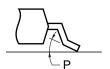

• Equivalent Circuit of CS0, CS1, CS2 Pins

• Equivalent Circuit of SCL Pin

• Equivalent Circuit of SDA Pin

• Equivalent Circuit of VrefU1, VrefU2, VrefL1, VrefL2 and AO1 to 12 Pins

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                   |            | SYMBOL          | LIMITS                        | UNIT |

|-----------------------------|------------|-----------------|-------------------------------|------|

| Digital Supply Voltage      |            | V <sub>DD</sub> | -0.3 to +7.0                  | V    |

| Analog Supply Voltage       |            | Vcc             | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Vcc Side Reference Vo       | ltage      | VrefU1, U2      | -0.3 to Vcc + 0.3             | V    |

| GND Side Reference Voltage  |            | VrefL1, L2      | -0.3 to Vcc + 0.3             | V    |

| Digital Input Voltage       |            | Vin             | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output Voltage              |            | Vouт            | -0.3 to Vcc + 0.3             | V    |

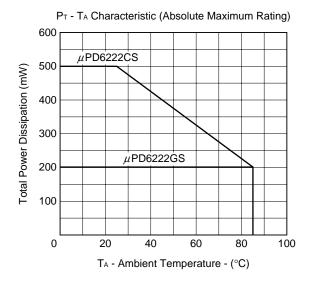

| Power Dissipation           | CS Package | PD              | 500                           | mW   |

| GS Package                  |            |                 | 200                           | mW   |

| Operating Temperature Range |            | TA              | –20 to +85                    | °C   |

| Storage Temperature R       | ange       | Tstg            | -55 to +125                   | °C   |

#### RECOMMENDED OPERATION CONDITIONS

| PARAMETER                                            | SYMBOL          | CONDITION                                                       | MIN.  | TYP. | MAX.  | UNIT |

|------------------------------------------------------|-----------------|-----------------------------------------------------------------|-------|------|-------|------|

| Digital Supply Voltage                               | V <sub>DD</sub> | VDD = VCC                                                       | 4.5   | 5.0  | 5.5   | V    |

| Analog Supply Voltage                                | Vcc             |                                                                 |       |      |       |      |

| Input Voltage of Vcc Side<br>Reference Voltage Range | VrefU1, U2      | This parameter is not same as D/A output voltage. D/A output is | VrefL |      | Vcc   | V    |

| Input Voltage of GND Side<br>Reference Voltage Range | VrefL1, L2      | defined by the ability of Output Buffer Amp.                    | GND   |      | VrefU | V    |

| Output Capacitance Load                              | Со              |                                                                 |       |      | 0.1   | μF   |

# ELECTRICAL CHARACTERISTICS DIGITAL BLOCK

(Vcc, Vdd, VrefU1, 2 = +4.5 to +5.5 V, VrefU1,  $2 \le Vcc$ , VrefL1, 2 = GND = 0 V, TA = -20 to +85 °C)

| PARAMETER                | SYMBOL  | CONDITION                    | MIN.                | TYP. | MAX.                | UNIT |

|--------------------------|---------|------------------------------|---------------------|------|---------------------|------|

| Digital Supply Current   | lod     | CLK = 1 MHz, IAO = 0 $\mu$ A |                     |      | 1.0                 | mA   |

| Input Leak Current       | II LEAK | Vin = 0 to VDD               | -10                 |      | 10                  | μΑ   |

| Low-Level Input Voltage  | VIL     |                              |                     |      | 0.2 V <sub>DD</sub> | V    |

| High-Level Input Voltage | Vih     |                              | 0.8 V <sub>DD</sub> |      |                     | V    |

ANALOG BLOCK (Vcc, VDD, VrefU1, 2 = +4.5 to +5.5 V, VrefU1, 2  $\leq$  Vcc, VrefL1, 2 = GND = 0 V, TA = -20 to +85  $^{\circ}$ C)

| PARAMETER                                      | SYMBOL          | CONDITION                                                                 | MIN. | TYP. | MAX.      | UNIT |

|------------------------------------------------|-----------------|---------------------------------------------------------------------------|------|------|-----------|------|

| Analog Supply Current                          | Icc             | CLK = 1 MHz, IAO = 0 $\mu$ A                                              |      | 1.0  | 4.8       | mA   |

| Input Current of Vcc Side<br>Reference Voltage | IrefU           | $V_{ref}U = 5 \text{ V},$ $V_{ref}L = 0 \text{ V},$ Data: Maximum Current |      | 1.2  | 3.0       | mA   |

| Output Voltage Range of                        | Vao             | I <sub>AO</sub> = ±100 μA                                                 | 0.1  |      | Vcc - 0.1 | V    |

| Output Buffer Amp.                             |                 | I <sub>AO</sub> = ±500 μA                                                 | 0.2  |      | Vcc - 0.2 |      |

| Output Current of Output                       | IAO             | Vao = 4.7 V                                                               |      |      | -1.0      | mA   |

| Buffer Amp.                                    |                 | Vao = 0.2 V                                                               | +1.0 |      |           |      |

| Differential Nonlinearity                      | N <sub>DL</sub> | V <sub>ref</sub> U = 4.79 V                                               |      |      | ±0.8      | LSB  |

| Nonlinearity                                   | NL              | V <sub>ref</sub> L = 0.95 V<br>Vcc = 5.5 V (15 mV/LSB)                    |      |      | ±0.8      | LSB  |

| Zero Scale Error                               | Nz              | No Load (IAO = 0 A)                                                       |      |      | ±1.2      | LSB  |

| Full Scale Error                               | NF              |                                                                           |      |      | ±1.2      | LSB  |

| Error between each Channel                     | Nch             |                                                                           |      |      | ±1.2      | LSB  |

| Output Impedance of Output Buffer Amp.         | Ro              |                                                                           |      | 5.0  |           | Ω    |

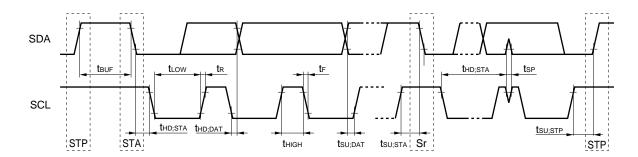

#### I<sup>2</sup>C-BUS TRANSFER STANDARD

| PARAMETER                                                                        | SYMBOL  | MIN.              | MAX. | UNIT |

|----------------------------------------------------------------------------------|---------|-------------------|------|------|

| SCL clock frequency                                                              | fscL    | 0                 | 100  | kHz  |

| Time the bus must be free before a new transmission can start                    | tвиғ    | 4.7               | -    | μs   |

| Hold time START condition. After this period, the first clock pulse is generated | thd;sta | 4.0               | _    | μs   |

| LOW period of the clock                                                          | tLOW    | 4.7               | _    | μs   |

| HIGH period of the clock                                                         | tнісн   | 4.0               | -    | μs   |

| Set-up time for START condition (Only relevant for a repeated START condition)   | tsu;sta | 4.7               | _    | μs   |

| Hold time DATA for I <sup>2</sup> C ICs                                          | thd;dat | O <sup>Note</sup> | -    | ns   |

| Set-up time DATA                                                                 | tsu;dat | 250               | -    | ns   |

| Rise time of both SDA and SCL lines                                              | tr      | _                 | 1    | μs   |

| Fall time of both SDA and SCL lines                                              | tr      | _                 | 300  | ns   |

| Set-up time for STOP condition                                                   | tsu;stp | 4.0               | _    | μs   |

**Note** Note that a transmitter must internally provide at least a hold time to bridge the undefined region (max. 300 ns) of the falling edge of SCL.

#### Timing requirements for the I<sup>2</sup>C-bus

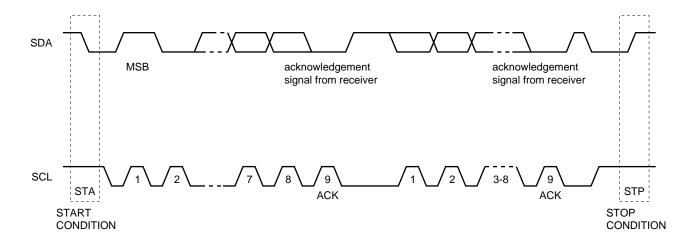

#### I<sup>2</sup>C-BUS FORMAT

| STA | SLAVE ADDRESS DATA | W | ACK | SUB ADDRESS DATA | ACK | D/A DATA | ACK | STP | 1 |

|-----|--------------------|---|-----|------------------|-----|----------|-----|-----|---|

|-----|--------------------|---|-----|------------------|-----|----------|-----|-----|---|

• STA: START condition

• W : This bit is a data-transfer direction bit. A 'Zero' (LOW) is set at sending a data from master to slave.

• ACK: This is an acknowledge bit. The receiver responses a 'Zero' (LOW) to the transmitter when the receiver acknowledges data reception.

• STP: STOP condition

#### **DIGITAL DATA FORMAT**

• SLAVE ADDRESS DATA

| First |   |   |   |      |        | Last |

|-------|---|---|---|------|--------|------|

| MSB   |   |   |   |      |        | LSB  |

| 1     | 0 | 0 | 1 | A2   | A1     | A0   |

|       |   |   |   | Chip | Select | Data |

Chip Select Data

MSB LSB

| A2 | A1 | Α0 | CS2 | CS1 | CS0 |

|----|----|----|-----|-----|-----|

| 0  | 0  | 0  | 0   | 0   | 0   |

| 0  | 0  | 1  | 0   | 0   | 1   |

| 0  | 1  | 0  | 0   | 1   | 0   |

| :  | :  | ÷  | :   | :   | :   |

| 1  | 1  | 1  | 1   | 1   | 1   |

This chip will be selected only when A0, A1 and A2 are equal to CS0, CS1 and CS2.

SUB ADDRESS DATA

| First |       |      |   |      |       |         | Last |

|-------|-------|------|---|------|-------|---------|------|

| MSB   |       |      |   |      |       |         | LSB  |

| ×     | ×     | ×    | × | S3   | S2    | S1      | S0   |

|       | Don't | care |   | Char | nel S | elect l | Data |

Channel Select Data

MSB LSB

| S3 | S2 | S1 | S0 | Channel Select          |

|----|----|----|----|-------------------------|

| 0  | 0  | 0  | 0  | Don't care              |

| 0  | 0  | 0  | 1  | ch1                     |

| 0  | 0  | 1  | 0  | ch2                     |

| :  | :  | i  | :  | :                       |

| 1  | 0  | 1  | 1  | ch11                    |

| 1  | 1  | 0  | 0  | ch12                    |

| 1  | 1  | 0  | 1  | Don't care              |

| 1  | 1  | 1  | 0  |                         |

| 1  | 1  | 1  | 1  | Inhibit <sup>Note</sup> |

Note Internally Test Mode

• D/A DATA

| First |    |    |    |    |    |    | Last |

|-------|----|----|----|----|----|----|------|

| MSB   |    |    |    |    |    |    | LSB  |

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0   |

D/A Output Data

| First | Last |

|-------|------|

| MSB   | LSB  |

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | D/A OUTPUT                                          |

|----|----|----|----|----|----|----|----|-----------------------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | $(V_{ref}U - V_{ref}L) / 256 \times 1 + V_{ref}L$   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | $(V_{ref}U - V_{ref}L) / 256 \times 2 + V_{ref}L$   |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | $(V_{ref}U - V_{ref}L) / 256 \times 3 + V_{ref}L$   |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | $(V_{ref}U - V_{ref}L) / 256 \times 4 + V_{ref}L$   |

| :  | :  |    | :  | :  | :  | :  | :  | :                                                   |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | $(V_{ref}U - V_{ref}L) / 256 \times 255 + V_{ref}L$ |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | VrefU                                               |

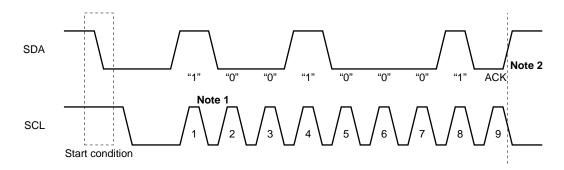

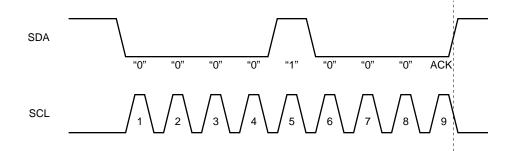

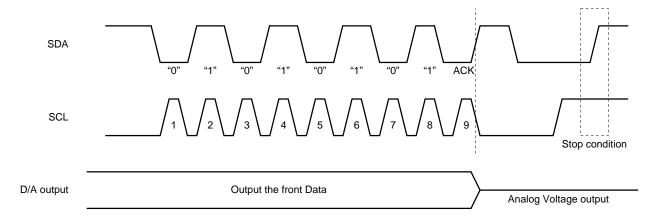

#### DATA TRANSFER ON THE I2C-BUS

#### I<sup>2</sup>C BUS ACCESS

Data example; (CS2, CS1, CS0) = (A2, A1, A0) = (0, 0, 1)(S3, S2, S1, S0) = (0, 1, 0, 0) Select output 4ch Digital Data = (0, 1, 0, 1, 0, 1, 0, 1)

#### **SLAVE ADDRESS DATA BLOCK**

#### SUB ADDRESS DATA BLOCK

#### D/A DATA BLOCK

Notes 1. The timing of reading data in SDA is the falling edge of SCL.

2. The acknowledgement signal is output from SDA in fall-timing of SCL8, and releases SDA line in the fall-timing of SCL9.

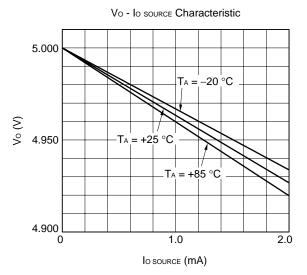

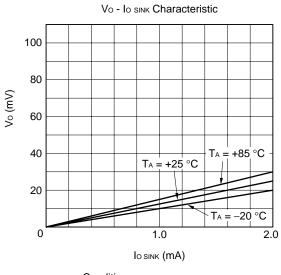

#### CHARACTERISTICS CURVES (TYP.)

Condition:  $Vcc = V_{ref}U = +5.0 V$   $V_{ref}L = 0 V$ Non Load

Condition:  $Vcc = V_{ref}U = +5.0 \text{ V}$   $V_{ref}L = 0 \text{ V}$ Non Load

Condition: Vcc = +5.5 V  $V_{ref}U = +4.79 \text{ V}$   $V_{ref}L = +0.95 \text{ V (15 mV/LSB)}$  Non Load

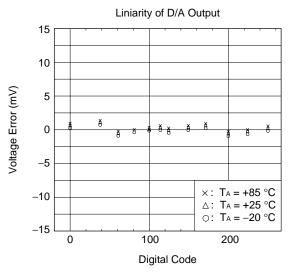

#### **APPLICATION EXAMPLE**

#### NOTE FOR USE

#### ABOUT INPUT VOLTAGE

This IC's Vdd, Vcc, VrefU1, VrefU2, VrefL1, VrefL2 pins must be supplied the stable voltage. When the voltage-level of these pins are added any noise signal, the analog accuracy of output voltage may be influenced by any noise signal.

Therefore, the bypass condenser is connected between these pins and GND pins for keeping the analog accuracy. And it's necessary that the bypass condenser is near IC.

#### • HANDLING RELATED TO THE UNUSED PINS

The output pins have a possibility of being unused pins. If there are unused pins, they must not be connected.

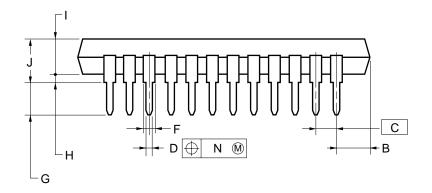

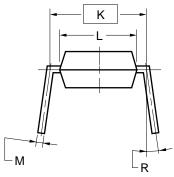

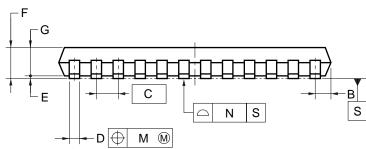

# 24PIN PLASTIC SHRINK DIP (300 mil)

#### **NOTES**

- Each lead centerline is located within 0.17 mm (0.007 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| Α    | 25.40 MAX.             | 1.000 MAX.                |

| В    | 3.0 MAX.               | 0.119 MAX.                |

| С    | 1.778 (T.P.)           | 0.070 (T.P.)              |

| D    | 0.50±0.10              | $0.020^{+0.004}_{-0.005}$ |

| F    | 0.85 MIN.              | 0.033 MIN.                |

| G    | 3.5±0.3                | 0.138±0.012               |

| Н    | 0.51 MIN.              | 0.020 MIN.                |

| 1    | 4.31 MAX.              | 0.170 MAX.                |

| J    | 5.08 MAX.              | 0.200 MAX.                |

| K    | 7.62 (T.P.)            | 0.300 (T.P.)              |

| L    | 6.4                    | 0.252                     |

| М    | $0.25^{+0.10}_{-0.05}$ | $0.010^{+0.004}_{-0.003}$ |

| N    | 0.17                   | 0.007                     |

| R    | 0~15                   | 0~15                      |

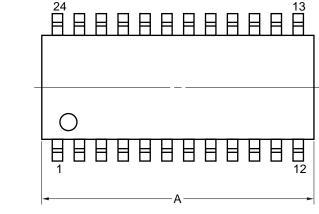

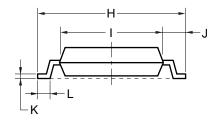

# 24 PIN PLASTIC SOP (300 mil)

detail of lead end

#### NOTE

- 1. Controlling dimension millimeter.

- 2. Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS                            | INCHES                    |

|------|----------------------------------------|---------------------------|

| Α    | 15.3±0.24                              | 0.602±0.010               |

| В    | 0.78 MAX.                              | 0.031 MAX.                |

| С    | 1.27 (T.P.)                            | 0.050 (T.P.)              |

| D    | $0.40^{+0.10}_{-0.05}$                 | $0.016^{+0.004}_{-0.003}$ |

| Е    | 0.1±0.1                                | 0.004±0.004               |

| F    | 1.8 MAX.                               | 0.071 MAX.                |

| G    | 1.55±0.05                              | 0.061±0.002               |

| Н    | 7.7±0.3                                | 0.303±0.012               |

| 1    | 5.6±0.15                               | $0.220^{+0.007}_{-0.006}$ |

| J    | 1.05±0.2                               | 0.041+0.009               |

| K    | 0.22 <sup>+0.08</sup> <sub>-0.07</sub> | $0.009^{+0.003}_{-0.004}$ |

| L    | 0.6±0.2                                | 0.024+0.008               |

| М    | 0.12                                   | 0.005                     |

| N    | 0.10                                   | 0.004                     |

| Р    | 3°+7°                                  | 3°+7°                     |

P24GM-50-300B-5

#### RECOMMENDED SOLDERING CONDITIONS

The following conditions (see tables below) must be met when soldering this product.

Please consult with our sales offices in case other soldering process is used, or in case other soldering is done under different conditions.

#### TYPES OF SURFACE MOUNT DEVICE

For more details, refer to our document "SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL" (IEI-1207).

#### [μ**PD6222GS**]

| Soldering method       | Soldering conditions                                                                                                                                                               | Recommended condition symbol |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Infrared ray reflow    | Peak package's surface temperature: 235 °C or below,<br>Reflow time: 30 seconds or below (210 °C or higher),<br>Number of reflow process: 3, Exposure limit <sup>Note</sup> : None | IR35-00-3                    |

| VPS                    | Peak package's surface temperature: 215 °C or below,<br>Reflow time: 40 seconds or below (200 °C or higher),<br>Number of reflow process: 2, Exposure limit <sup>Note</sup> : None | VP15-00-2                    |

| Wave soldering         | Solder temperature: 260 °C or below, Flow time: 10 seconds or below, Number of flow process: 1, Exposure limit Note: None                                                          | WS60-00-1                    |

| Partial heating method | Terminal temperature: 300 °C or below, Flow time: 3 seconds or below, Exposure limit <sup>Note</sup> : None                                                                        |                              |

Note Exposure limit before soldering after dry-pack package is opened.

Storage conditions: 25 °C and relative humidity at 65 % or less.

Caution Do not apply more than a single process at once, except for "Partial heating method".

#### TYPES OF THROUGH HOLE DEVICE

#### [µPD6222CS]

| Soldering method | Soldering conditions                                                   | Recommended condition symbol |

|------------------|------------------------------------------------------------------------|------------------------------|

| Wave soldering   | Solder temperature: 260 °C or below,<br>Flow time: 10 seconds or below |                              |

#### **REFERENCE**

| Document Name                                               | Document No. |

|-------------------------------------------------------------|--------------|

| NEC semiconductor device reliability/quality control system | IEI-1212     |

| Quality grade on NEC semiconductor devices                  | C11531E      |

| Semiconductor device mounting technology manual             | C10535E      |

| NEC IC Package Manual (CD-ROM)                              | C13388E      |

| Guide to quality assurance for semiconductor devices        | MEI-1202     |

| Semiconductor selection guide                               | X10679E      |

[MEMO]

#### -NOTES FOR CMOS DEVICES -

## (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR MOS DEVICES

Note: No connection for MOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. MOS device behaves differently than Bipolar device. Input levels of MOS device must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

[MEMO]

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5